MOS管米勒效应的罪魁祸首--Cgd

作者:硬件微讲堂

谈到MOS管的米勒效应,肯定绕不开栅-漏极电容Cgd的影响。这里面涉及一个重要计算,今天和大家一起讨论下。

1、一道问题

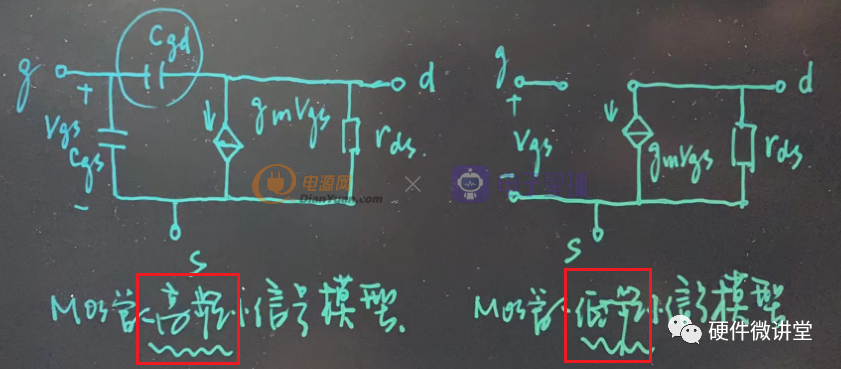

照例,先抛出一个问题:在MOS管的等效电路中,栅-漏电容Cgd等效到输入回路中的容值是多少?推导过程是怎样的?

这道题的难点在于推导过程,这需要同学们理解,而不是死记硬背。

2、等效电路

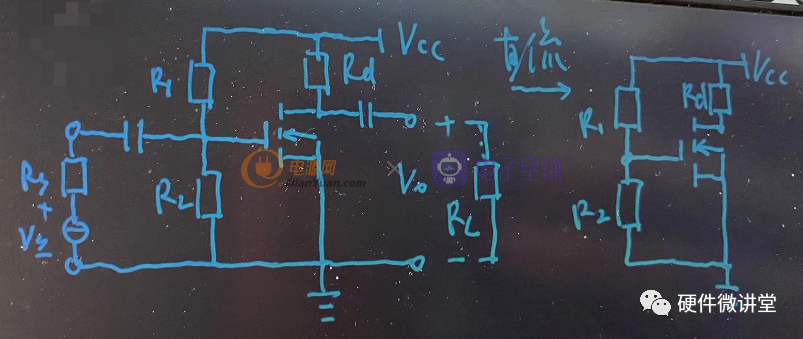

为便于理解,我们以带有栅极偏置的共源极放大电路作为分析对象。如下图所示,首先画图其直流通路,比较简单,这里我们不做过多分析。

接着,我们画出其交流通路。注意,这里我们使用的不是MOS管的低频小信号模型,而是高频小信号模型。

因为在低频模式下,我们是通常是忽略结电容的影响。高频模式下,交流通路如下图所示。

可能会有同学问了,这里和三极管的交直流通路很像。对的,确实相似,因为两者存在很多相通性。所以在学校里,很多老师只讲三极管放大电路,MOS管放大电路是自学部分。三极管部分,不清楚的同学可以回看《终于有人把共射放大电路不放大原因说清楚了!》,不做赘述。

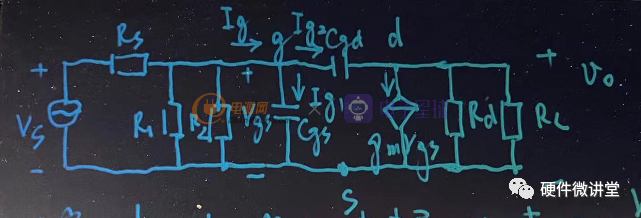

3、以电流为切入点

细心的同学会发现在上图中标注了Ig,Ig1和Ig2,其中Ig1是流过Cgs电容的电流,Ig2为流过Cgd电容的电流,而Ig是Ig1和Ig2的干路总电流,Ig=Ig1+Ig2……【继续阅读】

介绍一种输入阻抗测量方法

作者:小小的电子之路

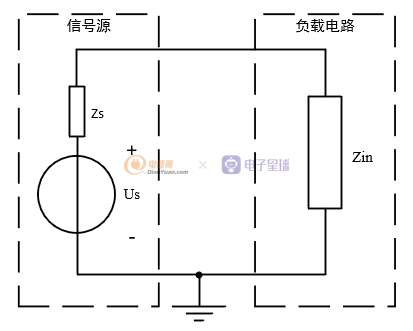

输入阻抗是指从电路的输入端看进去所得到的等效阻抗,它可以反映电路从信号源获取电压或者电流的能力。

1、输入阻抗

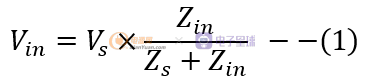

假设一个电路的输入阻抗为Zin,该电路采用电压源供电,实际电压源总存在内阻Zs,因此,整个电路可以简化为下图所示的电路:

根据分压原理,负载电路所获取的电压

可以看出,对于采用电压源驱动的电路,负载电路的输入阻抗越大,其从信号源获取电压的能力越强。因此,一般来说,其输入阻抗越大越好,但是对于电流源驱动的电路则相反。

2、输入阻抗的测量

输入阻抗可以采用分压法来测量,测量步骤如下:

(1)将信号源与待测电路直接连接,如下图所示,记录此时负载电路输入端的电压,记为V1;

(2)在电路中串接阻抗Ze,如下图所示,记录此时负载电路输入端的电压,记为V2;

其中该阻抗由电阻Re与电容Ce组成,其阻抗值可以表示为……【继续阅读】

#征文#天线阻抗匹配再研究

作者:EMC小白

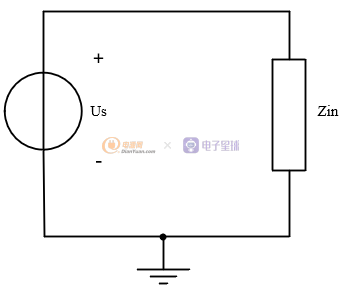

天线的调试目标一般来说都是使得天线的端口阻抗为50ohm,这些都需要用网络分析仪实测得到。

在前文的“天线匹配问题”中谈到过天线的阻抗匹配主要是将天线阻抗匹配等于传输线阻抗。

由于天线阻抗往往不能直接满足传输线的阻抗,因而需要用到匹配网络将其匹配到50欧姆,当天线等效阻抗中有虚部时,还需要匹配网络去除其虚部部分,同时使得等效阻抗等于50欧姆。这儿带来两个问题,阻抗匹配需要实现以下两个目标:1.匹配到传输线阻抗;2.使得天线形成谐振。

一.这儿提出两个问题:1.能不能直接用电阻+去除虚部的方式进行阻抗匹配;2.为什么要让天线形成谐振。

1.能不能直接用电阻+去除虚部的方式进行阻抗匹配

虽然形成了阻抗匹配,后端的等效电路变为电阻+LC谐振,能量将会有一部分在电阻上消耗掉;

2.为什么要让天线形成谐振

形成LC谐振,电感和电容会交替充电和放电,且在没有电阻的情况下,能量能完美的辐射出去。

二.解决了阻抗匹配的问题,还有关于等效阻抗的问题,为什么天线的阻抗匹配没有像前端传输线一样,直接让板厂将天线设计成特性阻抗为50欧姆?那样都不需要阻抗匹配网络了。

那是因为只有传输线才能设计成特性阻抗,我们看下传输线的定义:传输线由两条一定长度导线构成,一条是信号传播途径,一条是返回路径。对待天线构成,我们为了便于天线辐射,对其通常是挖空处理,也就是缺少一个“紧贴”的返回路径,个人理解其返回路径为大地平面。由于天线不是传输线,也就是谈不上特征阻抗设计了,说白了,天线缺少可见的返回路径,不能当作传输线来处理,只能通过等效阻抗来理解天线阻抗。

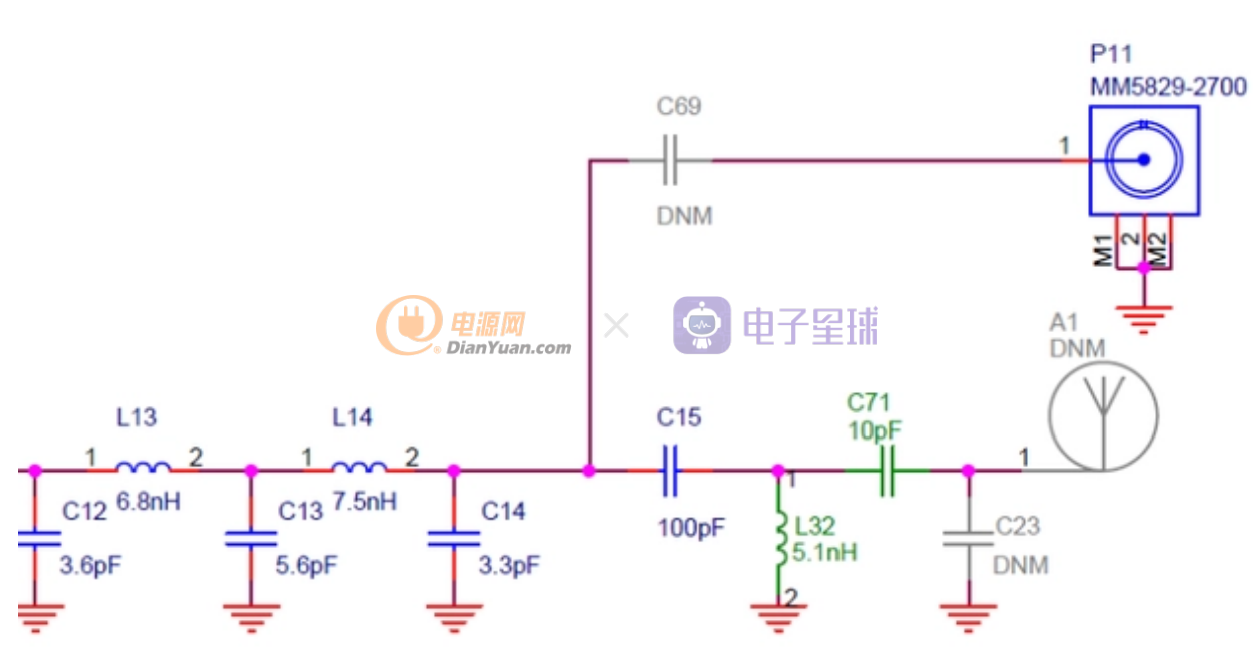

三.一些频率相对较低的走线为什么没有要求做阻抗匹配

信号频率为13.56MHz,黄色馈线部分为匹配网络前端走线,但是对于这段走线,我们并没有按照其他高频信号一样做阻抗控制,这是为什么呢……【继续阅读】

#征文#谈谈对MOS管米勒平台电压的理解

作者:EMC小白

新的一年,祝大伙事业蒸蒸日上,前兔似锦年华。

网上关于MOS管米勒平台的解释很多,今天谈谈自己对此平台的理解,以期给大家不一样的解释感受,若有不足支持,欢迎指出,谢谢。

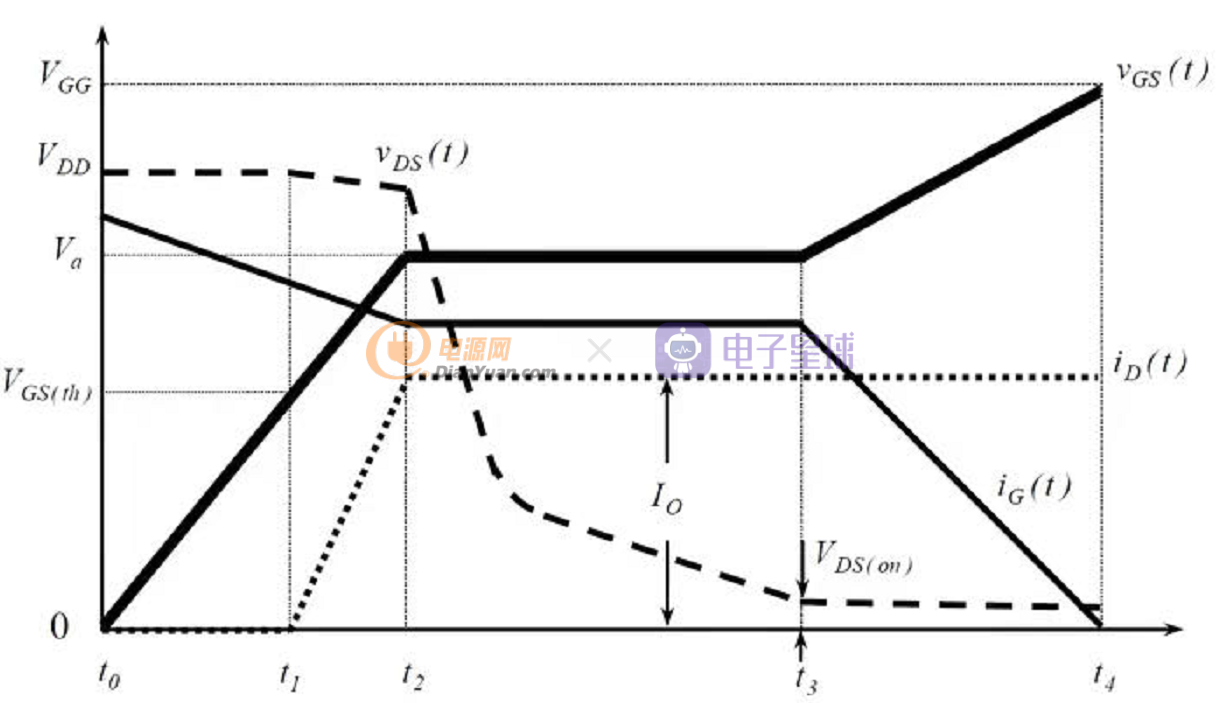

对于MOSFET管,米勒效应(Miller Effect)指其输入输出之间的分布电容(栅漏电容)在反相放大作用下,使得等效输入电容值放大的效应。由于米勒效应,MOSFET栅极驱动过程中,会形成平台电压,引起开关时间变长,开关损耗增加,给MOS管的正常工作带来非常不利的影响。话不多说,直接上图:

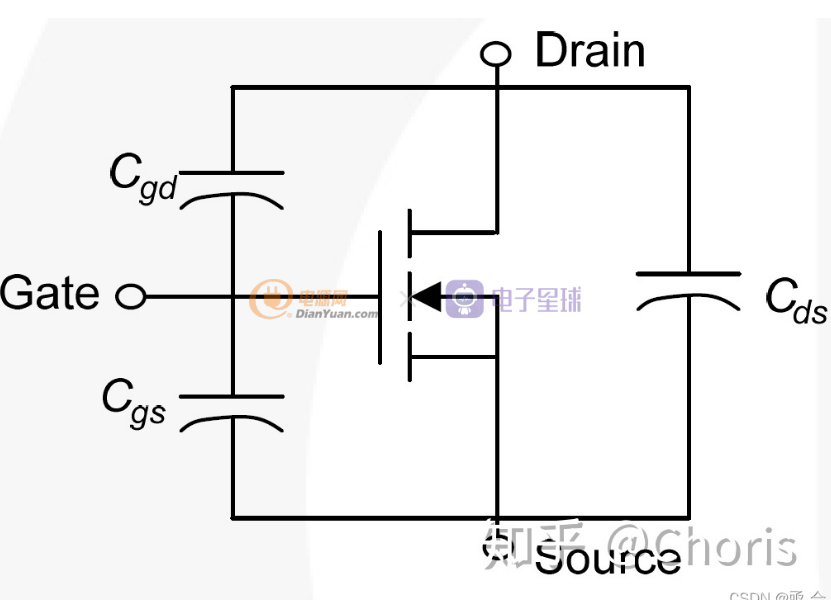

米勒平台指的是在t2到t3这段时间内,Vds的电压持续下降,但是未达到t3时刻的可变电阻区,id达到最大值,而Vgs此时基本维持不变,我们知道要让MOS管达到可变电阻区的条件是,Vgs-Vth>Vds,只有当Vgs足够大,Vds足够小,从图中可以看出在t3后期阶段,更容易达到可变电阻区。我们回到米勒平台电压的问题,在该阶段,明明给栅极电压充电了,但为什么会出Vgs电压值基本不变呢(以NMOS管为例),我们观察下MOS管的寄生参数模型:

可以看到存在Cgs,Cgd,Cds寄生电容,在t0到t2时间段,Vgs持续上升,Vds持续下降,注意观察在t2时刻左右,米勒平台出现,此时出现Vds和Vgs的交点,在这拐点之后,Vgs值大于Vds的值,即从此刻开始,栅极电压大于漏极电压,也就是说从此刻开始,给栅极端充电的电荷会有一部分转移到漏极(电容电压由高处流向低处),但为什么会出现Vgs的电压基本不变,可以这样理解,如果说后端负载不变,那么给栅极电容充满电后,栅极电荷会转移一部分到漏极,只要栅极电压比漏极高,电荷就会持续不断的转向漏极,同时Vgs端的电压和Vds端的电压也会持续上升,只有当后端负载持续增加,从曲线上看就是Vds端的电压持续下降,可以理解成前端电荷无法满足后端负载的需求,导致负载端电压被拉低,回到MOS管上,此时的情况应该是给栅极充电的电荷,由于Vds的压降持续下降,新增加的电荷基本都用来供给Vds(只是还是无法保证Vds电压上升而已),而Vgs由于无新增加的电荷,从而导致Vgs的电压基本维持不变。

在t3点时刻以后,当出现Vgs-Vth>Vds时,MOS管进入可变电阻区,Vds达到了极限电压状态,跟内部的Rdson有关,此时由于Vds压降不再下降,给栅极充电的电荷已经给栅极充电(栅极充电的电荷此时也应该给漏极再充电,由于漏极不再持续下降,也就是此时的电荷需求没有之前那么大了,栅极可以存储一部分的电荷),栅极电压进而可以持续上升,一直达到给栅极充电的电压幅值,一直达到t4阶段……【继续阅读】