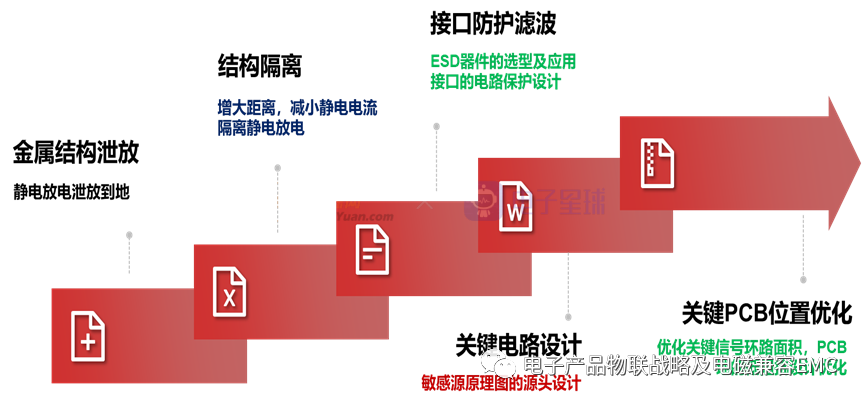

ESD静电放电的故障诊断与整改-常用的思路与方法如下:

(1)通常检查电缆的屏蔽层与外壳或壳体是否搭接良好,理想情况下,它应与壳体的屏蔽层进行3600的搭接。

(2)确保所有I/O连接器的外壳与EUT的壳体进行3600的搭接。

(3)壳体和屏蔽层要互相搭接好。确定所有紧固件都紧固好。

(4)确保机箱上搭接处的涂层不会产生阻抗,否则会引起交叉耦合能量和泄漏。

(5)找到一个与连接器连接的电缆屏蔽层然后与电路板相连,这样可用于泄放电流路径。这时就会将ESD电荷引至电路板的信号返回平面。如果这个电荷不受控制,就会出现问题。假如存在独立的外壳平面,或者如果外壳平面的某一区域专门用作地平面,将是一个好的参考点。

(6)孔缝、指示器,以及外壳上会形成开口和可能暴露电子器件的任何部件,都必须具有能对ESD进行泄流和安全转移的导电路径。

在理想情况下,所有的I/O端口及直流或交流电源,都应进行合适的滤波。这包括让滤波器的位置尽可能地接近连接器。对于I/O端口比如USB、以太网接口通常应使用为其设计的共模扼流圈,瞬态防护器件或滤波器可解决出现的任何问题。否则,I/O电缆或电源线电缆能将所产生的ESD电流完全传输进电路。

注意:当采用滤波器件旁路这种电流时,引线的长度将增加电感,从而降低滤波器件的有效性。从滤波器的电容器件到外壳的泄流路径,应非常接近电容器件,泄流路径阻抗要低甚至为平面以减小电感。

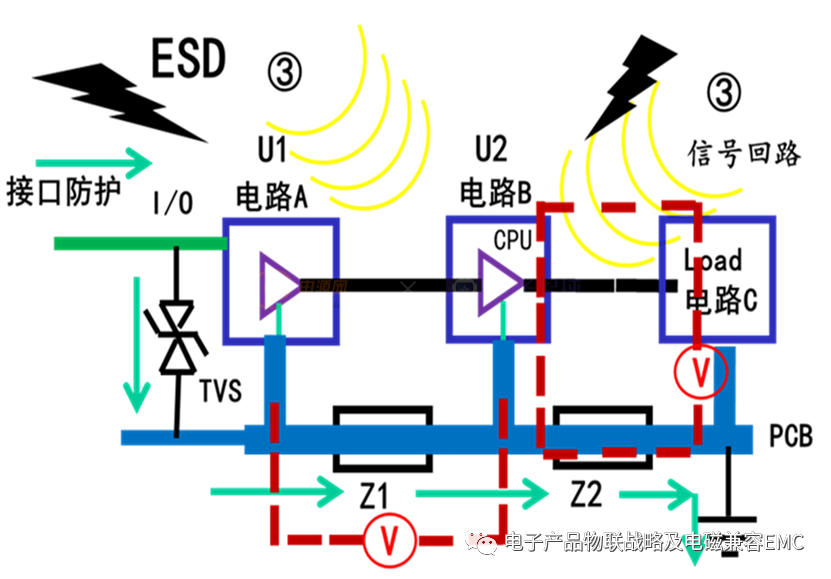

当ESD电流在PCB走线上流动时,他们能产生显著的电场和磁场。这些电磁场能耦合进敏感电路,使其受到干扰。同时,由于导体的阻抗特性,这些电流能在平面上或PCB走线上建立电压梯度。如果电路或元器件以此平面作为参考且承受着从平面的一端到另外一端的电压梯度,那么他们会受到干扰。这种效应有时被称为地弹。

一旦ESD进入到电路板上,再要对其进行控制则是比较困难的。最佳的方法是确保所有元器件和电路的电位能随着电压脉冲同时上升和下降。然而,由于这些脉冲具有非常高速的性质,因此在不同电路的PCB走线和平面上脉冲的时序可能不同。除此之外,PCB走线和导体的阻抗上也会产生电压降,因此,让所有元器件具有相同电压上升幅度是无法实现的。

ESD产生的总功率和电流通常情况下是相当小的。滤波器通常可使用额定电压为100V的标准电容器。TVS二极管可用于限制电路或平面之间产生的电压。

当进行故障诊断时,先使用低的ESD电压,比如500V或1000V。施加脉冲给任何孔缝,或者人可以触摸到的裸露金属。这就包括所有屏蔽的I/O连接器的导电外壳。当产品没有问题时,可以以500V的步进增加ESD模拟器的电压直到规定的限值。通常好的做法是,让测试电压超过规定限值以确定裕量。

如果敏感点或故障点为连接器的外壳,这时推荐以下故障诊断及优化方法:

(1)确保其与金属壳体进行了好的搭接。

(2)检查可能会在连接器外壳和产品外壳之间产生阻抗的涂层或喷涂。

(3)确保连接器的外壳都是紧固的,各组件之间具有低阻抗的路径。

(4)确保产品外壳与保护地或ESD发生器的返回路径进行了正确的连接。

如果怀疑是电缆把ESD电流耦合给了产品及电路,这时推荐的故障诊断方法:

(1)尽可能在接近产品连接器的电缆上加装铁氧体共模扼流圈。

(2)在任何可疑的输入或输出端口处设计简单的低通RC滤波器,串联电阻的典型值为47~100Ω,与信号或电源返回路径之间的典型电容值为1~10nF。

(3)I/O接口线上设计共模扼流圈。

(4)数据线上设计TVS器件。TVS设计注意其选型设计规则和方法。

(5)确保所有的壳体紧固件都是紧固的。

(6)可使用铜带密封可疑的缝隙。

(7)在泄漏缝隙和内部电路电子元器件之间增加附加的隔离。

(8)在泄漏缝隙和内部电路之间增加内部屏蔽体,并将其与外壳地进行直接连接。

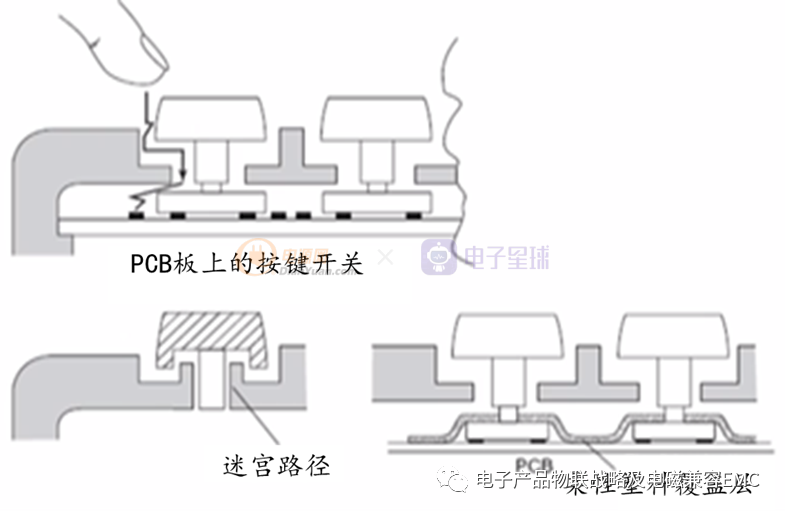

如果ESD通过键盘和按键进入,这时推荐的方法:

(1)在按键和键盘的PCB之间增加内部屏蔽体并将其与外壳地进行直接连接。

(2)在结构上设计的ESD静电放电的防护处理如下图所示。

图中为按键在结构上的ESD设计示意图。

注意:当静电放电ESD干扰信号通过耦合方式到达电路板内部的时候,如下图所示:

注意:PCB的设计地走线,地回路,接地点的位置设计也是解决抗扰度ESD设计最关键的设计方法与思路。

目前行业内最典型的EMS敏感度的设计也都跟这个结构图相关联。

产品问题的发生也是跟我们产品设计可靠性相关联的

更多的电子产品电路可靠性设计系列,会逐渐为大家解开这些设计方面的坑,让电子设计工程师少走弯路,敬请关注!