我现在做了一款54V升400V的移相全桥电路,输入电压为50A,主电路选用移相全桥,功率管选用STW120NF10(120A/100V,Rds为9m欧),现在一共使用了8个MOSFET,采用的两个管子并联的方式.主变压器选用EE55磁性两幅.变压器匝数比为2:23.开关频率66KHz.

现在的问题是:

MOSFET上的关断剑锋比较高,Vpeak大约为90V,如在每个MOSFET0.04uF左右的电容,Vpeak大约在71V左右.但是开关管比较热.

请教一下各位大侠:MOSFET管的DS上并联电容与效率有关系?

我的理解:不并电容,MOSFET的关断损耗比较大?并电容,MOSFET的开通损耗会比较大,但是那一种会占主要的呢?谢谢!

MOSFET管的DS上并联电容与效率有关系吗?

全部回复(28)

正序查看

倒序查看

现在还没有回复呢,说说你的想法

@yuanwen

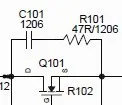

什么去磁绕组?能够说明白一点,谢谢! 我采用就是一个很普通的移相全桥电路,控制芯片采用的是UCC3995,由于输入电压很低且输入电流很大,故没有增加谐振电感,其变压器的漏感足以满足MOSFET中DS上节电容与并联电容谐振的需要.我还采用的是两个MOSFET并联的方式,以降低功率管的导通损耗.但效率也不是很高,只有89%左右.其实我在滞后臂也采用了RCD吸收,因为剑锋快100V了,增加RCD变为了72V左右.增加后感觉软开关不象软开关,有些不伦不类的感觉.

增加电容肯定可以减少PEAK Voltage,但是问题是效率会降低一点点.而且,电容容量不可太大.去磁绕组不可行的.

0

回复

提示

我以前做24V升360V移项全桥也出现过这种情况。当时用的是IR的一种管子,三只并的。我觉得你现在的关键问题不是怎么去吸收这个尖峰,而是降下来。尖峰大关断损耗大。因为你现在是移相全桥,是软开启的,也就是说没有开启损耗的,可以并联电容去吸收损耗。而并联电容还有一个好处就是可以减小关断损耗。也是就关断时延长了电压上升的时间的,而电流下降的时间没有变,电流电压的交点变低,损耗也会变小。但是,由于你这个地方的输入电流很大,并联电容后,由于电容ESR的存在,电容上也会消耗功率,电容会很热,甚至裂开。我当时就出现过这种情况。

我觉得你可以考虑看一下你的驱动,如果你的驱动电阻小的话,开关速度很快,那么关断的尖峰当然会大,加电容只是不得已而为之的办法,得从根本上解决。一般情况下,MOS的驱动波形从0V上升到10V在500ns附近比较合适,太慢会导致在死区时间内关断不了,造成上下管直通,太快电压尖峰会很高,关断损耗也会很大,因为电流和电压交汇点太高。

在不并电容的情况下将尖峰调到很小,然后并联较小电容去延长电压下降时间,减小关断损耗。我们现在超前臂并联的电容是682,滞后臂是222,24V输入情况下电压尖峰是28V,比较理想,三分之一载时DS间关断时电压升到最高用的时间是600ns。MOS管的型号是IRFB4110,Rg为22欧。

希望能给你点帮助,如果不对的地方请大家轻拍,谢谢!

1

回复

提示

@yuanwen

什么去磁绕组?能够说明白一点,谢谢! 我采用就是一个很普通的移相全桥电路,控制芯片采用的是UCC3995,由于输入电压很低且输入电流很大,故没有增加谐振电感,其变压器的漏感足以满足MOSFET中DS上节电容与并联电容谐振的需要.我还采用的是两个MOSFET并联的方式,以降低功率管的导通损耗.但效率也不是很高,只有89%左右.其实我在滞后臂也采用了RCD吸收,因为剑锋快100V了,增加RCD变为了72V左右.增加后感觉软开关不象软开关,有些不伦不类的感觉.

没有做过升压的,不过我们以前的移相全桥都有谐振电感的,开关没有并电容,用的RD吸收

0

回复

提示