### AC/DC Drivers

# AC/DC controller IC for LED lighting Included 650V MOSFET

BM520Q2XF Series (In Developing)

### Description

BM520Q2xF is AC/DC converter with a built in FET which has a 650V withstand voltage for LED lighting. This IC is suitable for a Quasi-resonant switching typed High Side LED driver application, it can achieve a high accuracy of the LED current, and a low EMI at once. In addition, by embedding a PFC (Power Factor Correction) converter, it provides a countermeasure for harmonics.

Moreover, owing to the built-in bootstrap circuit with 650V withstand voltage, the low-power can be achieved. And owing to the external resistance for sensing the switching current, you may design the power supply with a high degree of freedom.

By the built-in bootstrap circuit and MOSFET, a compact application board with only a few components can be designed easily. So this IC is also suitable for a low cost strategy.

### Key Specifications

Operating Power Supply Voltage Range:

VCC 8.9V to 26.0V DRAIN:~650V

Operating Current: Normal:

(BM520Q25F): 0.60mA (Typ.)

(BM520Q29F): 0.50mA (Typ.)

- Operating temperature range: 40deg. to +105deg.

MOSFET ON resistance: BM520Q25F : 4.0Ω (Typ.)

- BM520Q29F : 8.5Ω (Typ.)

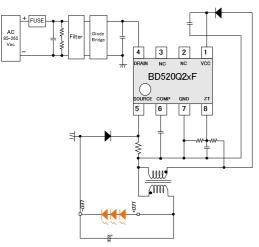

### Application Circuit

Figure 1. Application Circuit

### Features

- Quasi-resonant switching mode + PFC

- Built-in 650V bootstrap circuit

- Built-in 650V switching MOSFET

- Maximum frequency 150kHz

- VCC pin: under voltage protection

- VCC pin: over voltage protection (latch)

- SOURCE pin: Leading-Edge-Blanking function

- LED over current detection

- ZT pin: trigger mask function

- ZT pin: over voltage protection (latch)

- FET over current protection

- AC revision function for LED current detection

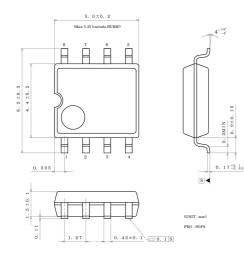

### Package

4.90mm×3.90mm pitch 1.27mm p.) (Typ.) (Typ.)

### Application

LED bulb, seal typed LED lighting Electrical machineries for LED lighting

### Lineup

| Part Number | MOSFET ON Resistance |

|-------------|----------------------|

| BM520Q25F   | 4.0Ω                 |

| BM520Q29F   | 8.5Ω                 |

OProduct structure : Silicon monolithic integrated circuit OThis product has no designed protection against radioactive rays.

# ●Absolute Maximum Ratings (Ta=25℃)

| ltem                         | Symbol          | Rating     | Unit | Condition                                          |

|------------------------------|-----------------|------------|------|----------------------------------------------------|

| Input voltage range 1        | Vmax1           | -0.3~30    | V    | VCC                                                |

| Input voltage range 2        | Vmax2           | -0.3~6.5   | V    | SOURCE, COMP, ZT                                   |

| Input voltage range 3        | Vmax3           | 650        | V    | DRAIN                                              |

| Drain current pluse          | I <sub>DP</sub> | 2.60       | А    | P <sub>w</sub> =10us, Duty cycle=1%<br>(BM520Q25F) |

| Drain current pluse          | I <sub>DP</sub> | 1.30       | А    | P <sub>w</sub> =10us, Duty cycle=1%<br>(BM520Q29F) |

| Maximum power dissipation    | Pd              | 563        | mW   |                                                    |

| Operating temperature range  | Topr            | -40 ~ +105 | °C   |                                                    |

| Maximum junction temperature | Tjmax           | 150        | °C   |                                                    |

| Storage temperature range    | Tstr            | -55 ~ +150 | °C   |                                                    |

(Note1) When mounted (on 70 mm x 70 mm, 1.6 mm thick, glass epoxy on single-layer substrate). Reduce to 4.563 mW/°C when Ta = 25°C or above.

# ●Operating Conditions (Ta=25°C)

| Item                  | Symbol             | Rating   | Unit | Condition     |

|-----------------------|--------------------|----------|------|---------------|

| Input voltage range 1 | VCC                | 8.9~26.0 | V    | VCC voltage   |

| Input voltage range 2 | $V_{\text{drain}}$ | ~650     | V    | DRAIN voltage |

# • Electrical Characteristics

IC (Unless otherwise noted, Ta = 25°C, VCC = 15 V)

|                            |                                |       | Specification           |       | Unit     | Condition                                              |  |

|----------------------------|--------------------------------|-------|-------------------------|-------|----------|--------------------------------------------------------|--|

| Item                       | Symbol                         | Min   | Тур                     | Max   | Unit     | Condition                                              |  |

| [Circuit current]          |                                |       |                         |       |          |                                                        |  |

| Circuit current (ON)1      | I <sub>on1</sub>               | 410   | 600                     | 790   | μA       | NTC=2.0V(PULSE operating)                              |  |

|                            | -0N1                           |       |                         |       | <i>µ</i> | BM520Q25F                                              |  |

| Circuit current (ON)2      | $\mathbf{I}_{_{\mathrm{ON2}}}$ | 350   | 500                     | 650   | μA       | COMP=2.0V(PULSE operating)<br>BM520Q29F                |  |

| Circuit current (ON)3      | I <sub>ons</sub>               | -     | 350                     | 450   | μA       | COMP=0V(PULSE OFF)                                     |  |

| [MOSFET block ]            |                                |       |                         |       | •        |                                                        |  |

| Drain-Source voltage       | V <sub>(BR)DDS</sub>           | 650   | _                       | _     | V        | ID=1mA / VGS=0V                                        |  |

| Drain leakage current      | I <sub>DSS</sub>               | _     | -                       | 100   | μA       | VDS=650V / VGS=0V                                      |  |

| ON resistance              | R <sub>ds(on)</sub>            | _     | 4                       | 5.5   | Ω        | ID=0.25A / VGS=10V<br>(BD520Q25F)                      |  |

|                            |                                |       |                         |       |          | ID=0.25A / VGS=10V                                     |  |

| ON resistance              | $R_{_{DS(ON)}}$                | -     | 8.5                     | 12    | Ω        | (BM520Q29F)                                            |  |

| [VH pin bootstrap circuit] |                                |       |                         |       |          | (                                                      |  |

| VH starting current 1      | I <sub>START1</sub>            | 0.4   | 0.7                     | 1     | mA       | VCC= 0V                                                |  |

| VH starting current 2      | I <sub>START2</sub>            | 1     | 3                       | 6     | mA       | VCC=10V                                                |  |

|                            | -START2                        |       | Ŭ                       | •     | 110 1    | VCC UVLO released                                      |  |

| VH OFF current             | I <sub>start3</sub>            | -     | 10                      | 20    | μA       | VH pin sink current                                    |  |

| VH starting current        |                                |       |                         |       |          | -                                                      |  |

| switching voltage          | V <sub>sc</sub>                | 0.6   | 1.6                     | 2.8   | V        | VCC pin                                                |  |

| [VCC pin protection]       |                                |       |                         |       |          |                                                        |  |

| VCC UVLO voltage 1         | V <sub>UVL01</sub>             | 12.5  | 13.5                    | 14.5  | V        | VCC rising up                                          |  |

| VCC UVLO voltage2          | V                              | 7.5   | 8.2                     | 8.9   | V        | VCC falling down                                       |  |

| VCC UVLO ヒステリシス            | V <sub>UVL03</sub>             | -     | 5.3                     | -     | V        | $V_{UVLO3=} V_{UVLO1-} V_{UVLO2}$                      |  |

| VCC OVP hysteresis         | V <sub>ovp1</sub>              | 26    | 27.5                    | 29    | V        | VCC rising up                                          |  |

| VCC OVP release voltage    | V <sub>ovp2</sub>              | 22    | 23.5                    | 25    | V        | VCC falling down                                       |  |

| Latch released VCC voltage | V <sub>LATCH</sub>             | -     | V <sub>UVLO2</sub> -0.5 | -     | V        | VCC falling down                                       |  |

| VCC recharge start voltage | V <sub>CHG1</sub>              | 7.7   | 8.7                     | 9.7   | V        | VCC falling down                                       |  |

| VCC recharge end voltage   | V <sub>CHG2</sub>              | 12    | 13                      | 14    | V        | VCC rising up                                          |  |

| Latch mask time            | T                              | 60    | 100                     | 140   | μs       |                                                        |  |

| [ DC/DC comparator (turn-o |                                |       |                         |       |          |                                                        |  |

| ZT comparator voltage 1    | V <sub>ZT1</sub>               | 60    | 100                     | 140   | mV       | ZT falling down                                        |  |

| ZT comparator voltage 2    | V <sub>ZT2</sub>               | 120   | 200                     | 280   | mV       | ZT rising up                                           |  |

| ZT comparator hysteresis   | V <sub>ZTHYS</sub>             | -     | 100                     | -     | mV       | V <sub>ZTHYS=</sub> V <sub>ZT1-</sub> V <sub>ZT2</sub> |  |

| ZT trigger mask time       | T <sub>ZTMASK</sub>            | _     | 0.6                     | -     | μs       | VZT H->L,<br>for preventing from noise                 |  |

| ZT trigger timeout         | T <sub>ZTOUT</sub>             | 10    | 15                      | 25    | μs       |                                                        |  |

| [ DC/DC comparator(turn-of |                                |       |                         |       |          |                                                        |  |

| Current trigger voltage    | V <sub>cs</sub>                | 1.7   | 1.8                     | 1.9   | V        | SOURCE rising up                                       |  |

| Maximum frequency          | F <sub>sw</sub>                | 135   | 150                     | 165   | KHz      |                                                        |  |

| Leading edge blank time    | T <sub>LEB</sub>               | _     | 0.2                     | _     | μs       |                                                        |  |

| Minimum ON width           | T <sub>min</sub>               | _     | 0.5                     | _     | μs       |                                                        |  |

| Maximum ON width           | T <sub>max</sub>               | 30    | 39                      | 50.7  | μs       |                                                        |  |

| Current detecting          |                                |       |                         |       |          |                                                        |  |

| AC revision factor         | K <sub>cs</sub>                | 12    | 20                      | 28    | mV/us    |                                                        |  |

| COMP sink current          | $\mathbf{I}_{_{Compsi}}$       | 5     | 20                      | 50    |          | COMP=1V, SOURCE=0V                                     |  |

| COMP sou rce surrent       | I <sub>compso</sub>            | -50   | -20                     | -5    |          | COMP=1V, SOURCE=2V                                     |  |

| [DC/DC protection]         | · 1                            |       | •                       |       |          |                                                        |  |

| ZT OVP voltage             | V <sub>ZTL</sub>               | 3.325 | 3.5                     | 3.675 | V        |                                                        |  |

# Pin Configuration

| -   |                           |     |                                                  |          |     |

|-----|---------------------------|-----|--------------------------------------------------|----------|-----|

|     | NO. Pin Name I/O Function |     | Function                                         | ESD 保護系統 |     |

| NO. |                           |     | Function                                         | VCC      | GND |

| 1   | VCC                       | I/O | Power supply pin                                 | -        | 0   |

| 2   | N.C.                      | -   | Non Connection                                   | -        | -   |

| 3   | N.C.                      | -   | Non Connection                                   | -        | -   |

| 4   | DRAIN                     | I/O | MOSFET DRAIN pin                                 | -        | 0   |

| 5   | SOURCE                    | Ι   | MOSFET DRAIN pin<br>Inductor current sensing pin | -        | 0   |

| 6   | COMP                      | I/O | ERROR AMP output pin                             | -        | 0   |

| 7   | GND                       | I/O | GND pin, input pin for feedback signal           | 0        | -   |

| 8   | ZT                        | I   | Zero current detecting pin                       |          | 0   |

Table 1. 入出力 PIN 機能

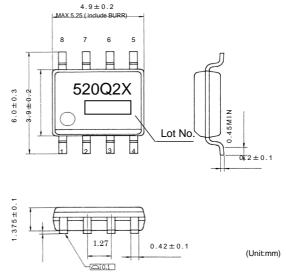

### • External Dimensions

Figure 2 SOP-J8 Package External Dimensions

# •I/O Equivalent Circuit Diagram

Figure 3 I/O Equivalent Circuit Diagram

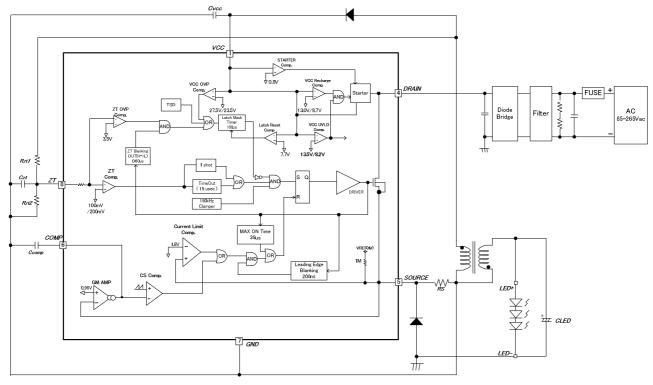

# Block Diagram

Figure 4. Block Diagram

# Block Descriptions

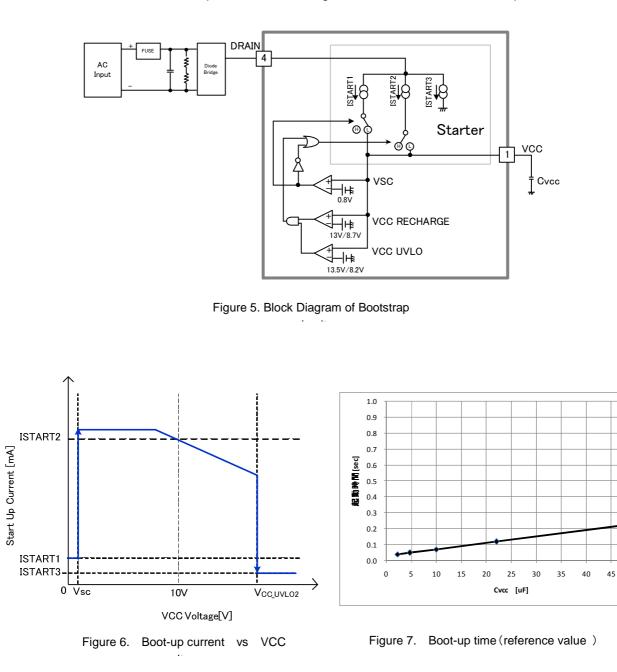

# (1) Bootstrap circuit (DRAIN: 8pin)

A bootstrap circuit with 650V withstand voltage is built in this IC. Owing to this, the low-power standby and high-speed start can be achieved. After the IC was booted up, the power consumption becomes only the idling current (typ=10uA). The reference value of the boot-up time is showed in Figure 7. When Cvcc=10uF, the boot-up time can be less than 0.1s

- \* Boot-up current is the source current form DRAIN pin.

- ex) When Vac=100V, the power consumption of bootstrap circuit is showed below. PVH=100V\* $\sqrt{2}$ \*10uA=1.41mW

- ex) When Vac=240V, the power consumption of bootstrap circuit is showed below. PVH=240V\* $\!\sqrt{2^*10uA}\!=\!\!3.38mW$

50

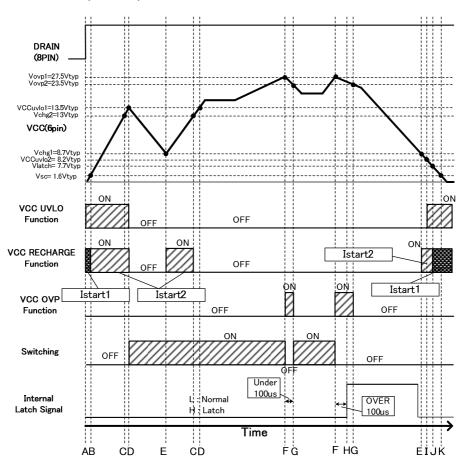

# (2)起動シーケンス

起動シーケンスを Figure 8 に示します。 各々の詳細な説明は、各章で説明します。

# TBD

Figure 8. 起動シーケンス タイムチャート

- A : Input voltage VH is applied.

- B : The IC starts operating when VCC >  $V_{UVLO1}$  (13.5 V Typ).

- Switching function starts when other protection functions are judged as normal. During the time from the IC starts up until the secondary output voltage increases higher than certain voltage, the current consumption of VCC pin causes a drop of VCC voltage. As a result, the VCC should be set to higher than V<sub>UVLO2</sub> (8.2V Typ) until the switching operation starts.

- C : Owing to the soft-start function, over current limit value is restricted to prevent any excessive rise in voltage or current.

- D : When the switching operation starts, VOUT rises.

- Once the output voltage starts, set the rated voltage within the  $T_{FOLP}$  period (32ms Typ).

- E : When there is a light load, it makes FB voltage < V<sub>Bst</sub> (0.40V Typ). In this case, burst operation starts for reducing power consumption. While the burst operation works, the IC is in a low-power consumption mode.

- H : If the VCC voltage becomes lower than  $V_{UVLO2}$  (7.7V Typ), the restart is executed.

- I : The circuit current of IC reduces, and the voltage of VCC pin rises. (same as B)

- J : Same as F.

- K : Same as G.

# (3) VCC pin protection function

The VCC low voltage protection function VCC UVLO (Under Voltage Lock Out), over voltage protection function VCC OVP (Over Voltage Protection), and a VCC recharge function which operates in case of a drop in VCC voltage are built in this IC. The VCC UVLO and VCC OVP functions are used for preventing the destructions of the switching MOSFET which occurs when the VCC voltage is too high or too low.

Owing to the VCC charge function, the VCC pin is charged from high voltage lines by the start circuit when the VCC voltage drops, and the secondary output voltage is stabilized.

### (3-1) VCC UVLO / VCC OVP function

VCC UVLO and VCC OVP are auto recovery comparators which have voltage hysteresis.

VCC OVP operates in case of continuing VCC pin voltage >  $V_{OVP}$  (Typ=27.5V).

VCC OVP has a built-in mask time  $T_{LATCH}(Typ=100us)$ .

When the VCC voltage is over  $V_{\text{OVP}}$  (typ=27.5V) ,and this state lasts  $T_{\text{LATCH}}$  (typ=100us) , the detection is executed. By this function, the surge which occurs at VCC pin can be masked .

### (3-2) VCC charge function

When the VCC pin voltage is over  $V_{UVLO1}$ , the IC starts up. In this case, if the VCC pin voltage drops below  $V_{CHG1}$ , VCC charge function operates. At this time, the VCC pin is charged from the DRAIN pin through the bootstrap circuit. By this operation, the failure of start-up can be prevented.

Figure 9. VCC\_UVLO/ VCC\_OVP / VCC Charge Function Timing Chart

A: DRAIN pin voltage is applied, VCC voltage rises by the charging current Istart1 (700uA typ).

B: VCC voltage> Vsc, the charging current to VCC changes from start1(700uA typ)⇒Istart2(3mA typ)

C: VCC voltage> V<sub>chg2</sub>, though VCC charge function reacts, due to VCC UVLO is detected, the charge continues.

D: VCC voltage> Vuvio1, the VCC UVLO is released, and DC/DC operation starts, the charge to VCC stops.

E: VCC voltage>  $V_{chg1}$ , the charge to VCC restarts.

F: VCC voltage> Vovp1, VCC OVP is detected.

G: VCC voltage>  $V_{ovp2}$ , if VCC voltage drops below  $V_{ovp2}$  in 100us, VCC OVP is released, and the latch will not be activated. H:  $V_{ovp2}$ < VCC voltage <  $V_{ovp1}$ , if this state is kept longer than 100us, switching stops by latch.

I: VCC voltage  $< V_{uvlo1}$ , VCC UVLO is detected.

J : VCC voltage < V<sub>latch2</sub>, the latch state is released.

K : VCC voltage< V<sub>cs</sub> 、 the charging current to VCC changes from start2(3mA typ)⇒Istart1(700uA typ)

### (4)Over Current Detection

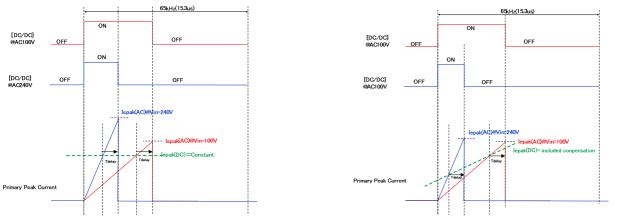

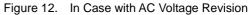

Over current limiter for each switching cycle is built in this IC. When the SOURCE pin voltage exceeds certain value, the switching operation stops. And an AC voltage revision function is built in. This function is achieved by increasing the level of the over current limiter together with the time. Through this, the AC voltage revision function works. It is showed in Figure 11,12,13.

Figure 11. In Case without AC Voltage Revision

In case of the over load mode, the peak current in primary side is decided by the formula below.

Peak current in primary side: Ipeak = Vcs/Rs + Vdc/Lp\*Tdelay Vcs : the voltage of the over current limiter in IC Rs : resistance for current sensing Vdc : input DC voltage Lp : inductance value in primary side

Tdelay : the delay time after detecting of the over current limiter

Figure 13. Over Current Limiter Voltage

### (5) L.E.B blanking period

When the MOSFET driver is turned ON, surge current occurs by the capacitive components and drive current. In this case, if the SOURCE pin voltage rises temporarily, false detections may occur in the over current limiter circuit. For preventing from the false detections, a L.E.B function (Leading Edge Blanking function) which masks the SOURCE voltage during the 200nsec after the OUT pin switches form  $L \rightarrow H$  is built in.

## Operation mode of protection circuit

Operation mode of protection circuit

| Abnormal state<br>detection |      | Detect   | Release                                   | Protection<br>operations                      |  |

|-----------------------------|------|----------|-------------------------------------------|-----------------------------------------------|--|

|                             | UVLO | 8.2V 以下  | >=13.5V                                   | Auto recovery                                 |  |

| VCC                         | OVP  | 27.5V 以上 | Before latch∶<=23.5V<br>Latched∶VCC<=7.7V | 100us timer latch                             |  |

| TSD                         |      | 175℃以上   | ラッチ前∶155℃以下<br>ラッチ後∶VCC=7.7V 以下           | Before latch:<br><=155°C<br>Latched:VCC<=7.7V |  |

| ZT                          | OVP  | 3.50V 以上 | Before latch∶<=3.33V<br>Latched∶VCC<=7.7V | 100us timer latch                             |  |

| Table 2. | Operation Mode of Protection Circuit |

|----------|--------------------------------------|

|----------|--------------------------------------|

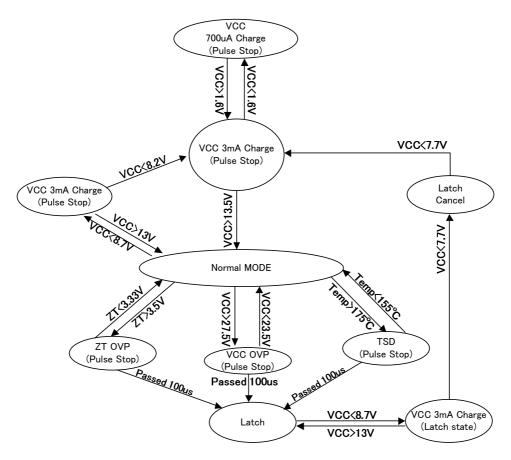

### Sequences

he sequences diagram of all states of this IC is showed in Figure 14.

Figure 14. Transition Diagram for All States

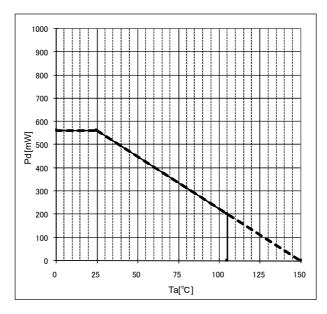

# Thermal loss

According to the thermal design, please observe the conditions below when use this IC.

- 1. The ambient temperature Ta must be 105°C or less.

- 2. The consumption of the IC must be within the allowable dissipation  $\mathsf{P}_{\mathsf{d}}.$

### The thermal dissipation characteristics are as follows.

(PCB: 70 mm × 70mm × 1.6 mm, mounted on glass epoxy substrate)

Figure 15. Thermal Dissipation Characteristics

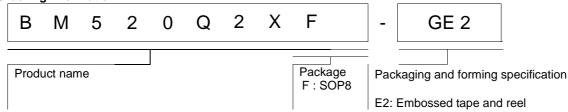

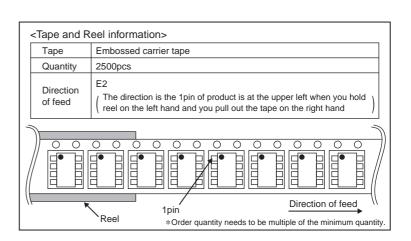

# Ordering Information

# Physical Dimension and Forming Specification

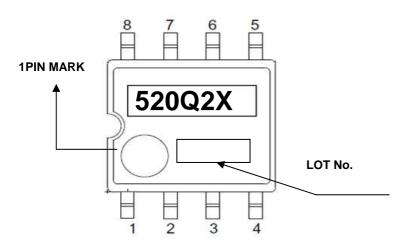

# Marking Diagram

# ●Line Up

| <b>形名</b> (BM520Q2XF) |

|-----------------------|

| BM520Q25F             |

| BM520Q29F             |

# Cautions on Use

### (1) Absolute maximum ratings

Operating the IC over the absolute maximum ratings may damage the IC. In addition, it is impossible to predict all destructive situations such as short-circuit modes, open circuit modes, etc. Therefore, it is important to consider circuit protection measures, like adding a fuse, in case the IC is operated in a special mode exceeding the absolute maximum ratings.

(2) Power supply lines

Design the PCB layout pattern to provide low impedance ground and supply lines. Separate the ground and supply lines of the digital and analog blocks to prevent noise in the ground and supply lines of the digital block from affecting the analog block. Furthermore, connect a capacitor to ground at all power supply pins. Consider the effect of temperature and aging on the capacitance value when using electrolytic capacitors.

(3) Ground voltage

The voltage of the ground pin must be the lowest voltage of all pins of the IC at all operating conditions. Ensure that no pins are at a voltage below the ground pin at any time, even during transient condition.

(4) Shorting between pins and mounting errors

Be careful when mounting the IC on printed circuit boards. The IC may be damaged if it is mounted in a wrong orientation or if pins are shorted together. Short circuit may be caused by conductive particles caught between the pins.

(5) Operation under strong electromagnetic field

Operating the IC in the presence of a strong electromagnetic field may cause the IC to malfunction.

(6) Input terminals

In the construction of this IC, P-N junctions are inevitably formed creating parasitic diodes or transistors. The operation of these parasitic elements can result in mutual interference among circuits, operational faults, or physical damage. Therefore, conditions which cause these parasitic elements to operate, such as applying a voltage to an input pin lower than the GND voltage should be avoided. Furthermore, do not apply a voltage to the input terminals when no power supply voltage is applied to the IC. Even if the power supply voltage is applied, make sure that the input terminals have voltages within the values specified in the electrical characteristics of this IC.

(7) External capacitor

When using a ceramic capacitor, determine the dielectric constant considering the change of capacitance with temperature and the decrease in nominal capacitance due to DC bias and others.

(8) Thermal consideration

Use a thermal design that allows for a sufficient margin by taking into account the permissible power dissipation (Pd) in actual operating conditions.

(9) Rush current

When power is first supplied to the IC, rush current may flow instantaneously. It is possible that the charge current to the parasitic capacitance of internal photo diode or the internal logic may be unstable. Therefore, give special consideration to power coupling capacitance, power wiring, width of GND wiring, and routing of connections.

(10) Unused input terminals

Input terminals of an IC are often connected to the gate of a CMOS transistor. The gate has extremely high impedance and extremely low capacitance. If left unconnected, the electric field from the outside can easily charge it. The small charge acquired in this way is enough to produce a significant effect on the conduction through the transistor and cause unexpected operation of IC. So unless otherwise specified, input terminals not being used should be connected to the power supply or ground line.

(11) About this document

Although the functional description and application notes given in this document for the IC are reliable, it does not mean that the particular application a user designs with this IC is guaranteed to work. It is the user's responsibility to check well the design application including other external devices used together with this IC.

Status of this document

The Japanese version of this document is the formal specification. A customer may use this translated version only as an aid in reading the formal version.

If there are any differences between the translation and formal version of this document, the formal version takes priority.