大家好,很高兴和各位一起分享我第 79 篇原创文章,喜欢和支持我的工程师,一定记得给我点赞、收藏、分享哟。

加微信【jiyuyun18】与作者沟通交流。

1 锁相环

锁相环电路(PLL)是一种利用反馈控制原理实现频率和相位同步的电路,可将两个信号在频率和相位上锁定在一起,用于FM、AM调制、频率合成、时钟恢复等多种用途。

锁相环电路的基本原理:

锁相环电路由三个基本部分组成:鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)。

- 鉴相器:Phase Detector, 也成为相位检测器。

- 环路滤波器:Loop Filter, 大多数情况下就是一个低通滤波器。

- 压控振荡器:Voltage Controlled Oscillator。

如果是在手机上阅读本文,点击图片可放大。

锁相环的工作原理是:鉴相器如果检测到两个输入之间的相位差,鉴相器将输出与相位差成比例的脉冲信号,这些脉冲信号将被滤波成 VCO 的输入电压,该电压将调整 VCO 的输出信号频率和相位,并试图消除鉴相器两个输入信号之间的相位差。

上面的工作原理和负反馈运放差不多,运放在负反馈时总是竭尽所能试图消除其两个输入引脚之间的压差。

在许多情况下,环路滤波器实际上不过是一个简单的低通滤波器,可能是一个简单的 RC 滤波器。其主要任务就是从相位检测器中取出脉冲,并将它们转换成一个控制电压,用于控制 VCO。

锁相环电路的应用:

- 频率合成:锁相环电路可以用于频率合成,即利用一个基准频率产生多个不同频率的信号。

- 频率同步:锁相环电路可以用于频率同步,即将两个或多个频率不同的信号同步到同一个频率。

- 调制解调: 锁相环电路可以用于调制解调,即将信息调制到载波信号上,或从载波信号中解调出信息。

- 信号恢复: 锁相环电路可以用于信号恢复,即从一个噪声污染的信号中恢复出原始信号。

2 CD4046

CD4046 芯片是一种由 CMOS 工艺制造的锁相环 (PLL) 集成电路。它具有以下特点:

- 电源电压范围宽: 3V 至 18V

- 输入阻抗高: 约 100MΩ

- 功耗低: 在中心频率为 10kHz 时,功耗仅为 600μW

CD4046 芯片内部包含以下功能模块:

- 鉴相器: 比较两个输入信号的相位差,并产生一个与相位差成比例的误差电压。

- 环路滤波器: 滤除误差电压中的高频噪声,并将其输出给压控振荡器。

- 压控振荡器: 根据环路滤波器的输出电压调整其输出频率和相位。

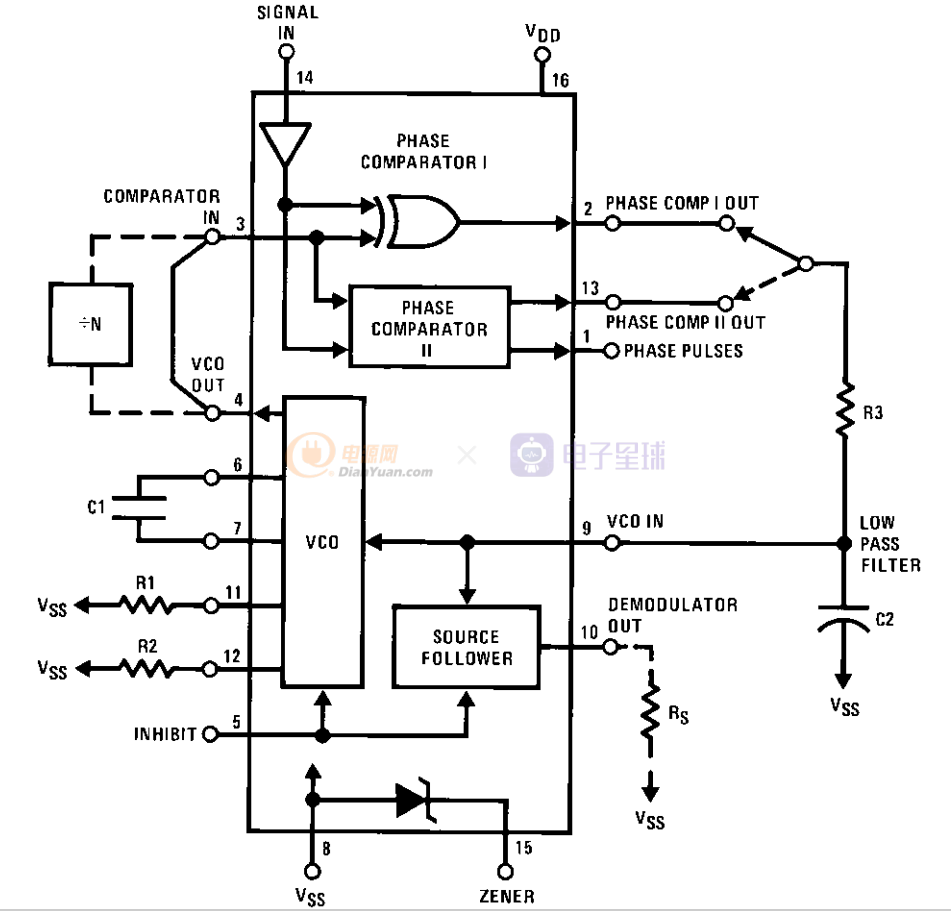

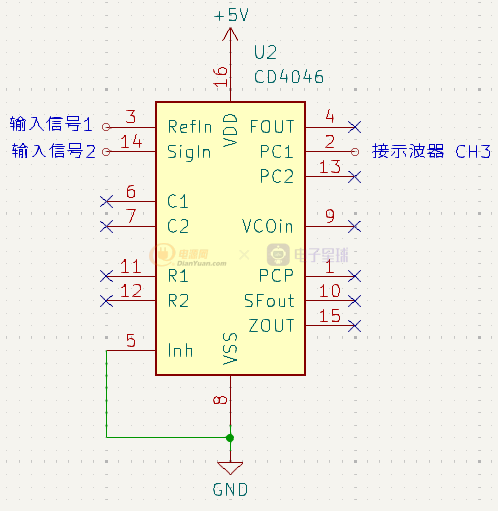

CD4046 的框图如下:

CD4046采用的是 RC 型压控振荡器,必须外接电阻电容作为充放电元件,上图中外接电阻 R1 和 电容 C1 决定了 VCO 的振荡频率。

外接电阻 R2 电阻决定控制电压为零时的最低振荡频率。

引脚定义如下:

1 引脚:鉴相器 2 相位输出端,环路锁定时为高电平,环路解锁时为低电平

2 引脚:将向其 1 的输出端

3 引脚:比较信号输入端

4 引脚:VCO 的输出端

5 引脚:禁止使能。高电平禁止,低电平允许工作

6 引脚:接外部振荡电容

7 引脚:接外部振荡电容

8 引脚:电源负极

9 引脚:VCO 控制电压输入

10 引脚:解调输出端,用于调频解调

11 引脚:接外部振荡电阻

12 引脚:接外部振荡电阻

14 引脚:信号输入端

15 引脚:内部独立的齐纳稳压二极管负极

16引脚:电源正极

3 VCO 原理和实验

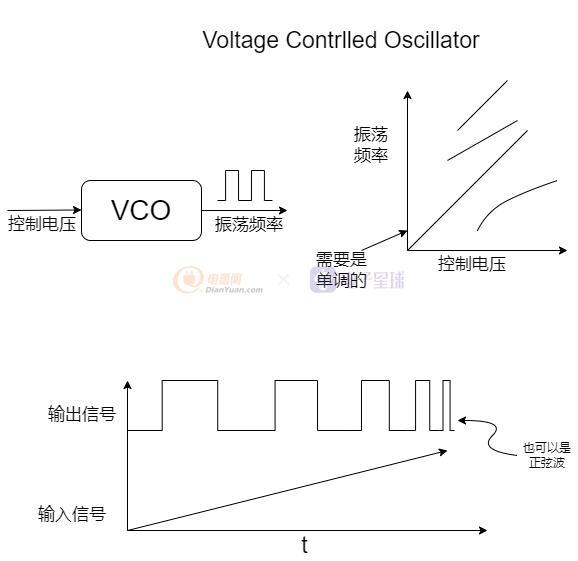

VCO(电压控制振荡器)实际上就是一个振荡器,其频率可以通过外部电压来改变。控制电压可和输出频率的关系基本上是线性的,它可能有一些偏移,甚至可能有一些曲线。在使用范围内它需要是单调的(monotonic ),意味着斜率始终必须为正。否则会影响反馈,导致环路无法工作。

从上图中可以看到,如果输入的控制电压随时间线性增加,输出频率会随时间增加得越来越快。

CD4046 内部集成了一个 VCO, 我们使用它学习和观察 VCO。CD4046 采用的是 RC 型压控振荡器,必须外接电容C1和电阻R1作为充放电元件。当PLL对跟踪的输入信号的频率宽度有要求时还需要外接电阻R2。由于VCO是一个电压控制振荡器,对定时电容C1的充电电流与从9脚输入的控制电压成正比,使VCO的振荡频率亦正比于该控制电压。当VCO控制电压为0时,其输出频率最低;当输入控制电压等于电源电压VDD时,输出频率则线性地增大到最高输出频率。VCO振荡频率的范围由R1、R2和C1决定。由于它的充电和放电都由同一个电容C1完成,故它的输出波形是对称方波。

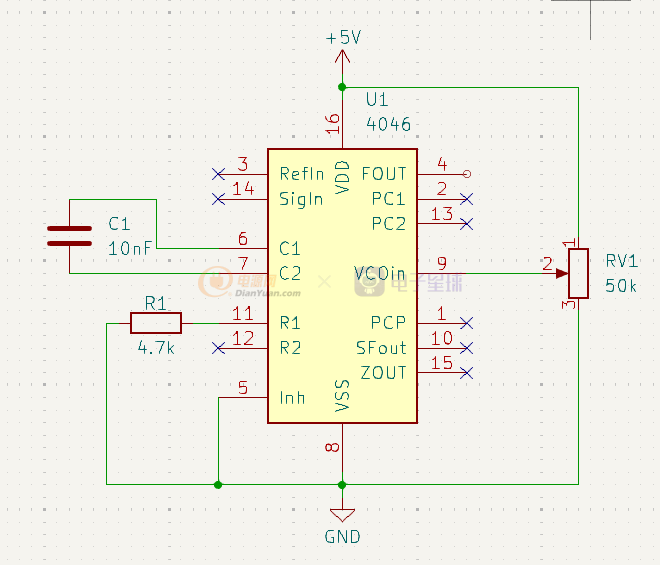

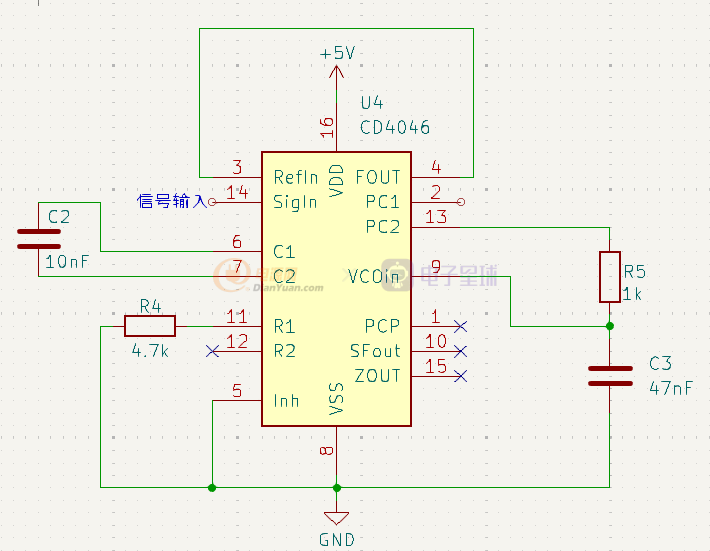

我们给芯片使用 5V 供电,11脚接 4.7k 电阻,6脚和7脚之间接 10nF 电容,9脚上接 50k 电阻,用于改变 VCO 控制电压,其余引脚悬空。

VCO 实验电路如下:

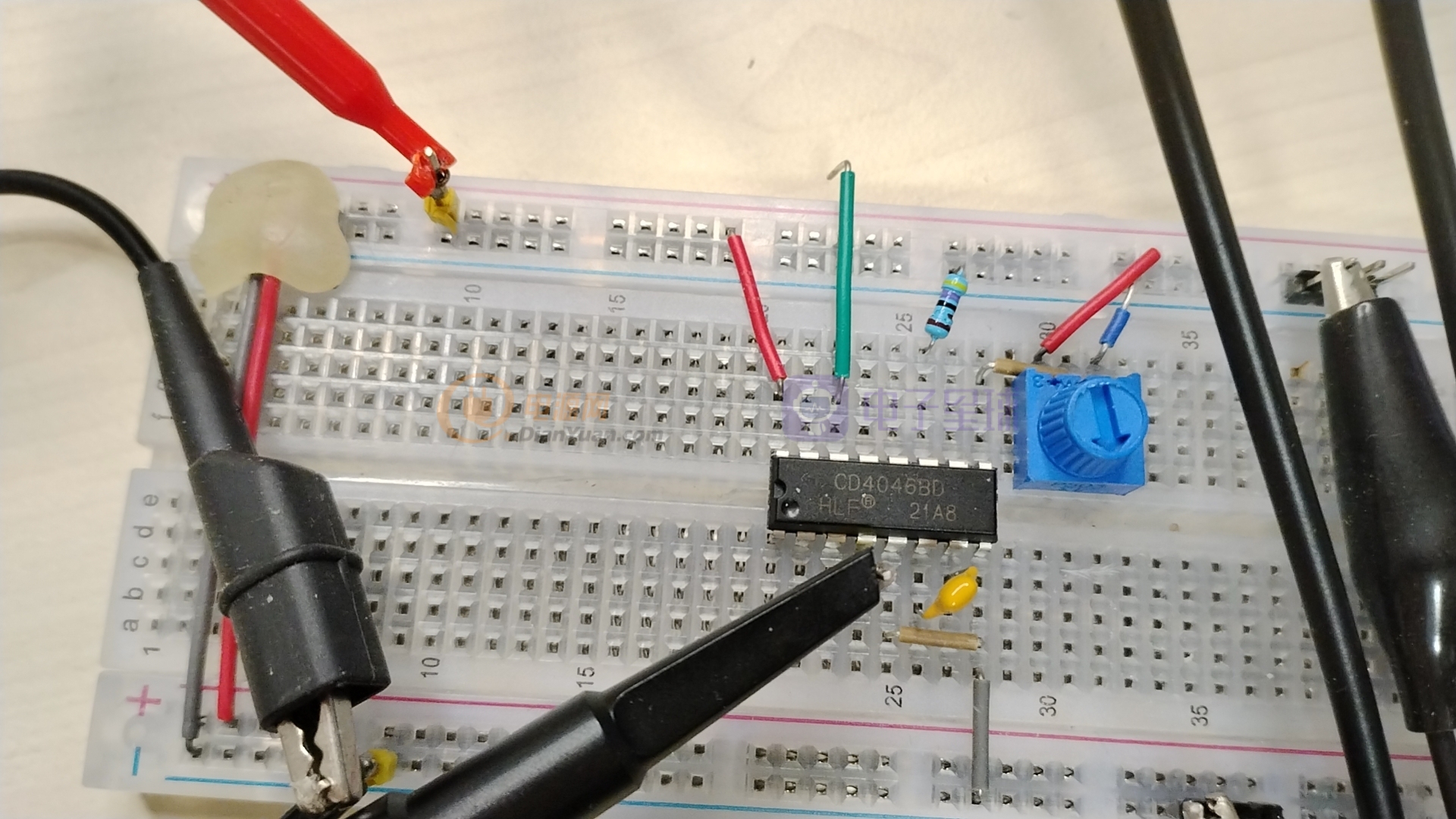

面包板上搭建好的实验电路如下:

示波器通道1探头接 VCO 输出引脚4,当我调节可调电阻,使 9脚 VCO 控制电压不断增大时, 4脚 VCO 输出频率不断随之变大:

4 Ⅰ型鉴相器原理和实验

CD4046 内部集成了两种类型的可单独使用的鉴相器。

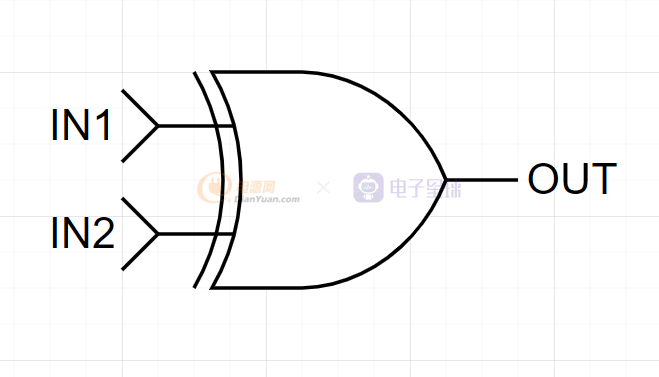

Ⅰ型鉴相器是一个异或门,当两个输入端信号的电平状态相异时(即一个为高, 一个为低电平),输出端信号为高电平;反之,两个输入信号均为高,或均为低电平时, 输出为低电平。

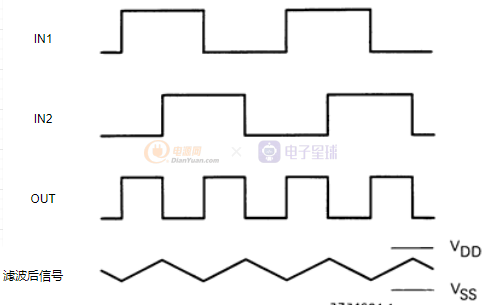

下图是从比较器Ⅰ的输入和输出信号的波形:

Ⅰ型鉴相器优点:

- 当输入信号有噪音时表现良好

- 简单易用

Ⅰ型鉴相器缺点:

- 可能会锁定到谐波

- 锁定时的相位可能是 0-180°

- 输入应该具有 50% 的占空比

- 没有真正的频率检测

Ⅰ型鉴相器实验电路如下:

我们将鉴相器的两个输入引脚分别接入一路由信号源产生的信号,Ⅰ型鉴相器输出引脚接示波器 CH3 探头。

信号源设置如下:

信号源设置两路信号没有相位差时,即鉴相器两路输入信号相位相同时波形如下:

CH1(黄色)接鉴相器输入引脚 14

CH2(青色)接鉴相器输入引脚 3

CH3(紫色)接Ⅰ型鉴相器结果输出引脚 2

通过 CH3 看一看到一根根细小的针,说明鉴相器是很灵敏的,检测到了两路信号之间的微小相位差异。

逐渐增大两路信号的相位差至45°波形变化如下:

信号源逐渐增大 CH2 信号相位至 45° 波形如下:

I 型鉴相器有一个缺点:无法分辨两路输入信号那个相位在前哪个在后。

5 Ⅱ型鉴相器原理和实验

Ⅱ型鉴相器也被称为鉴相鉴频器。对应英文是 Phase Frequency Detector, 缩写是 PFD。

Ⅱ型鉴相器基本电路图如下:

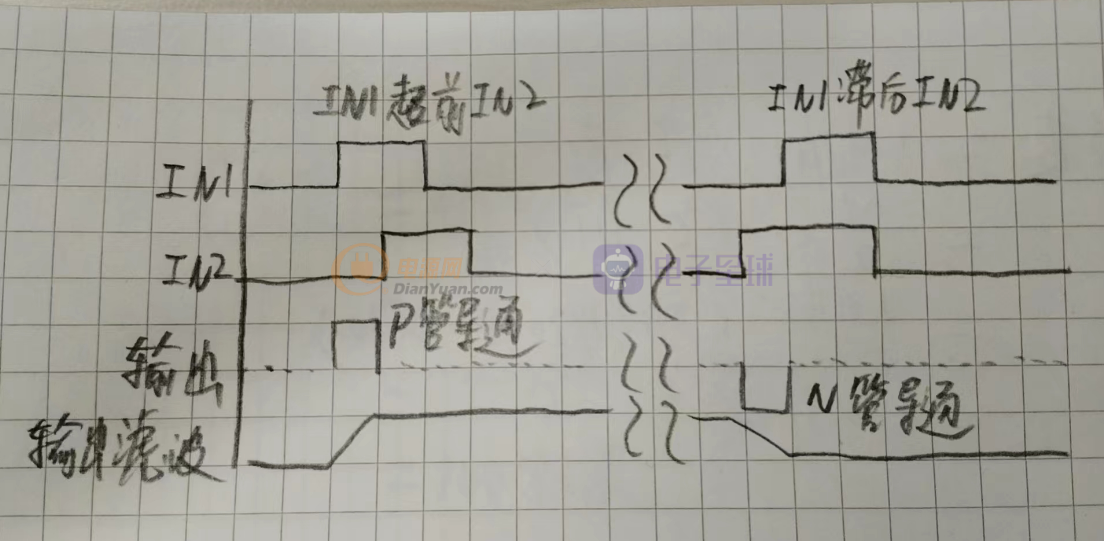

相位比较器II是一个边沿控制的数字存储网络。当P-MOS或N-MOS驱动器打开时,它们分别将输出拉高到VDD或拉低到VSS。这种类型的相位比较器只在输入信号的上升沿时进行比较(两路输入信号中的任意一路,以先出现为准),信号(14脚)和比较器输入(3脚)的占空比并不重要。如果两个信号输入频率不同,而N和P驱动器都处于关闭状态(三态),相位比较逻辑会调整其内部电路直至两路输入信号频率相同。

如果信号(14脚)和比较器输入(3脚)频率相同,但信号输入滞后于比较器输入相位,那么N型输出驱动器将保持打开状态,时间与相位差相对应。如果信号和比较器输入频率相同,但比较器输入滞后于信号相位,那么P型输出驱动器将保持打开状态,时间与相位差相对应。随后,调整连接到该相位比较器的低通滤波器的电容电压,直到信号和比较器输入在相位和频率上相等。在这个稳定点,N型和P型输出驱动器都保持关闭状态,因此相位比较器输出变成了开路输出,并保持低通滤波器的电容电压恒定。此外,“相位脉冲”输出引脚 1 处的信号为高电平,可用于指示已锁定的状态。因此,对于相位比较器 II,在整个VCO频率范围内,信号和比较器输入之间不存在相位差。此外,当使用此类型的相位比较器时,由于大部分信号输入周期中P型和N型输出驱动器都处于关闭状态,低通滤波器的功耗降低。值得注意的是,对于这种类型的相位比较器,PLL锁定范围等于捕获范围,与低通滤波器无关。在信号输入处没有信号时,相位比较器II将VCO调整到其最低频率。

Ⅱ型鉴相器 优点:

良好的频率检测

不会锁定到谐波

输入信号不必具有 50% 的占空比

可以在 0° 相位锁定

缺点:

更复杂

在输入信号有噪音时表现不良

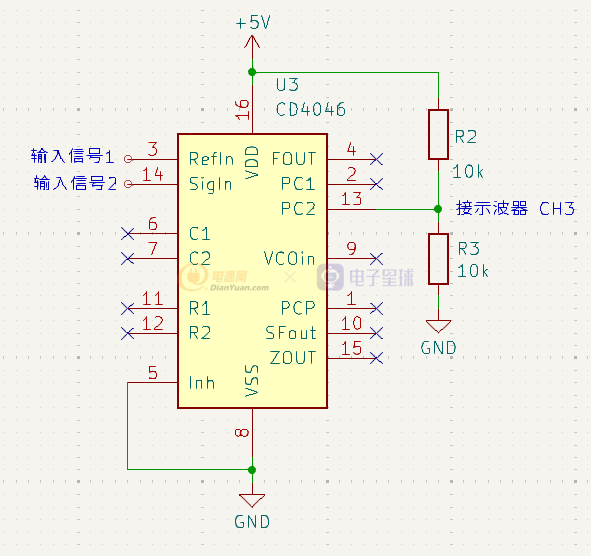

Ⅱ型鉴相器实验电路如下:

我们在Ⅱ型鉴相器结果输出引脚 13 接了上下拉电阻,因为当两个信号处于同相时,此处为开路,我们通过上下拉电阻给了一个确定的电压。

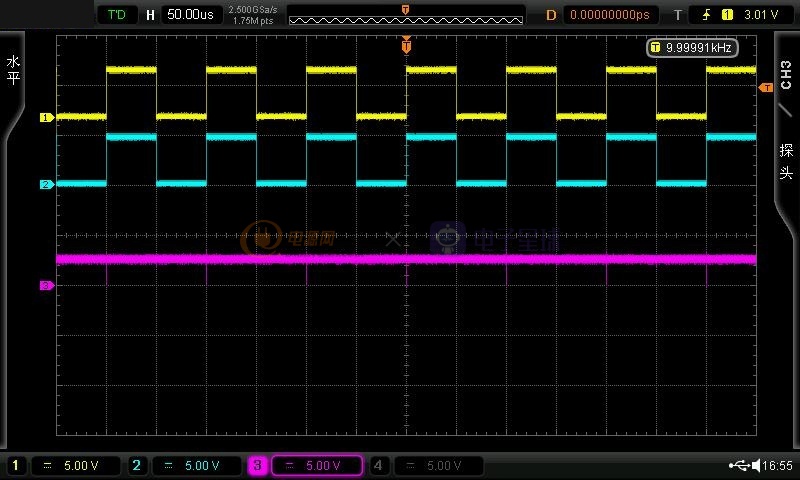

当两个输入信号同相时波形如下:

逐渐增大信号源 CH1 使其相位至45°时波形如下:

逐渐增大信号源 CH2 使其相位至45°时波形如下:

可以看到,随着相位超前的信号不同,比较结果波形中会对应出现正脉冲和负脉冲,可以籍此判断哪一个信号超前。Ⅰ型鉴相器则只能鉴别出差异,区分不出哪个超前哪个滞后。

6 PLL 实验

PLL 各部分实验已经完成,我们把闭合整个环路进行实验。

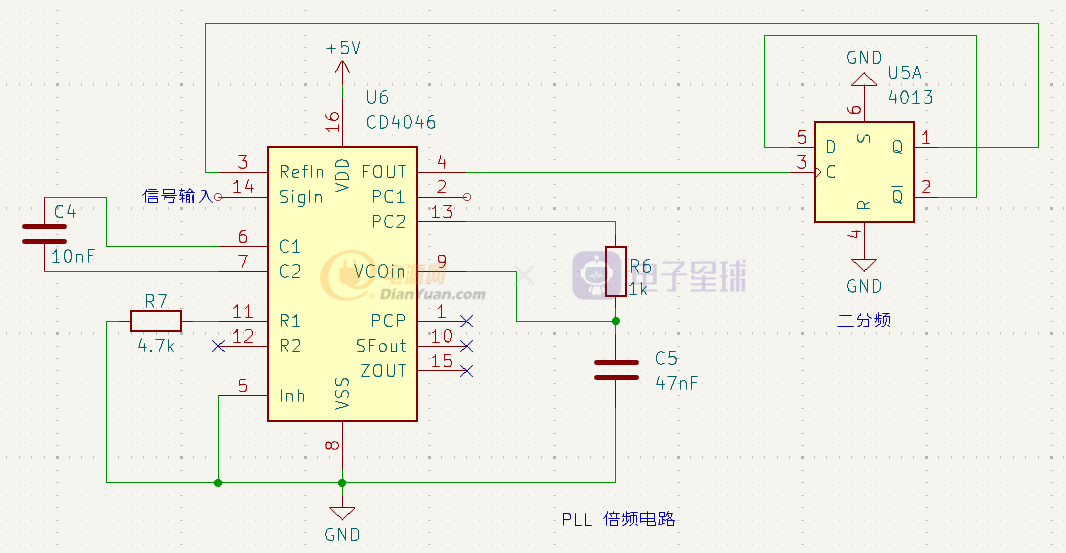

PLL 环路实验电路图如下:

鉴相器需要两路输入信号以进行比较。我们使用外部信号源的方波信号作为一路输入信号,接到14脚上。我们把 4 脚 VCO 的输出的脉冲信号接到鉴相器的另一路输入 3 脚上。我们使用13 脚输出的 II 型鉴相器比较结果经低通滤波后驱动 VCO。

我们 使用 1k 电阻加 47nF 电容组成低通滤波器对鉴相器输出脉冲信号进行滤波,其截止频率为 3.4kHz。

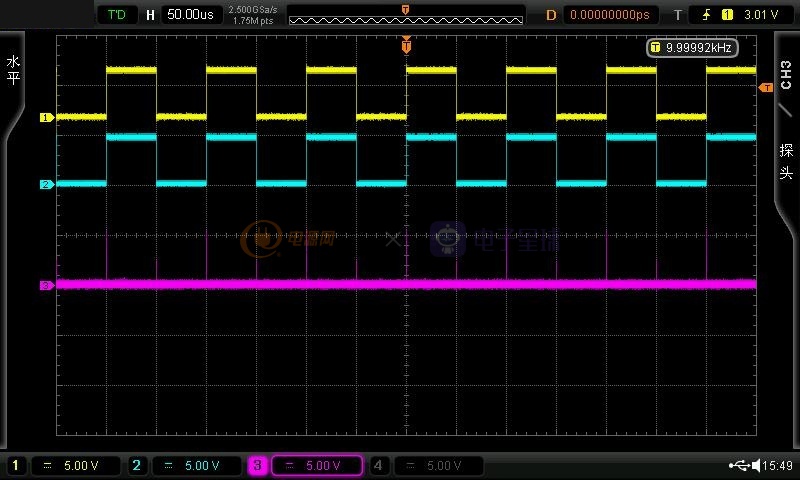

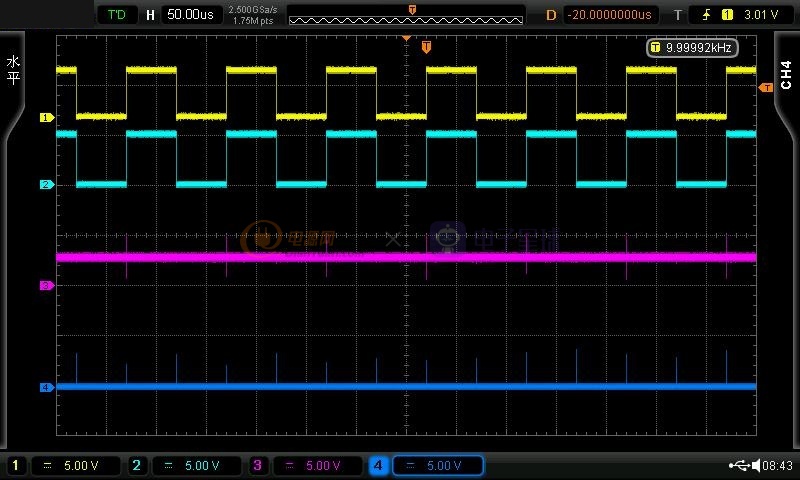

14脚输入 10kHz 波形如下:

CH1(黄色)测量的是输入信号,探头接引脚 14。

CH2(青色)测量的是 VCO 输出信号,探头接引脚 4。

CH3(紫色)测量的是 II 型鉴相器比较结果,探头接引脚 13。

CH4(蓝色)测量的是 I 型鉴相器比较结果,探头接引脚 2。

CH3 波形是 II 型鉴相器比较结果,你可以看到一点点轻微的向上或向下的脉冲,这是整个环路闭合的结果。

CH4 波形是 I 型鉴相器的比较结果,我们没有在环路中使用它,放在这里是为了和 II 型鉴相器的结果进行参考。

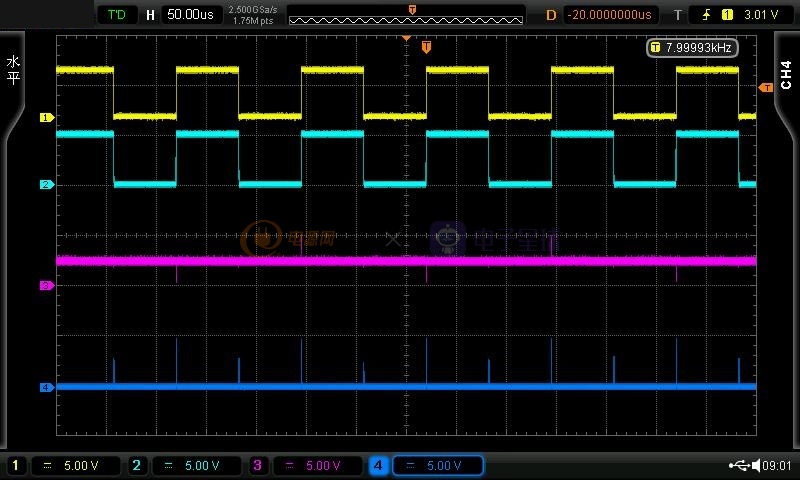

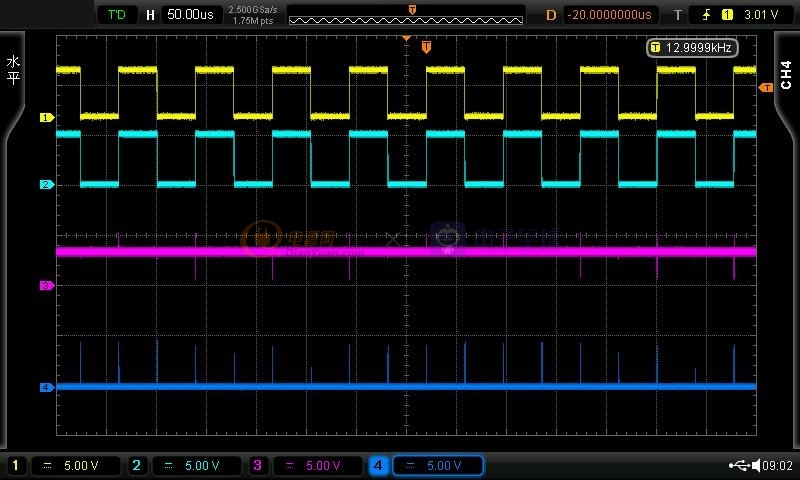

如果我把信号源输入信号频率改为 8kHz 和 13kHz 时, 整个环路依然能够闭合:

如果是在手机上阅读本文,点击图片可放大。

输入信号从 8kHz 到 13kHz 范围变化时的波形如下图:

在 8kHz 到 13kHz 范围内,VCO 输出的脉冲(CH2)始终能和输入信号保持同步,很神奇。

实验到这里,我们再看一遍如同天书的锁相环定义:

锁相环是利用反馈控制原理实现的频率及相位的控制系统,其作用是将电路输出的信号与其外部的参考信号保持同步,当参考信号的频率或相位发生改变时,锁相环会检测到这种变化,并且通过其内部的反馈系统来调节输出频率,直到两者重新同步,这种同步又称为“锁相”(Phase-locked)。

或许会理解这段初看味同嚼蜡的话是什么意思。

模拟电路一定要理论和实践相结合,初学理论可能不大理解,放下执念,放下对自己智商的怀疑,做个实验回头再看理论就会好理解很多。

7 倍频和降频

锁相环的一个常见应用是频率合成(Frequency Synthesis)。你可以通过对进入相位检测器的信号进行一些调整来实现这一点,例如,如果在VCO输出和相位检测器之间放一个除以2的分频器:

那意味着相位检测器会希望其输入的两个信号在频率和相位上匹配,所以现在如果我们在其输入端从外部输入一个 10 kHz 的信号,那么它希望在其另一个输入端看到10 kHz 的输入信号,这意味着环路中的 VCO 将不得不生成 20kHz 来实现这一点。所以通过简单地进行 2 分频,我们实际上现在创建了一个与该输入信号锁相的信号,但其频率是该输入信号的两倍。

我们通过在 VCO 和鉴相器之间加一个分频器,来“欺骗” VCO, 让其输出信号倍频。

如果我们在外部输入信号后面加一个分频器,那将会产生降频的效果,所以如果我将外部参考信号进行分频,那么这将导致VCO的输出电压降低,进而其输出的振荡信号频率降低:

倍频实验电路图如下:

我们使用 CD4013 双 D 触发器芯片进行二分频,把分频后的信号输入到Ⅱ型鉴相器输入引脚3。VCO 的输出接到触发器的输入引脚 3。

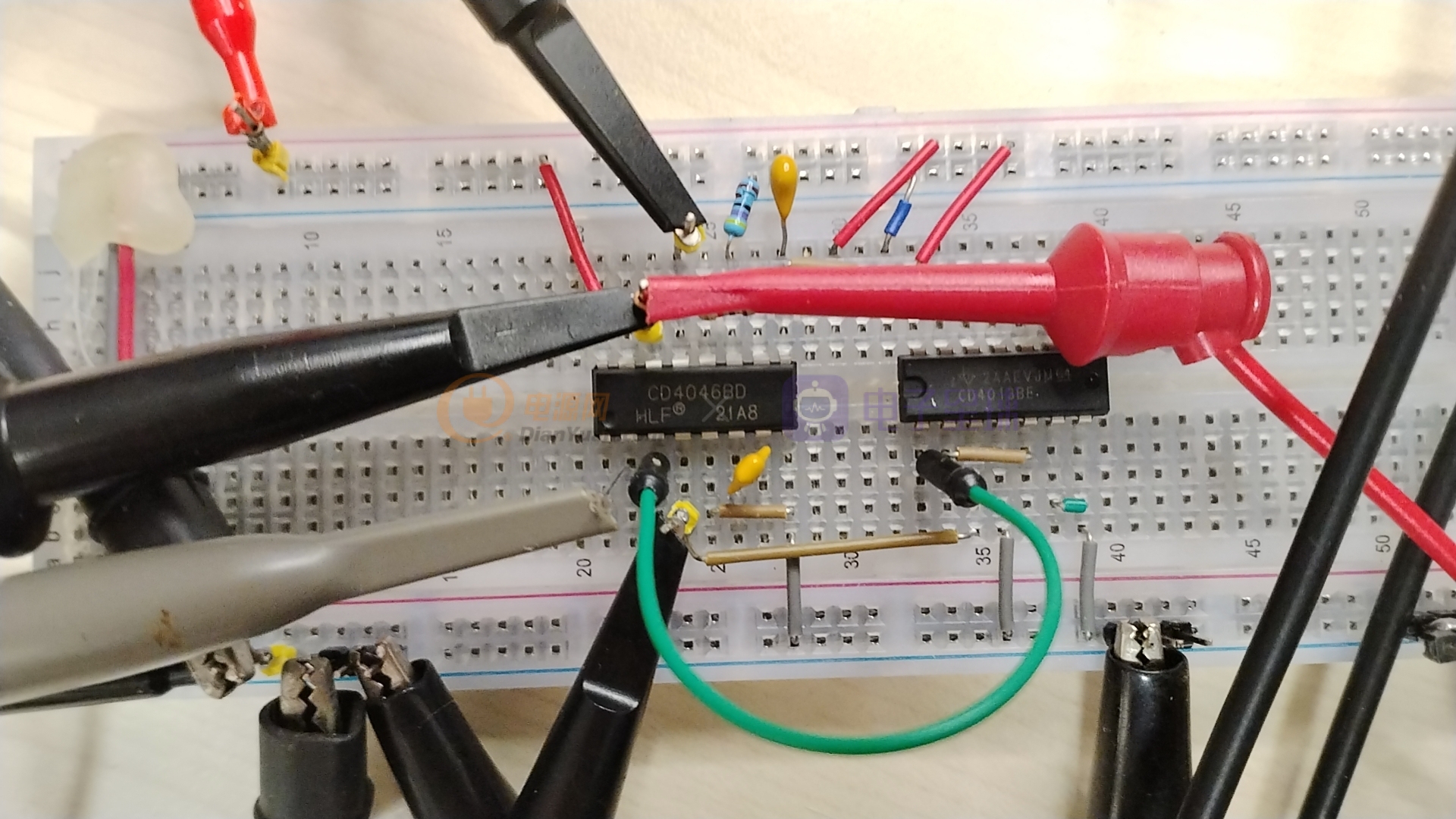

面包板上安装好的电路如下:

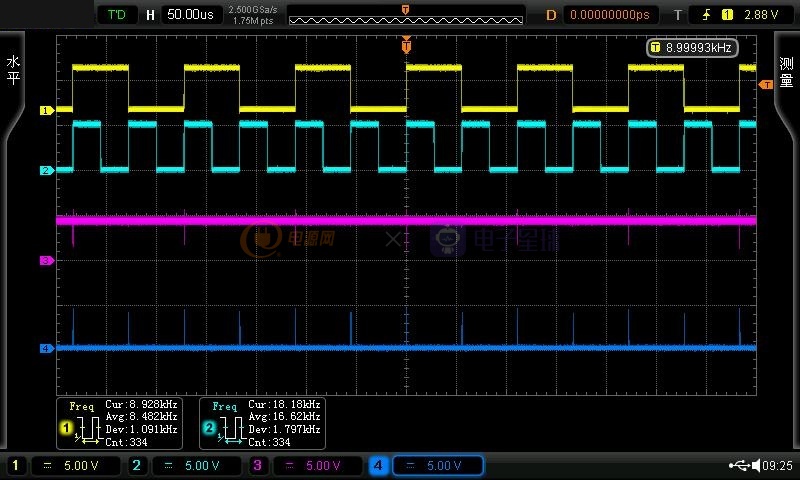

14脚输入 9kHz 频率信号波形如下:

CH1(黄色)测量的是输入信号,探头接引脚 14。

CH2(青色)测量的是 VCO 输出信号,探头接引脚 4。

CH3(紫色)测量的是 II 型鉴相器比较结果,探头接引脚 13。

CH4(蓝色)测量的是 I 型鉴相器比较结果,探头接引脚 2。

输入 9kHz 信号(右上角测出的频率为硬件实现,准确些),VCO 倍频后使用示波器自带的自动测量功能(软件实现)频率为 18.18kHz,不是期望的 18kHz, 可能是测量不准或其他原因导致,本文不做探究。

8 总结

本文介绍了锁相环电路和频率合成的基础知识。锁相环电路可以将两个信号在频率和相位上锁定在一起,用于调频、调幅、频率合成等多种用途。通过实验演示了锁相环电路的工作原理,以及如何通过调节输入信号和反馈信号来实现频率合成。

既然看到这里了,就帮忙点个赞吧!