1. 电快速瞬变脉冲群测试的实质

前面通过对标准的解读,我们知道电快速瞬变脉冲群测试主要有两种形式:耦合/去耦网络和容性耦合夹。电源端口采用耦合/去耦网络试验的接线方式是:试验发生器电芯通过可供选择的耦合电容加到电源线上,信号电缆的屏蔽层则和耦合/去耦网络的外壳相连,而外壳接PE地。这就表明脉冲群干扰实际上是加在电源线与参考接地之间,其实质是共模干扰。信号端口采用耦合夹的实验方式来说,电快速瞬变脉冲通过耦合板与受试电缆之间的分布电容进入受试电缆,而受试电缆所接收到的脉冲仍然是相对参考接地板来说的,其实质也是共模干扰。

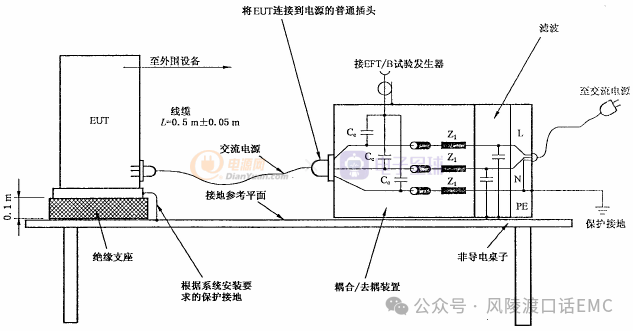

电快速瞬变脉冲群试验台布置图

2. 电快速瞬变脉冲群干扰机理分析

2.1 电快速瞬变脉冲群的特点

电快速瞬变脉冲群的特点是骚扰信号不是单个脉冲,而是一连串的脉冲群。一方面是由于脉冲群可以在电路的输入端产生积累效应,使骚扰电平的幅度最终可能超过电路噪声容限。另一方面脉冲群的周期短,每个脉冲波的间隔时间较短,当第一个脉冲波还未消失时,第二个脉冲波紧跟而来。对于电路中的输入电容来说,在未完成放电时又开始充电,因此,容易达到较高的电压,对电路的正常工作影响较大。 电快速瞬变脉冲群骚扰源的电压的大小取决于负载电路的电感,负载断开速度和介质的耐受能力。骚扰电压的特点是:幅值高,频率高,其实质是共模电压,是通过电容耦合间接传输至其它电路。当由一个电路的电流产生的磁场穿过第二个电路的电流环路时,就会产生磁场耦合;当由一个电路的电压产生电场与第二个电路的信号布线平行时就会产生容性耦合。电快速瞬变脉冲群(EFT)与ESD是两种突发干扰,EFT信号单脉冲的峰值电压高达4KV,上升沿5ns。而接触放电测试时的ESD信号的峰值电压可高达8KV,上升时间小于1ns。都属于高电压,宽频带的特点。

2.2 电快速瞬变脉冲群干扰机理分析:

EFT试验波形的上升沿很陡,包含了很丰富的高频成分。另外,由于试验脉冲是持续一段时间的脉冲串,因此它对电路的干扰有一个累积效应,大多数电路在输入端未安装有效滤波电路,不能有效滤除EFT干扰。EFT对设备影响的原因有三种:

- 通过电源线直接传导进设备的电源,产生干扰电流的主要部分流入低阻抗的参考平面,引起参考平面电位的变化,信号电平从而随之波动,导致信号电平的传输错误、或者不稳定,系统出现异常。

- EFT干扰电流流过参考地平面时,由于地平面寄生电感的存在,参考地平面间不等位,导致平行于参考地平面较长的GPIO信号布线,会因为容性耦合与感性耦合产生感应电压、感应电流。感应电流流入芯片内部时,造成芯片工作状态异常,感应电压超过噪声电压容限时同样会出现芯片工作状态异常。

- EFT干扰包含了丰富的高频成分,在电源线上传导的过程中,向空间辐射。辐射能量在邻近的信号电缆上感应出噪声电压,对信号电缆连接的电路形成干扰。辐射能量同样会在邻近的信号环路内产生感应电流,感应电流流入芯片内部,导致严重的干扰,而导致EFT测试的失败。

长期实践表明:一台设备往往是某一条电缆,在某一种试验电压,对某个极性特别的敏感。长期实验显示:信号线要比电源线对EFT干扰敏感得多。在电源系统上流动的干扰电流,产生很强的宽频谱电磁场,能干扰其周围集成电路、信号线、敏感器件,例如复位信号、片选信号、RX/TX信号、GPIO信号,由此引起系统的各种不稳定的现象。

需要注意,磁场不仅仅由电源线上干扰电流以及电缆上的电流产生,旁路电容的电流路径以及内部参考地平面上的电流也会扩大干扰的范围。