1.前言

最近在工作中遇到了一个时钟辐射(RE)超标的问题,前前后后经过差不多2周的时间,终于在这周五把问题解决了。解决的手段采用了三种:降低驱动电流;增加pF级别的电容;增加地搭接。

上述使用的三种方法,其实也是解决EMC问题常见的手法。本周周报将结合工作中遇到的EMC问题,把为什么要用这三种方法的原因和背后的原理进行分析,并分析产生这些问题的根本原因。

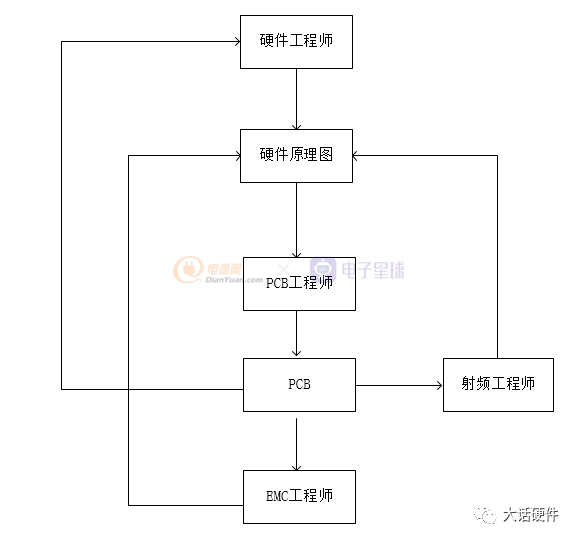

高速PCB的设计是高速电路中非常重要的环节,一般大厂的硬件和PCB是分开的,硬件工程师出原理图和PCB设计指导书;考虑到DFX方面,在原理图设计时,也会有EMC和射频工程师的加入。

PCB工程师完成PCB设计后,会发给EMC工程师,射频工程师,硬件工程师检查。比较尴尬的是,原理图是硬件工程师画的,而EMC和射频的东西又需要非常专业的理论作为指导。PCB工程师在完成Layout之后,如果EMC和射频工程师没有发现问题,硬件工程师估计也很难发现。但是,这个单板的负责人还是硬件。

因此,作为一名合适的单板硬件开发工程师来说,掌握基本的高速PCB设计规则还是非常有必要的。

2. EMC之辐射干扰

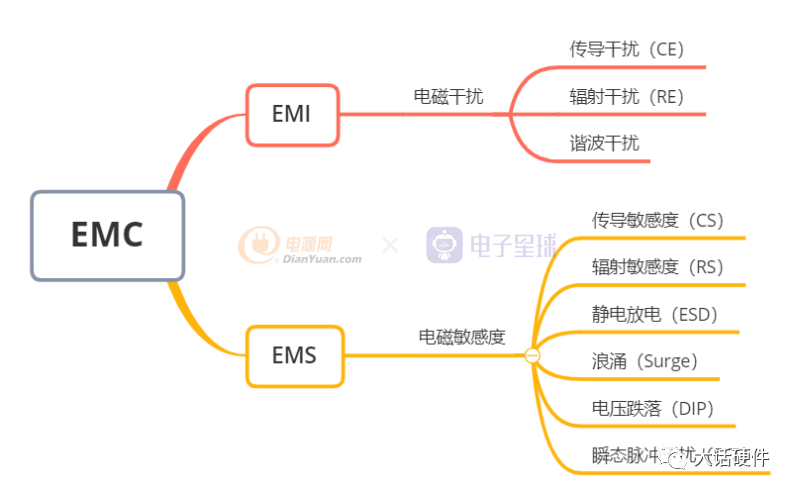

从下面整理EMC包含的内容可以看出,任何一款需要面向消费者的产品,仅仅在EMC方面的设计就要考虑这些问题。

虽然EMC工程师能帮我们在原理图阶段发现某些问题,但是他们经常需要一对多,不可能面面俱到。我们自身如果能掌握EMC基本的设计规则掌握,按照2/8定律来看,80%的产品也不会存在一些简单的EMC设计缺陷。

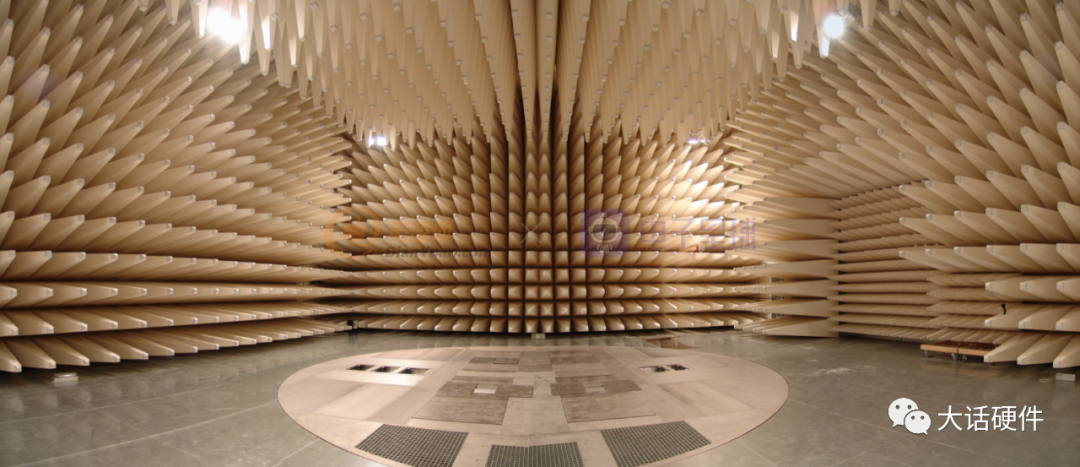

项目中出现的时钟超标的问题,是属于EMC中的EMI当中的辐射干扰。在测试辐射干扰时,我们需要遵循国标。对于工业产品来说,辐射干扰必须小于 Class A 等级;对于民用产品来说,辐射干扰必须小于 Class B等级。考虑到实际产品使用的场合,最好能留有一定的裕量,不同的公司可能标准还不一样。

测量辐射干扰所用的电波暗室如下。在测试时,先测量水平,再测量垂直,最后叠加的辐射就是总的辐射干扰。

图片来源于网络

上图显示的ClassA和ClassB是欧盟CISPR 22的标准中对ClassA和ClassB等级的要求。从图中可以得到的信息是,同等频率条件下,民用产品对RE的要求更苛刻。国标中也是一样。ClassB等级更严格。

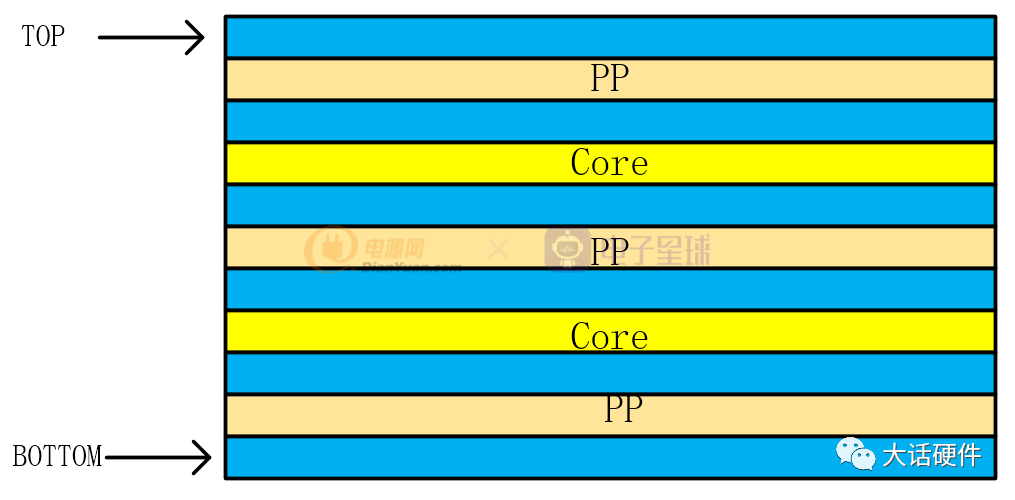

3. PCB之传输线

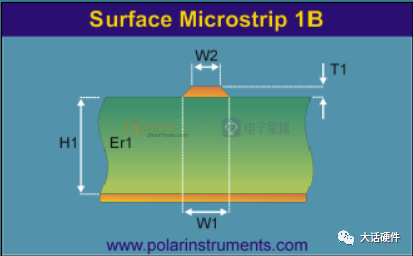

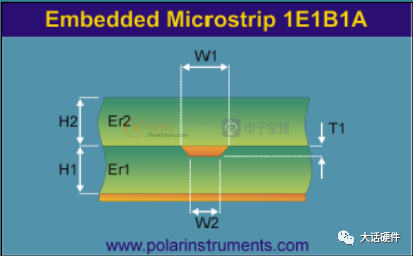

高速PCB设计中,按照传输线的结构,PCB上的走线可以分为微带线和带状线。微带线是指在PCB表层的走线。即我们设定的TOP层或者BOTTOM层,仅与一个参考层相邻。如下图所示。

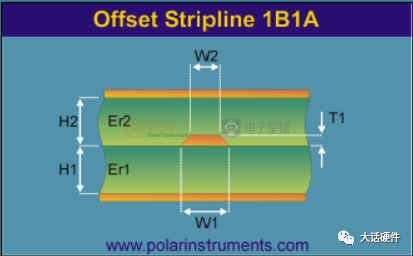

带状线指在PCB内层的走线,即我们设定的除TOP和BOTTOM层的走线层,位于两个参考层之间的走线。如下图所示。

还有一种是嵌入式的微带线,它是标准微带线的改进型,区别在于导线的表面覆盖了一层介质材料。如下图所示。

微带线和带状线的各自的特点如下:

(1)阻抗控制难易程度不一样

微带线一边是空气,一边是PP固态树脂,阻抗不好控制;带状线两边都是填充介质,阻抗可以更好的控制。

(2)走线速率不一样

空气的介电常数比PCB板材小,信号传输速率高。相比带状线,微带线的传输速率略高,延时更小。

(3)抗辐射程度不一样

微带线由于一面直接与空气接触,容易产生对外的辐射;带状线在两个参考层之间,能有效的屏蔽。

根据上述的特点可以看出,如果是走高速的时钟信号,最好是走在内层,并且用地线进行包地处理,可以有效的降低对外的辐射。

4. 信号上升速率

高速数字电路的PCB设计中,当布线长度大于λ/20(λ波长)或信号延时超过1/6信号上升沿时,PCB上的布线可以被视为传输线。信号上升沿越陡,高频分量越丰富,越容易出现信号完整性的问题。

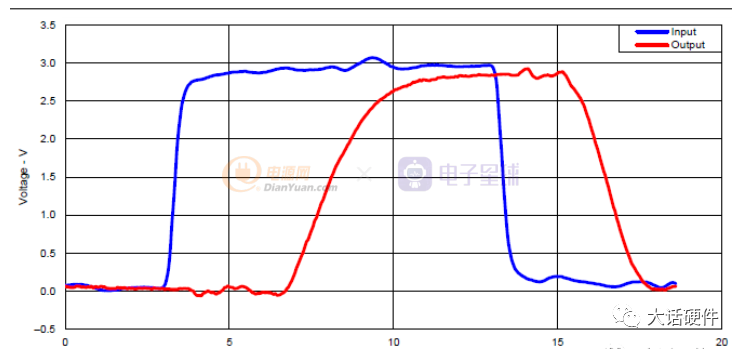

下图所示的信号,输入信号和输出信号上升沿斜率不一样,高频分量就会不一样。

在PCB中需要关注的信号完整性问题主要是反射,串扰,辐射。

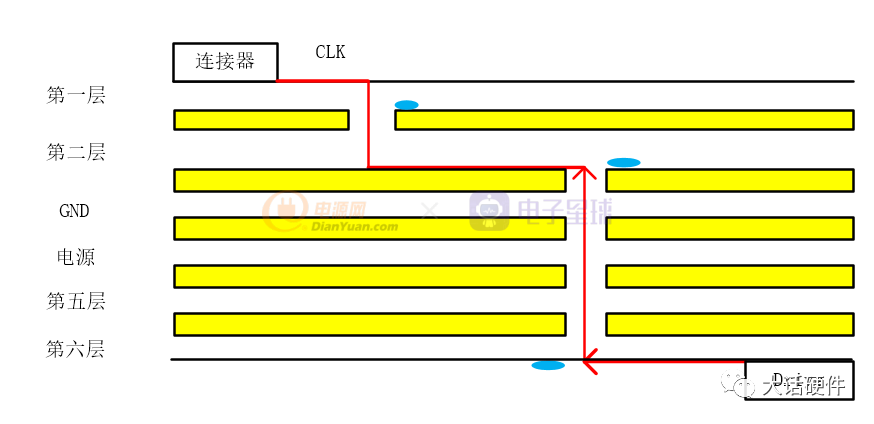

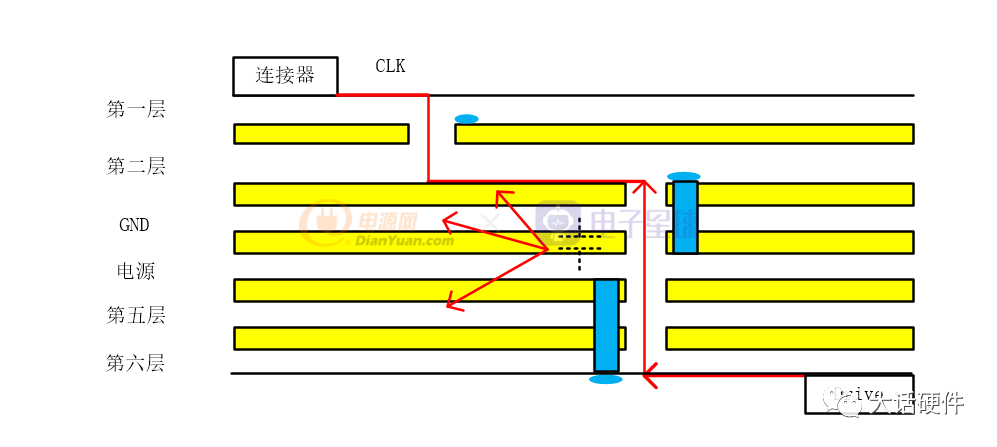

项目中遇到的EMC辐射超标问题,就归属于信号完整性中的辐射。出现问题后,特地的查看了PCB的走线,发现CLK在从第六层穿到第二层的时候,没有放置地过孔,而且在穿层的旁边还有其他的数据信号,因此可能还出现了串扰的问题。大概示意图如下。

检查到PCB上存在上面的问题后,进行了两个方面的调整:

(1)降低时钟输出端的驱动能力,从12mA降低到4mA

(2)增加12pF的电容,原理图设计时预留了电容工位

经过修改后再去测试EMC,辐射直接降了20dB,但是还是过不了ClassB。然而,从结果看两个措施的效果还是比较明显,其本质都是降低了信号上升沿的斜率。

信号从Drive出发,从第六层穿到第二层,再从第二层穿到第一层。时钟信号在整个路径中换了2次。穿层对高速的信号影响主要有两个方面:

(1)过孔寄生电感和电容,阻抗发生突变,容易出现反射

(2)过孔是容性负载,会降低信号的速率,在时序设计时可能会因为延时导致接收到时序裕量不足。

(3)过孔处信号的参考层发生改变,导致回流路径发生变化,从板材之间的寄生电容导致向外的辐射。

时钟信号在第一层走线时,是参考的第二层,在第一次穿层时,回流路径发生了改变,此时增加电源的过孔,可以引导CLK以电源属性为参考平面,阻抗小(当然,这里也可以直接打孔到GND上)。在第二层走线时,以GND为参考层。因此,回流路径在电源层和GND层发生了变化。

虽然电源和GND之间有很多去耦电容来降低电源的阻抗,但是寄生电容还是会存在(PCB板的固有属性)。因此,在该层会因为阻抗回流路径发生改变导致高频信号通过寄生电容往外辐射。

这也是为什么项目中设备辐射超标的一个原因,穿层时没有加过孔。回流路径以相邻的走线作为回流参考路径,因此就发生了串扰。而降低驱动能力和增加电容,可以降低信号的边沿上升速率,降低高频有效频率,既能够降低串扰的程度,也能降低往外辐射的高频能量。

5. 接地

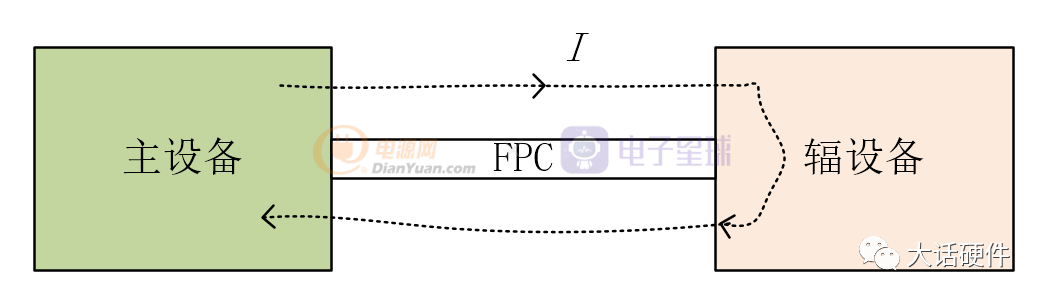

将驱动和增加电容措施导入后,还是满足不了EMC的要求。经过分析,发现设备在测试时,主设备和辐设备之间只使用一根FPC相连接,FPC上的地线数量比较少,推测应该是接地面积不够大带来的问题。

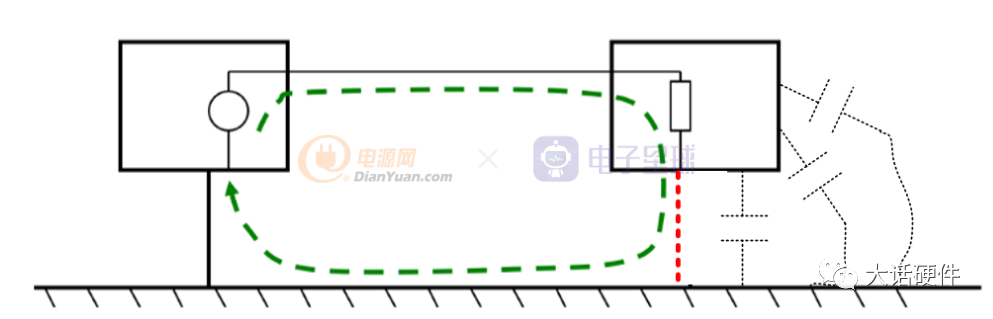

在解决EMC设计时,经常用到屏蔽,隔离,滤波,接地。其中接地在某种程度上来说,也是提供了一个良好的回路。

由于FPC线的地线比较少,高频信号在回流时会有一部分通过设备和地之间的寄生电容作为回流路径。这些寄生电容其实也是共模电流的返回路径。如下所示。

于是就将主设备和辅设备放在了同一块金属板上,同时在主设备和辅设备之间增加了两条较粗的金属导线。如下所示。经过上面的措施后,再去测试EMC后,ClassB等级直接通过,还多出来了5dB的裕量。

至此,项目中遇到的问题得到了完美的解决,看似一个很简单的辐射超标问题,但是从这个问题出发,还是有很多值得去挖掘的地方。

对上面的内容进行回顾,即知:时钟信号驱动能力较强,信号上升沿斜率较高,导致时钟高频奇次谐波往外辐射,RE测试超标;主设备和辅设备的的接地较差,辅设备传输到主设备的时钟靠寄生电容作为信号回流路径,导致向外的辐射较大。

6.总结

高速PCB设计中SI是非常关键的一环,其中涉及到阻抗匹配,信号参考路径,串扰,接地,过孔穿层等方面的问题。在设计的时候,要尽可能保证阻抗的一致性;尽可能保证回流面积最小;高速信号少穿层;走带状线和包地处理来降低敏感信号的辐射。通过这些手段来降低可能出现的EMC问题。

EMC的设计最好是在原理图设计之初就进行考虑,或者直接让EMC和射频工程师参与原理图的设计,避免等单板设计完出现问题之后再考虑如何整改。越是离产品发布的时间近,调整起来的成本就越高。