上上期我们提到了buck电路的开关的振铃波形,本质原因是LC的阻尼振荡。文章偏理论,那BUCK到底是怎么产生尖峰振荡呢?要想把这个问题搞清楚,也很是不容易,所以文章有点长。

问题

本期主要分析以下这两个问题:

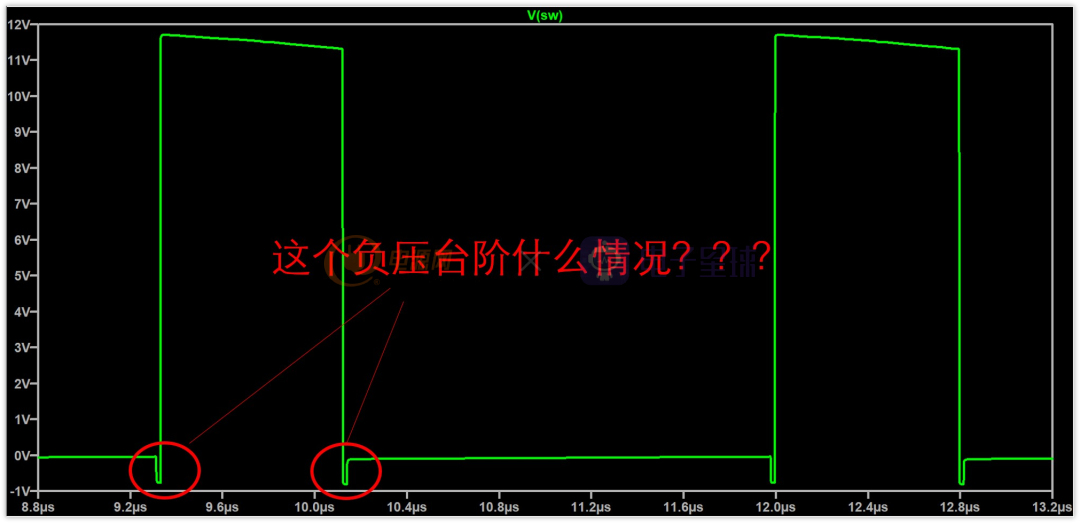

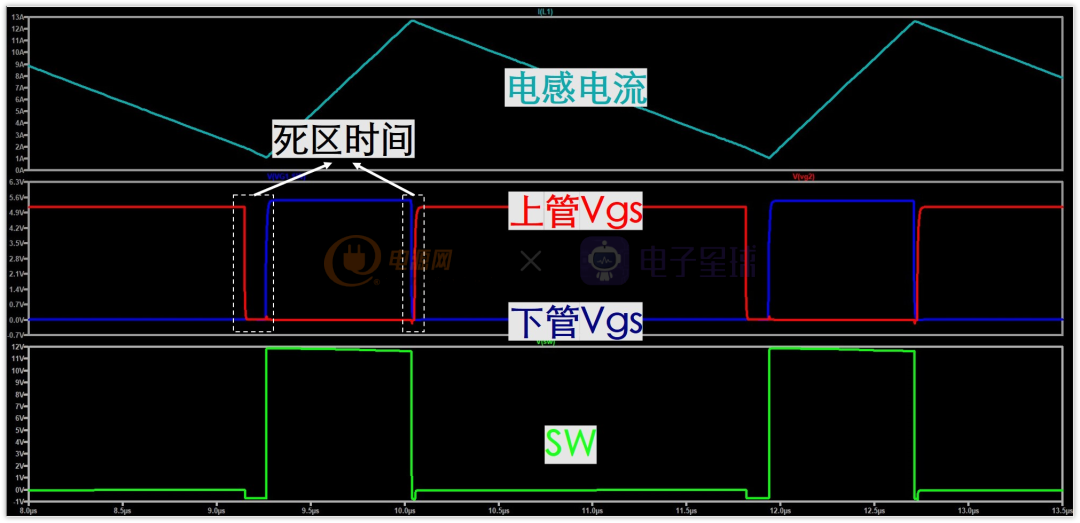

1、死区时间是什么?这里有个小台阶是什么情况?

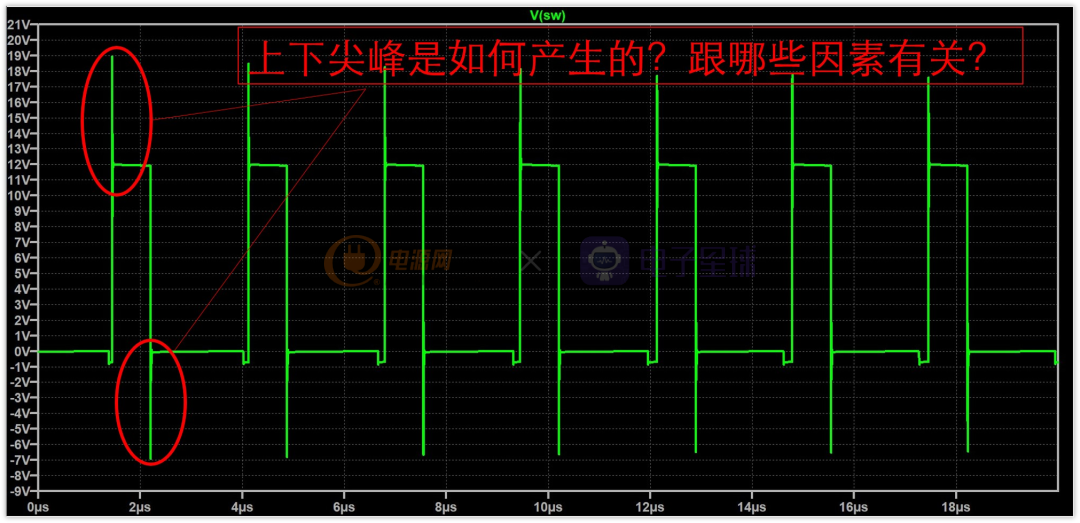

2、上下尖峰振荡是如何产生的?跟哪些因素有关?

理想的BUCK的SW波形

我们由浅入深,一步一步来,先看理想的开关SW波形—没有尖峰电压的波形。

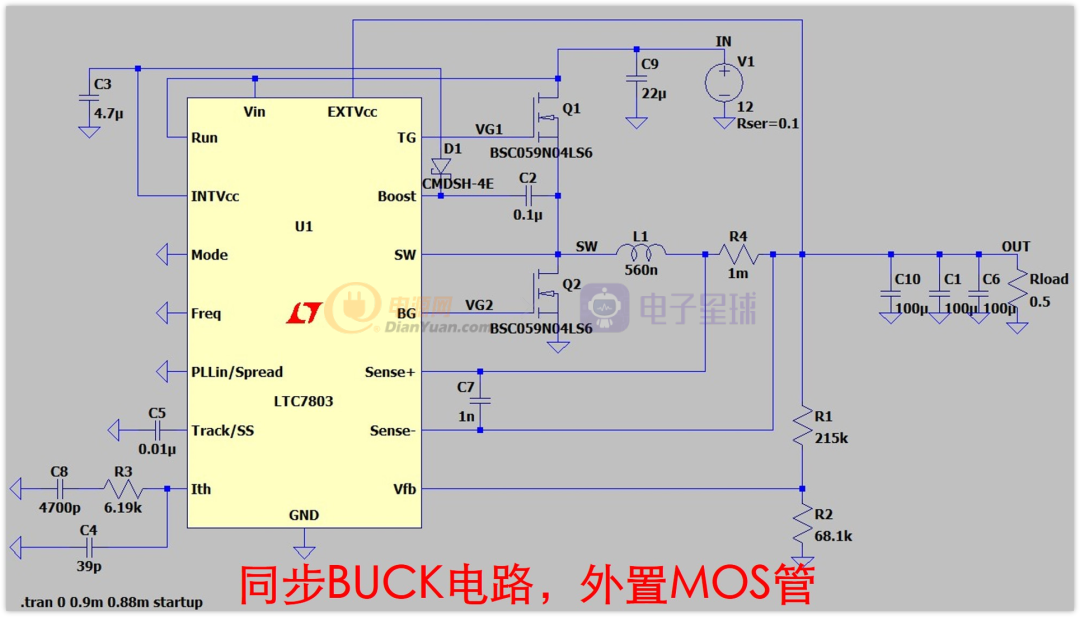

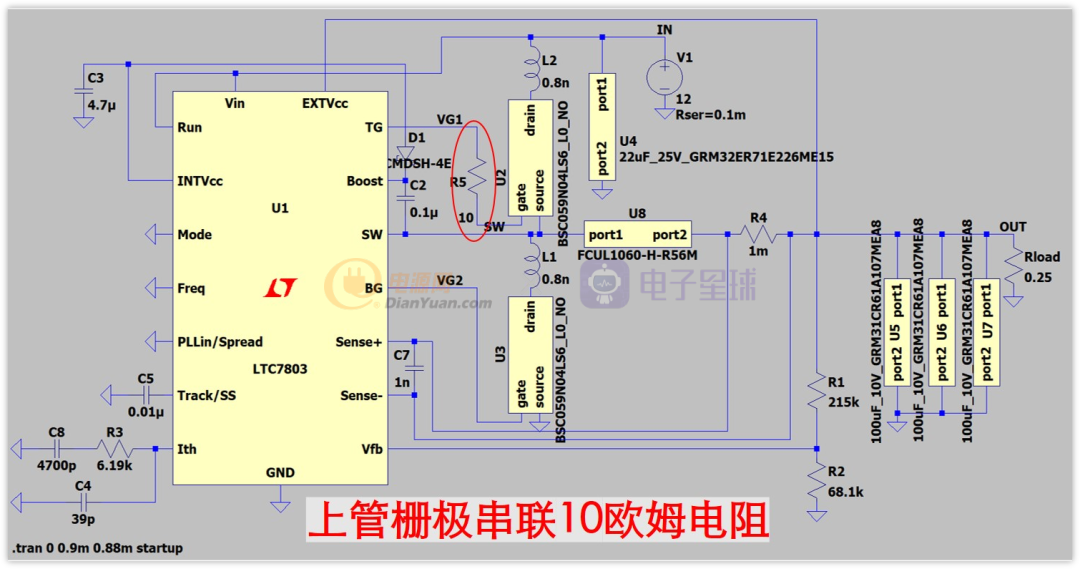

为了能更好的看buck电路各个点的电压电流情况,我选的电源芯片是没有内部集成开关管的,使用的是外置的MOS管,电源芯片型号为LTC7803。

使用LTspice进行仿真,电路图如下:

如果对BUCK的拓扑有了解的话,上面这个电路一眼应该就看明白了,是一个同步buck,没有用到二极管。

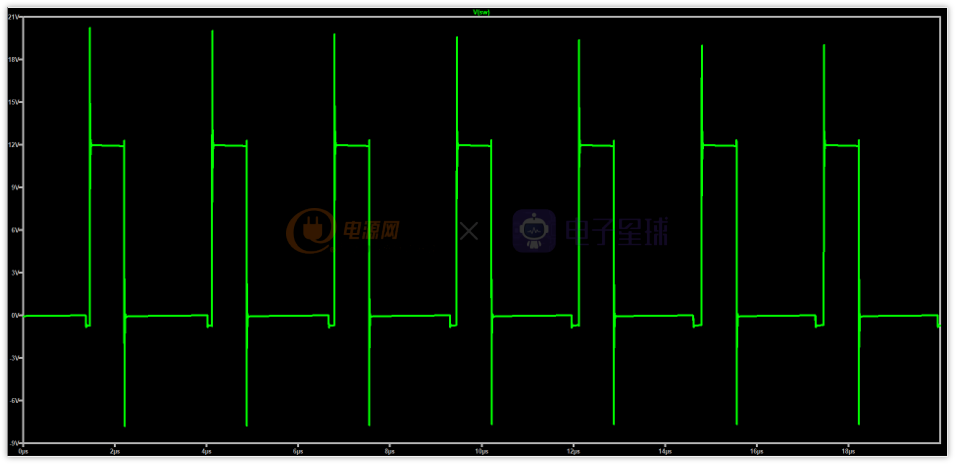

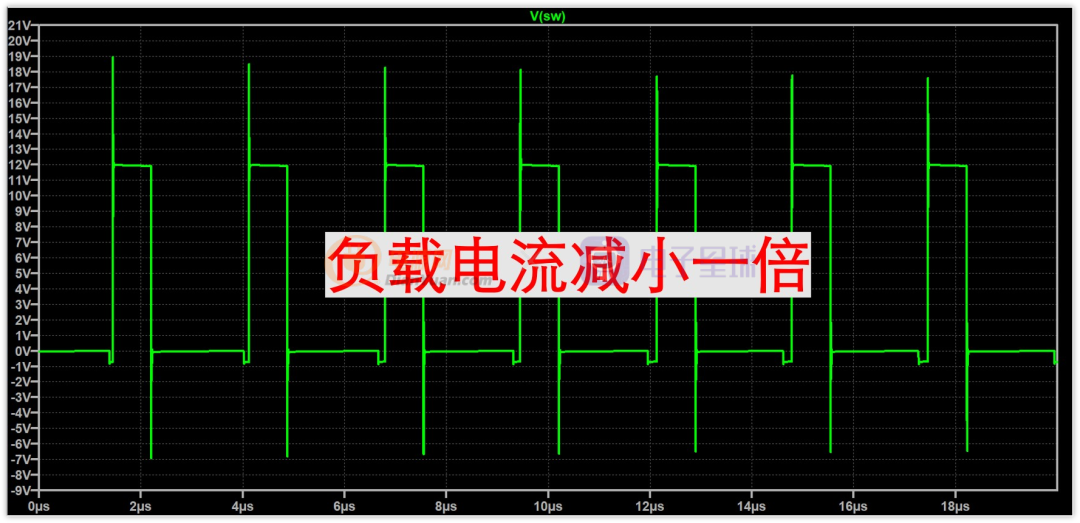

这个电路的输入是12V,输出是3.3V,负载等于0.5Ω,BUCK工作在连续模式。现在我们直接看电感前面SW的波形,如下图:

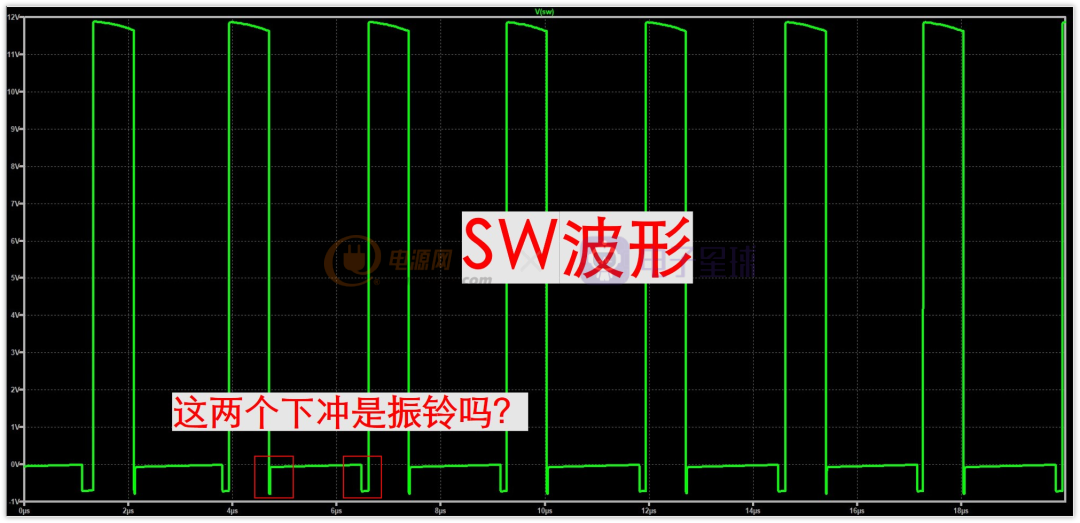

我们可以看到,这个波形很漂亮,看着就是非常好的矩形波,没有向上的振铃。

唯一美中不足的是,在底部有下冲。

这是怎么回事呢?是向下的振铃吗?

如果仔细观察的话,这个下冲的幅度大概是0.7V左右,也没有出现振荡波形,如此,猜测应该是二极管的导通电压。

为了验证这个想法,我们对比两个MOS管的驱动电压Vgs,然后看看电感的电流。

从上图,很容易看到,电感的电流一直都是正的(大于0),也就是电感的电流总是向负载那个方向流动的,并不会反向,并且,最小的电流也有2A。

但是呢,如果我们对比两个NMOS管的Vgs,会发现有同时为低的情况,也就是说两个管子同时都不导通,这一段时间就是死区时间。

为啥会有死区时间呢?

我们通常分析BUCK拓扑结构的时候,经常会认为只有一个管子导通,要不上管,要不下管(连续模式)。

而实际MOS管在切换导通状态的时候,MOS管必然会存在中间态-半导导通状态,半导通时的MOS管的导通电阻是变化的,很大到接近于0,如果两个管子同步切换,那么必然会出现都处于半导通状态的情况,回路电阻很大,这样功率电感电流就没法续流了。

所以呢,必须要考虑切换时其它的续流方式。

不仅如此,如果两个管子同步切换,稍微有一点不同步的话,那么肯定会存在两个管子都导通的情况,这样的话就相当于电源直接对地短路了,这简直是灾难。

现在看来,保险起见,干脆将时间错开,每次切换的时候,让两个管子都不导通一段时间,这样就绝不会出现两个管子同时导通了。

但是这样的话,我们必须想办法给功率电感续流。

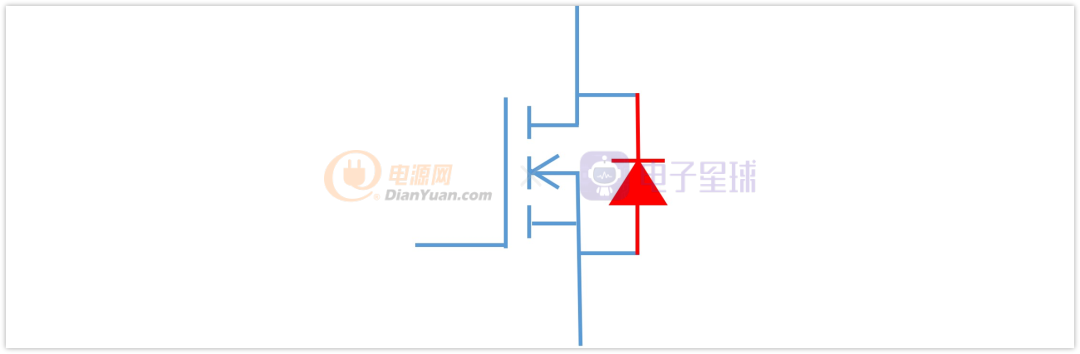

这个续流的方式很容易想到,MOS管是有体二极管的。在两个管子都关闭的时候,可以通过体二极管的续流。

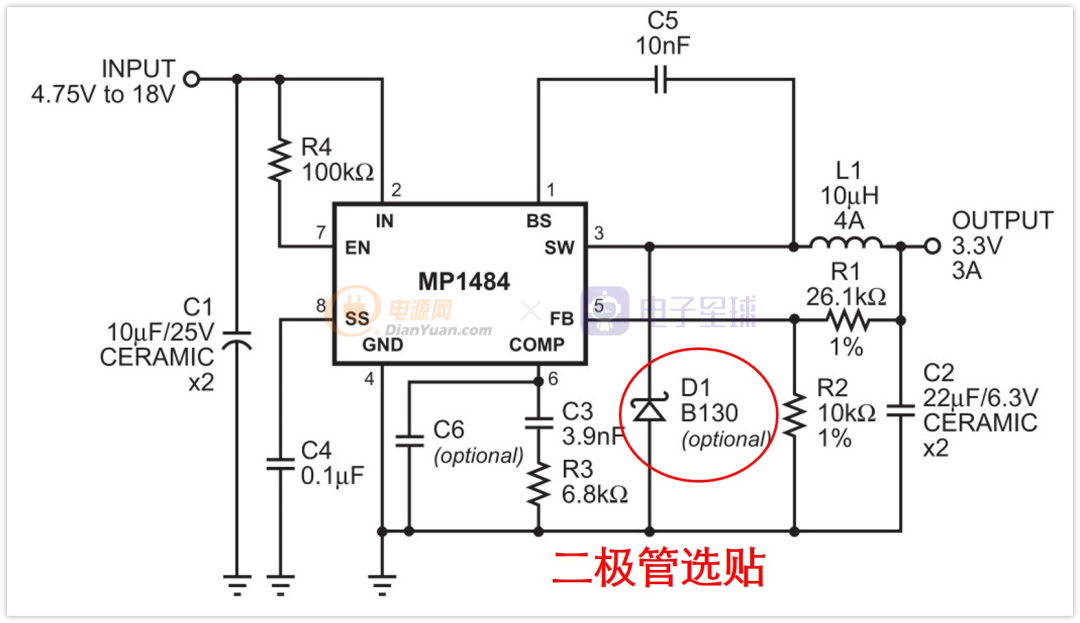

写到这里,我突然想起来,有些同步的DCDC芯片推荐的电路,会有二极管选贴一说(二极管可要可不要),比如这个MP1484的D1。

看到这个图不要以为这是一个异步buck,二极管D1是选贴的。

那这个二极管有什么用呢?

其实MP1484芯片手册里面也有写。

写的很明白了:

在上管和下管转换期间,电感电流主要从下管的体二极管流过。体二极管的导通电压比较高,可选用一个肖特基二极管并在SW和GND之间,以此来提升整体效率。

这个器件是硅芯片,那么显然,体二极管也就是硅二极管,导通电压自然要比肖特基二极管更高,因此使用肖特基二极管可以降低功耗。

不过我想这个降幅应该很是很有限的,因为上下管转换期间的时间非常短暂,只占开关周期很短的一部分时间,并且就算用了肖特基二极管,也还是有导通电压,只是比之前小一点而已。

以上是仿真波形,那实际电路也会在开关切换时有个0.7V左右的“下冲”吗?

我手头正好有MP1484的板子,于是我用示波器测试了一下,波形如下图:

奇怪的是,只在下降沿时出现了一个0.7V的下冲台阶,在上升沿时底部并没有向下的“下冲”台阶。

这是为什么呢?难道上升沿时上下管切换并没有死区时间?

为此,我猜测可能是负载电流的太小,并且上升沿时的死区时间比较短,而MOS管的D和S是有寄生电容的。

在开关切换之前,下管是导通的,等于接地,寄生电容两端电压约为0V,体二极管也是0V。

在切换时,体二极管刚开始也没有导通,所以是先对电容进行放电才能让电压变为-0.7V,此时二极管才会导通。如果死区时间太短,或者电感需要续的电流很小,那么可能在死区时间结束,电容都能提供足够的续流,电压下降很小。

为了印证我的猜测,因为没法加长死区时间,所以我改变了负载电阻,加大了负载电流,目的是为了让寄生电容提供不了足够的续流。

再次测试了一下,确实就能量到上升沿的死区时间了,如下图所示

可以看到,上升沿也有一个向下的冒尖,时间非常短,拉开示波器时间尺度发现大概是13ns(就不截图了)。而下降沿向下的冒尖时间大概是100ns。也就是说这个MP1484的两个死区时间分别是13ns和100ns。

从前面的仿真波形可以看到,在开关管切换时,死区时间会导致SW处出现0.7V左右的负压台阶,但是完全看不到尖峰。

而实测波形是有尖峰的,那这个尖峰是如何产生的呢?它的大小与哪些因素有关系呢?

我们接着看。

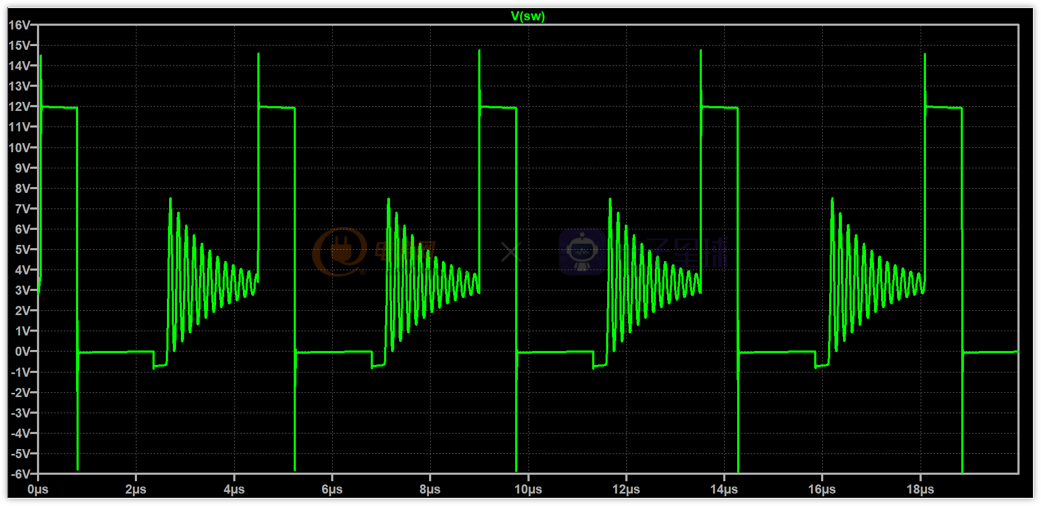

当然,我上图中实测的尖峰也很小,这是因为我做的板子已经尽量优化PCB了,所以尖峰效果不明显,如果板子做得差的话,可能是下面这样的。

拉开可以看到是高频振荡

我们知道,这个尖峰过高,意味着存在高频的剧烈变化的电流,会产生EMI的问题,同时,如果太高的话,可能会击穿内部开关管。

如果我们想要降低尖峰,最好的方式莫过于知道这个尖峰是如何产生的,然后对症下药。

BUCK的SW波形尖峰如何产生?

首先一个问题,仿真没有出现尖峰,是什么原因呢?

是因为器件模型不准确吗?也许吧,仿真使用到了集成芯片,NMOS管,电感和电容,那么如何确认这个问题呢?

更新功率电感模型

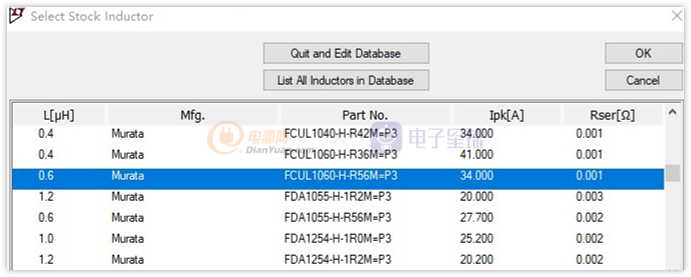

功率电感FCUL1060-H-R56M我使用的是LTspice库里面自带的。

里面的寄生参数很少,我只看到了Rser,寄生电容都看不到,因此我有理由怀疑这个模型不准确。

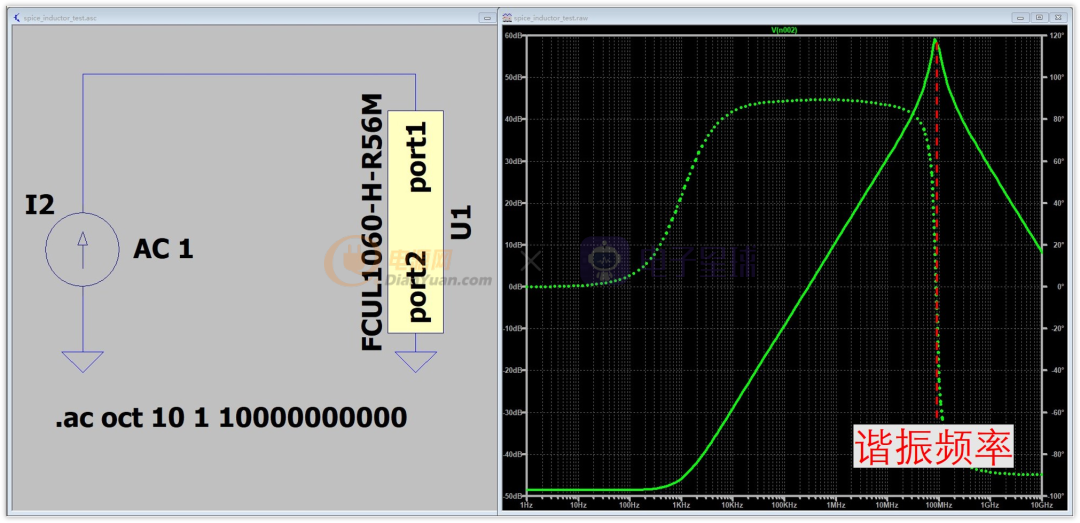

既然有怀疑,那就单独测试下这个电感的阻抗曲线。

测试方法很简单,用1A的电流源,采用AC频率扫描的方式,测量电感两端电压就可以了。

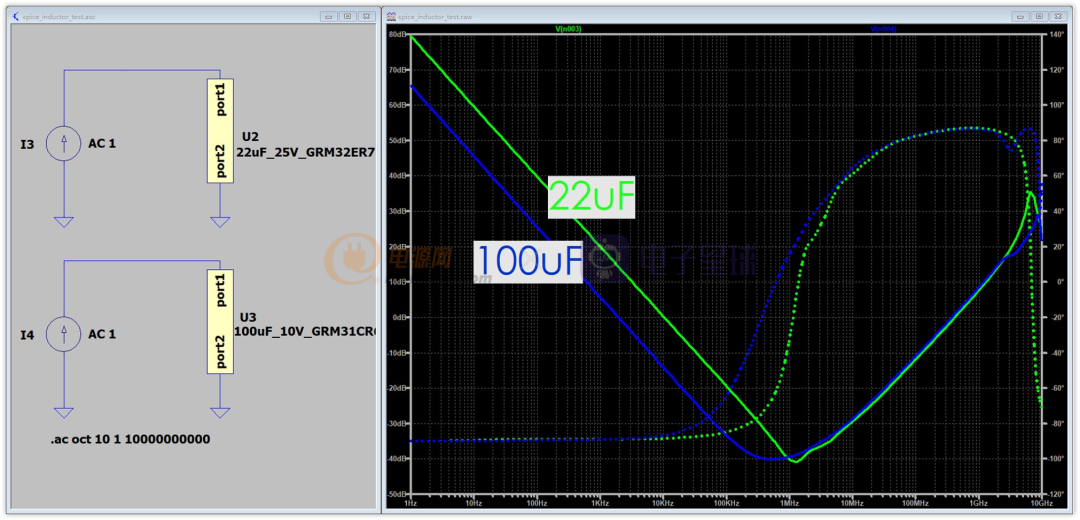

因为电流是1A,所以阻抗值与测得的电压相等,测试电路与结果如下图:

实线是阻抗,虚线是相位。

很显然,这个电感模型有问题,或者说是不够准确吧,因为阻抗随频率的增大而增大,连自谐振频率都看不见。

因此,我从村田下载了FCUL1060-H-R56M的Spice文件,重新构建模型,再次测试阻抗曲线如下图:

注意,上图中U1就是重新生成的电感模型,这个LTspice软件打开spice文件,然后自动创建的电感模型,所以在LTspice看来,它是一个模块,位号就成了U1,大家知道这是我生成的电感模型就好。

可以看到自谐振频率大概是100Mhz,这个模型应该是比较准确的,看起来是那么回事。

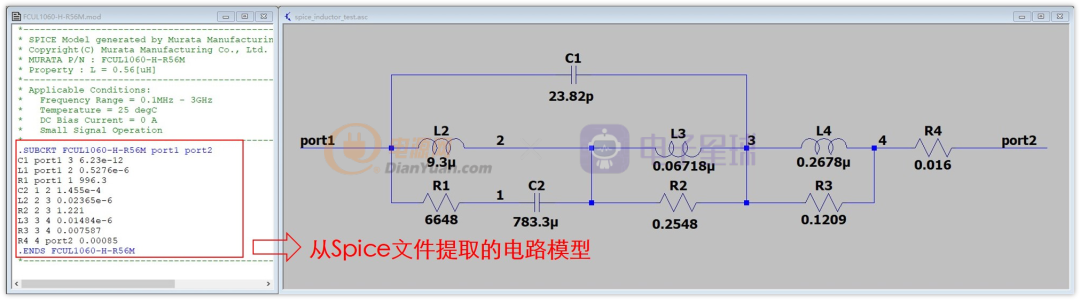

其实我们也可以从spice文件提取出这个电感的等效电路模型,spice文件本质来说就是个网表

上图是我根据spice文件画出的等效电路模型,仿真一下会发现阻抗曲线与前面的一模一样。

可以看到,这个官网提供的电感的spice文件还是挺复杂的,它创建的电感的模型应是更为准确的。

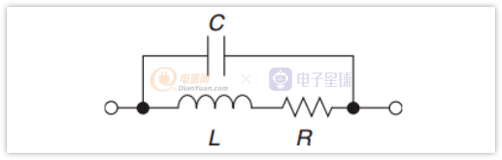

我们平时可能会说电感的高频模型是下图这样的。这也不能说错,只能说不够准确,因为我们平时也不需要那么精确,因此下图也就够用了。

而这次我们需要更精准的模型,所以用厂家官网提供的spice文件是最好的。

更新电容模型

同样的方法,我从官网下载我使用的22uF和100uF电容的spice文件,构成新的模型,测试阻抗曲线如下图所示

同样,实线是阻抗,虚线是相位

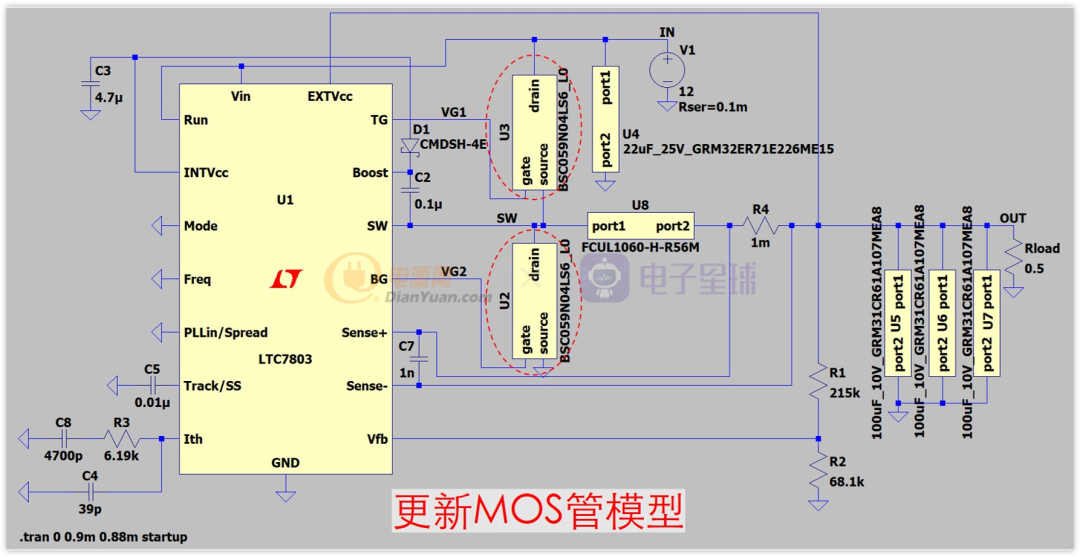

使用新的电感和电容模型,放入到原来的电路中,电路如下所示:

电感和滤波电容均使用了从官网下载的spice文件构建的模型,仿真SW的波形如下图:

与更新模型之前相比,基本没差别,这说明问题不在更新的模型上面。

LTC7803只是一个驱动芯片,产生Vgs信号,用作驱动MOS管开关,抛开开关速度不谈的话,应该跟尖峰关系不大。那就只剩下MOS管的原因了。

我们接着看

更新MOS管模型

从前面知道,LTspice软件自带的模型很可能是简易的,也就是说是不够精确的,NMOS管很有可能也是如此。

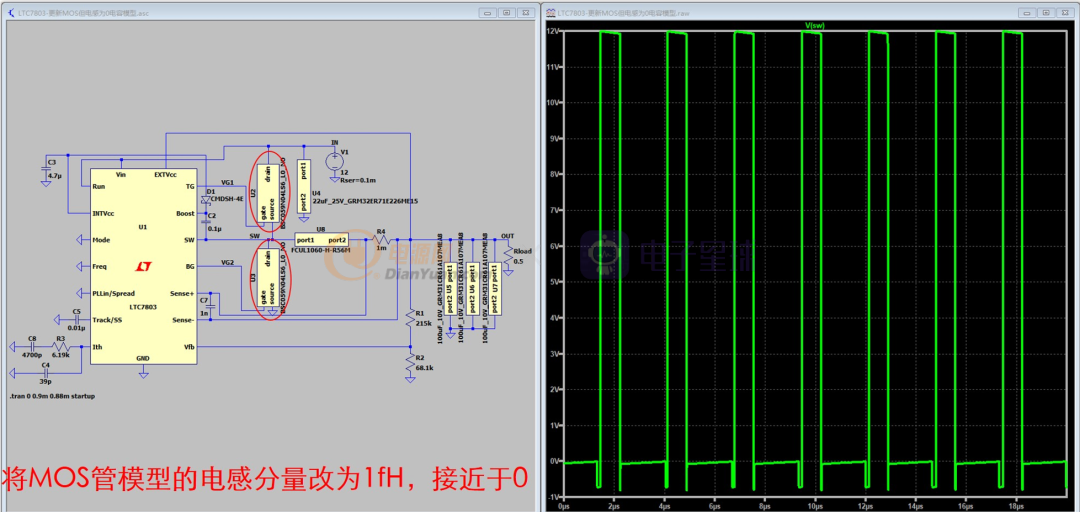

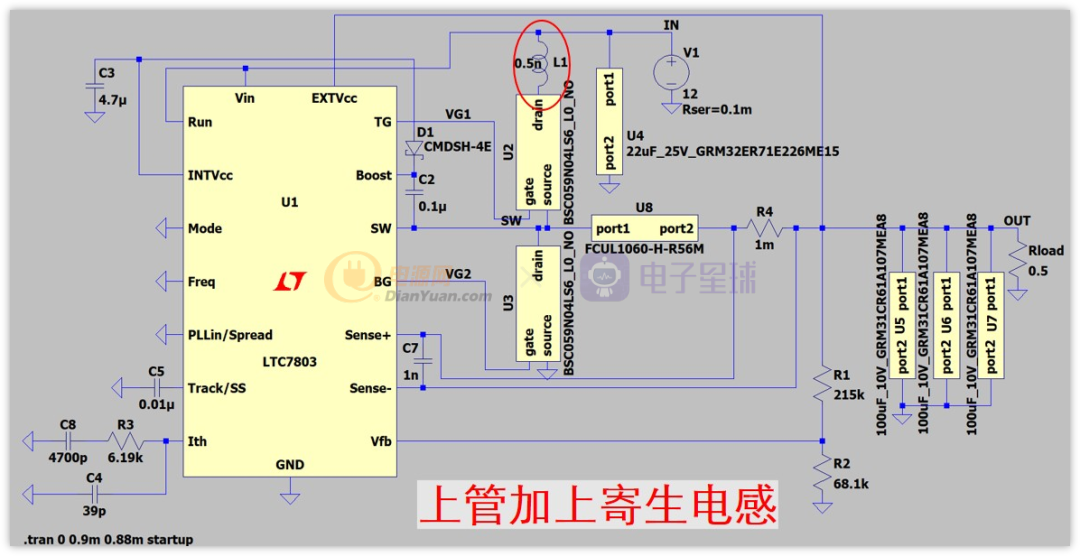

电路图中MOS管使用的是BSC059N04LS6,厂家是Infineon,我从官网上面下载spice文件,根据spice构建新的模型,换到前面的电路中,电路更新如下图:

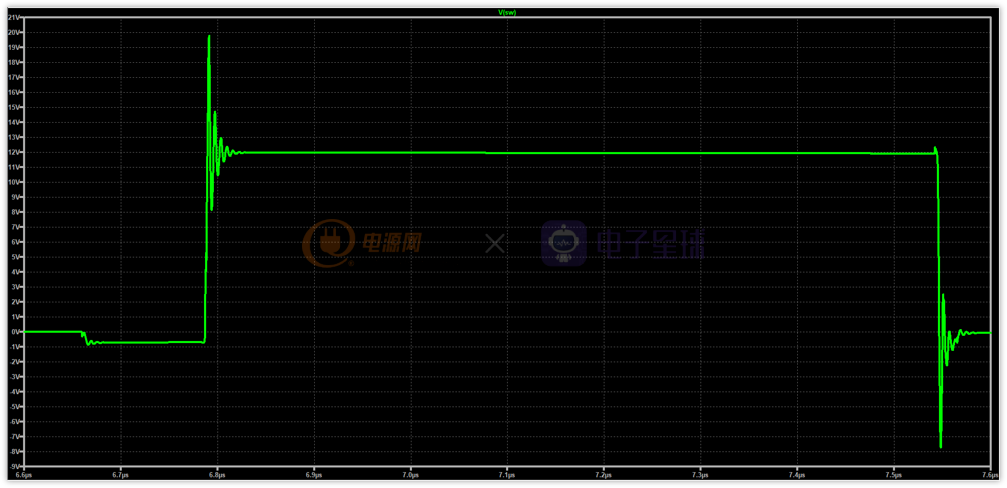

仿真SW波形如下图:

久违的振荡尖峰终于出现了。。。有一丝兴奋。。。

上下尖峰幅度差不多,大概有8V。

现在已经看到了类似于我们现实中的尖峰,那么问题来了,这个尖峰到底是怎么产生的呢?目前看到的就是我们换了一个MOS管的模型就出现了。

这个官网提供的MOS管模型到底有什么不同呢?

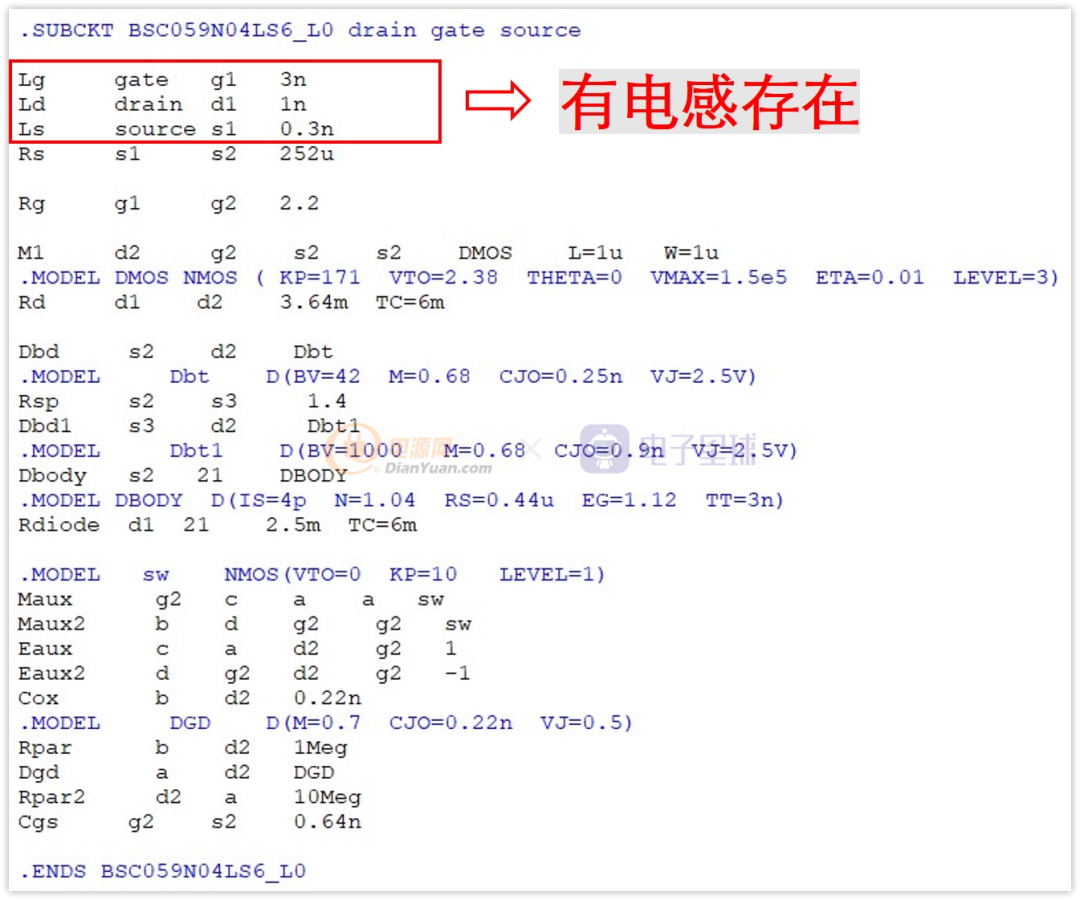

上图是官网下载的MOS管的spice文件,需要特别注意的是有三个参数,Lg,Ld,Ls这是3个电感分量。

它的意思是,在MOS管的G,D,S极上面分别串联了电感。

因此,我猜测就是因为引入了这3个电感分量,所以才有了振荡尖峰。

之所以有此猜测,是因为振荡尖峰产生的原因一般就是因为LC阻尼振荡,MOS管的模型一般都不会少了电容,而电感却不一定有。

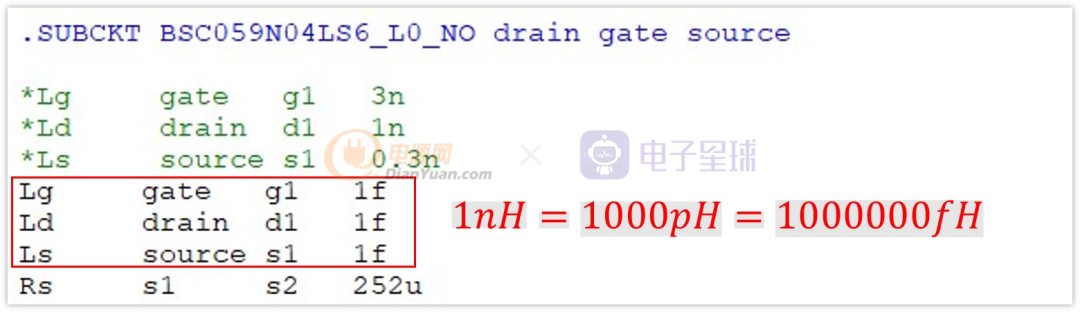

为了验证到底是不是这三个电感的原因,我将Lg,Ld,Ls都改成了1fH,1fH等于10的负六次方纳亨。其实我是想改为0的,只不过改为0后仿真出现不收敛的情况,因此就改成了1fh,这也足够小了。

将电感参数改为1fH。

创建一个新的模型,替换到电路中,再次仿真一下。

会看到SW的尖峰没有了,所以可以肯定的是,MOS管上面串联的电感是产生尖峰的必要条件。

那问题又来了?

能不能直接从拓扑结构分析下,电感是产生尖峰的必要条件?

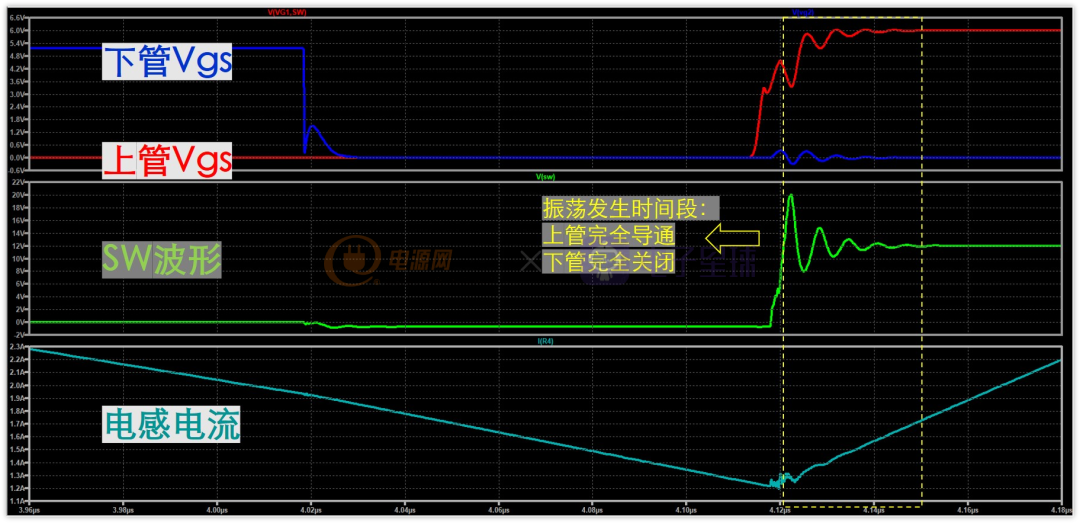

先来看产生尖峰的时候,两个开关管的开通与关闭情况。

以上升尖峰为例。

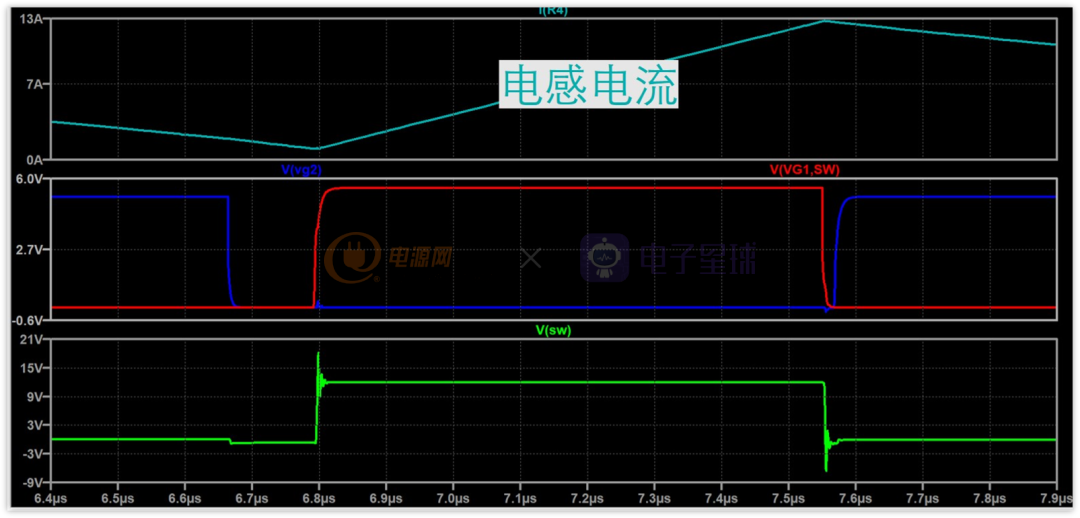

红色的波形是上管的Vgs电压,蓝色的是下管的Vgs电压,绿色的为SW电压,最下面的为电感电流。

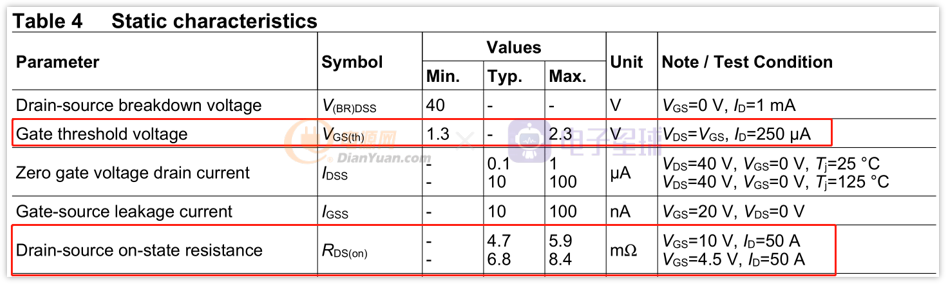

MOS管使用的是BSC059N04LS6,我们查看芯片手册,会发现在Vgs的开启门限最大是2.3V。而在在SW处产生尖峰振荡的时候,Vgs都在3.5V以上,也就是说上管已经完全导通了,而此时下管是完全关闭的,这可以从上图中的波形中看出来。

也就是说,上尖峰振荡的时候,上管完全导通,下管完全关闭,不是在开关开始切换,半导体的时间段。

上管完全导通说明什么呢?

尽管上管有寄生电容,但是此时上管完全导通,导通电阻只有几毫欧,所以这个寄生电容也被短路了。

如果没有串联的寄生电感存在,那么就相当于是输入电源直接通过几毫欧的电阻接到了SW管脚,而输入电源电压可以认为是基本不变的。

所以没有电感的话,SW处不可能产生高达8V的尖峰振荡。

只有中间存在寄生电感,才会因为电流变化非常快,足以在电感上面产生8V的电压。

那具体过程是怎么样呢?

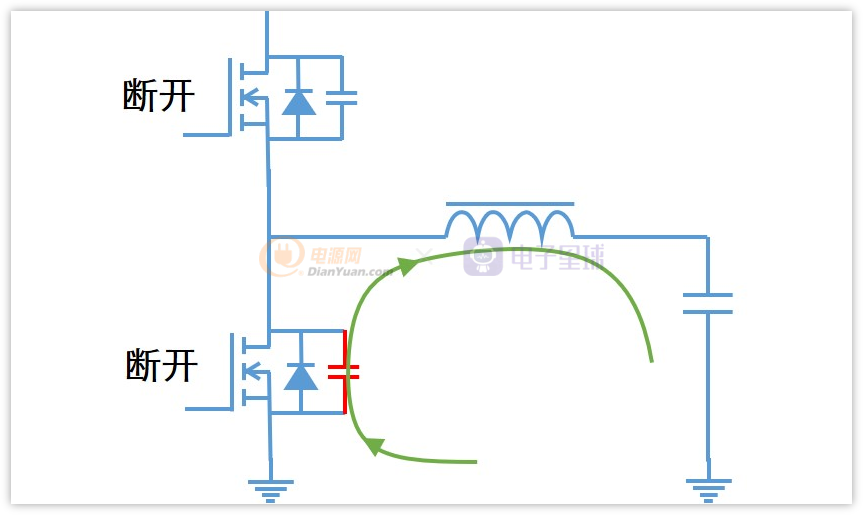

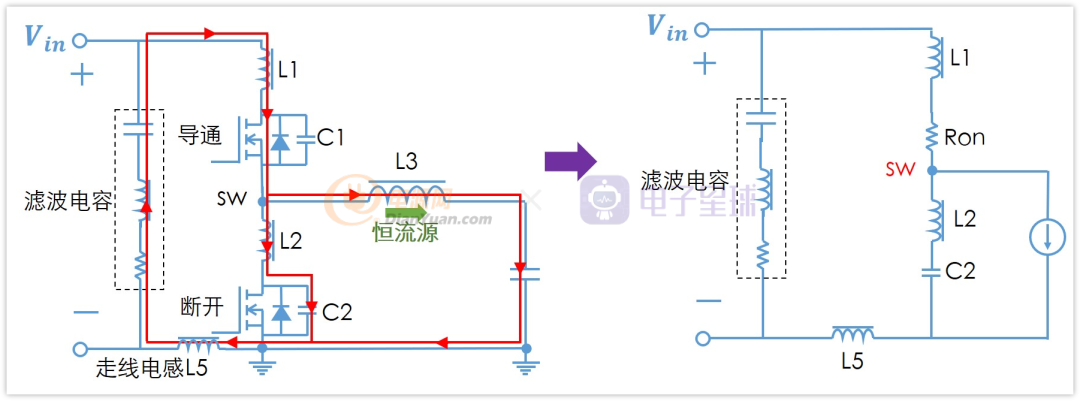

在上管导通之前,功率电感从下管的体二极管续流,下管的寄生电容C2电压为0。

在上管导通之后,其导通电阻只有几毫欧,因此C1相当于被短路。下管完全断开,但是上面有寄生电容C2。

我们看SW节点,因为我们现在分析的是很小的一段时间,所以功率电感此时可以看作恒流,电流方向流向负载。

可能有人会认为功率电感也有寄生电容参数,能走高频电流,所以不能看作恒流源。关于这一点,其实我也怀疑过,这也是我要更新模型的原因。

不过查看功率电感的电流波形,在振荡时间段,确实是基本不变的。

另外我们知道,振荡频率是百兆量级的,而我们查看这个功率电感的阻抗曲线,其自谐振频率就在100Mhz左右,此时阻抗最大,阻抗达到了上千欧姆,所以它是无法通过高频的电流的。

我们继续。

我们知道,SW节点处稳定之后基本等于电源电压。

在开关导通之后,SW从0V电压开始上升,那么C2在被充电,电源需要通过L1提供功率电感L3的续流以及对C2的充电。

也就是说:L1的电流=功率电感L3的电流+C2的充电电流

随着SW节点的电压升高,一直到SW电压和Vin一样,这时候电压为什么不停止上升呢,直接达到稳态呢?

这是因为L1的电流=功率电感L3的电流+C2的充电电流,也就是说在SW电压达到Vin之前,L1的电流>功率电感电流。

在SW电压达到Vin时,如果电压不再上升,那么意味着C2不再被充电,即流过C2的 电流为0,那么L1的电流=功率电感电流。

而事实是L1的电流>功率电感电流。

所以在SW达到Vin电压之后,SW电压继续上升,会大于Vin,此时电感L1两端的电压反向,电流开始减小。

随着SW电压上升,那么C2继续被充电。

当L1的电流减小到和功率电感一样的时候。

因为L1的电流=功率电感L3的电流+C2的充电电流。那么意味着C2的充电电流为0,就不能通过L1接着对C2进行充电了。

此时SW电压达到最高,但它也不能保持住,为啥呢?

因为此时SW的电压大于Vin,电感L1的电流要继续减小。而功率电感L3的电流不变,所以功率电感必须从C2抽取电流,这意味着C2开始放电。

C2开始放电后,SW电压开始降低,然后SW的电压降低到Vin,此时L1的电流达到最小。再之后C2继续放电(因为L1电流小,不足以提供功率电感的续流),SW电压继续降低,L1两端电压反向,L1的电流开始增大,直到L1电流大小达到功率电感的电流。

此时C2停止放电,SW电压达到最低,然后C2开始被充电,SW电压开始升高,如此循环往复,SW处电压看起来就是振荡了。

当然整个过程中因为有电阻分量,所以振荡幅值是越来越小的,本质就是LCR阻尼振荡。

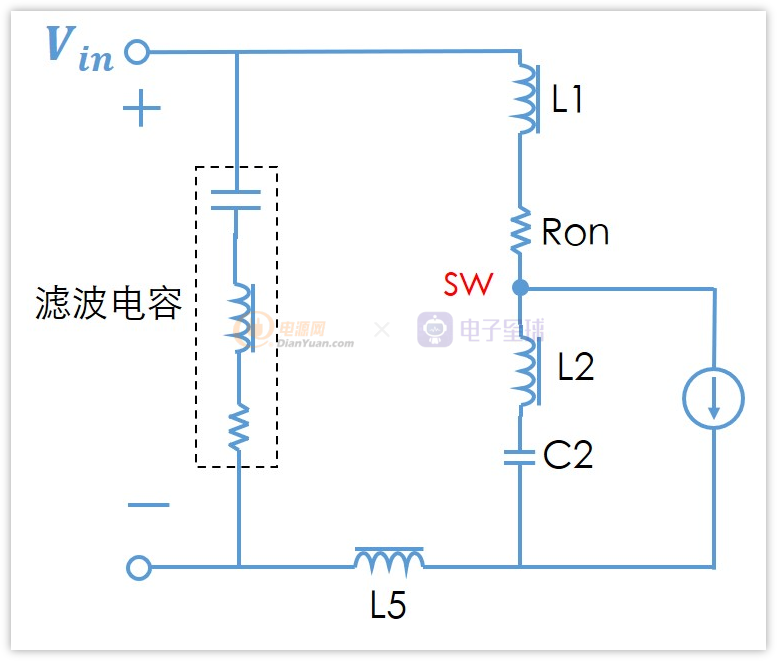

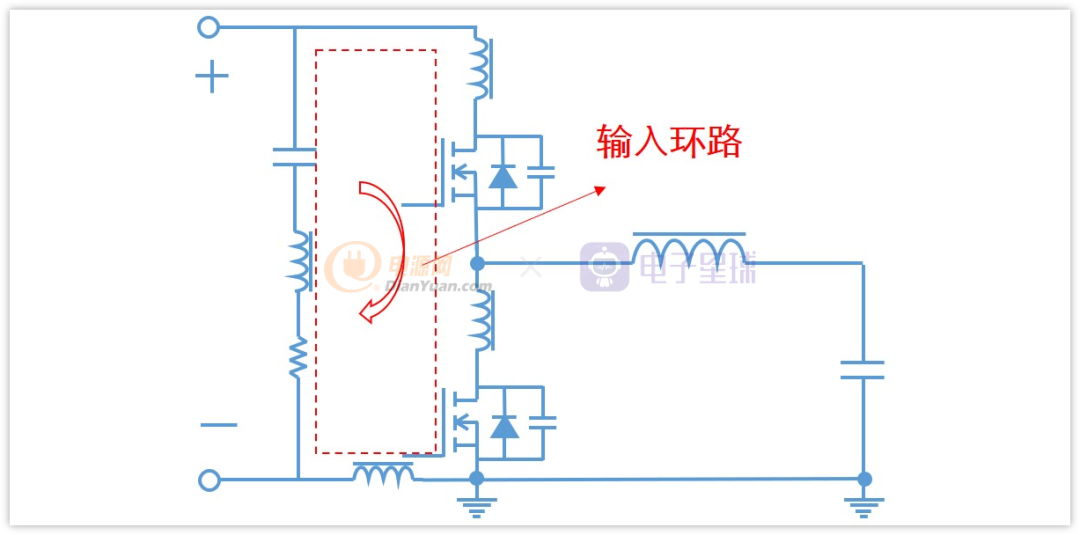

简易的等效电路如下:

滤波电容的寄生电感,电阻,还有回路中的走线电感,电阻,都是处于振荡回路。

上管到输入滤波电容之间的电感量对上升沿尖峰的大小起了决定性的作用,因为尖峰的大小基本就等于L1的两端电压(忽略Ron两端的电压)。如果没有L1的存在,振荡虽然还存在,但是SW处的电压基本是不变的,就越等于Vin。

很明显,如果寄生电感L1比较大,那么产生的尖峰电压肯定是越大的。

那负载电流大小与振荡尖峰的大小有关系吗?

关系是有的,负载电流越大,那么意味着功率电感电流越大,在SW从0上升到Vin电压时,寄生电感L1得到的电流也越大,L1获得的用于振荡的能量也是越大的。用于振荡的能量越大,那么振荡尖峰自然也就越高。

也就是说负载电流越大,参与振荡的能量越多,那么产生的尖峰也是越高的。

同样的,开关速度越快,寄生电感电流上升的速度也越快,在SW从0上升到Vin电压时,寄生电感L1得到的电流也越大,参与振荡的能量也越多,所以尖峰也越高。

以上就是上尖峰的分析过程如果从文字描述的过程看,相当的复杂,下尖峰也就不分析了,疲了。。。。

我们来看点轻松的,直接看实验过程。

如何看寄生电感的影响有多大呢?

前面我们不是将Lg,Ld,Ls三个参数改成接近于0的值,重新构建模型,尖峰就消失了么?

我们继续使用该模型,然后手动在电路上面串联电感,然后修改不同的电感值,看看尖峰的大小。

1、只在上管串联0.5nH电感,下管没有串联电感,负载为0.5Ω,电压为3.3V,那么负载电流为6.6A。

可以看到此时上尖峰最高为4V,而下尖峰是没有的(负的电平为死区时间的0.7V体二极管压降)

这说明上尖峰的大小是由上管的寄生电感决定的,下尖峰的大小是由下管的寄生电感决定的。

2、将上管串联0.5nH电感改为0.8nH

可以看到上尖峰最高为8V,比原来4V高了不少,这说明电感越大,尖峰越大

3、我们顺便还可以改变一下负载,看一下电流对尖峰的影响。

保持上管串联0.8nH,负载电阻减小一倍,即负载电流增加1倍,为13.2A。

可以看到,上尖峰达到了19V,增大了很多。这说明了负载电流越大,尖峰越大。

这跟前面分析是一致的,负载电流越大,上下管切换的时候,寄生电感获得的参与振荡的能量越高,尖峰也越大。

4、我们去掉上管的串联电感,下管串联0.8nH,负载电流还是13.2A

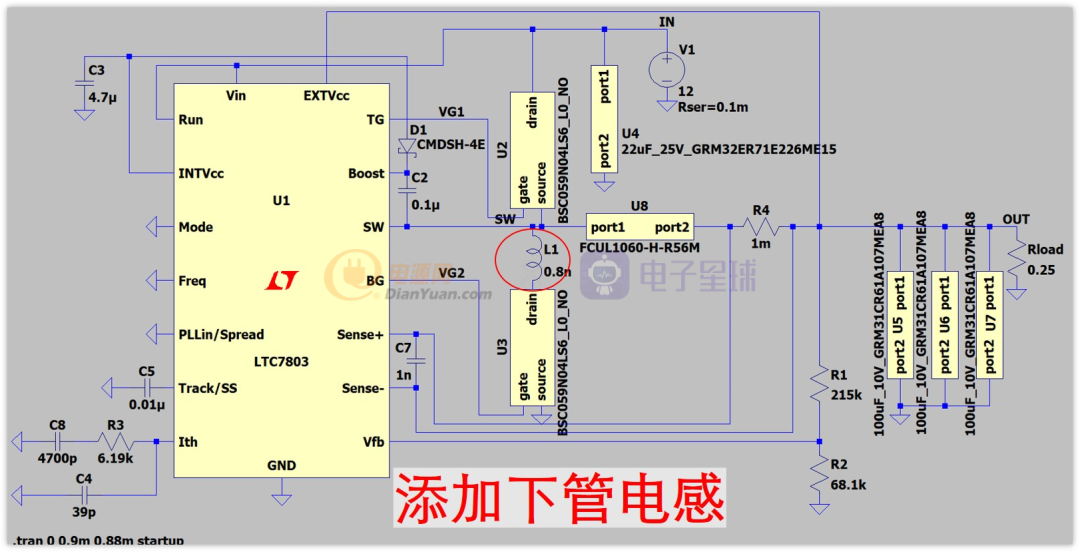

电路图如下图:

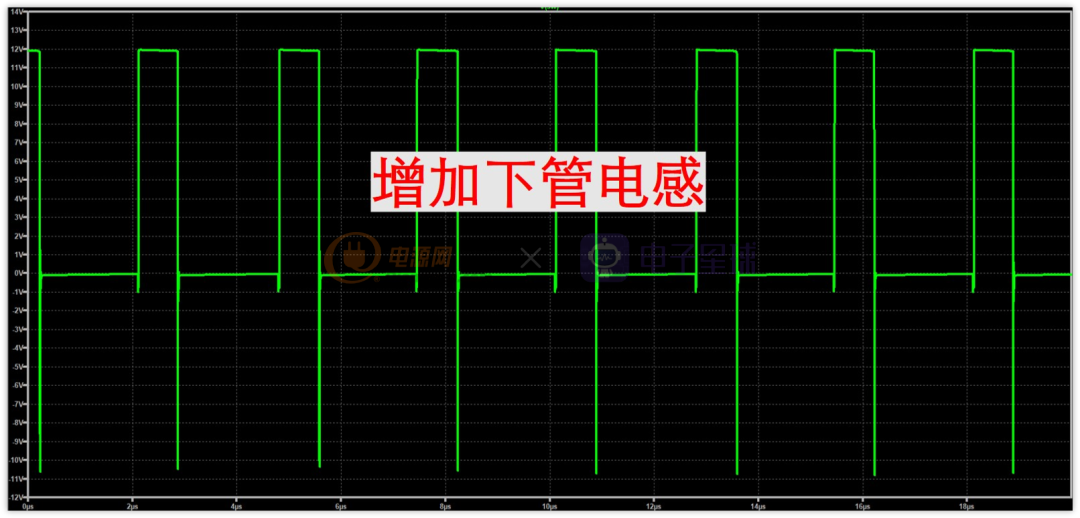

仿真的SW波形如下图:

可以看到,没有上尖峰,下尖峰大概有10.5V,这说明了下尖峰的大小是由下管的寄生电感决定的。

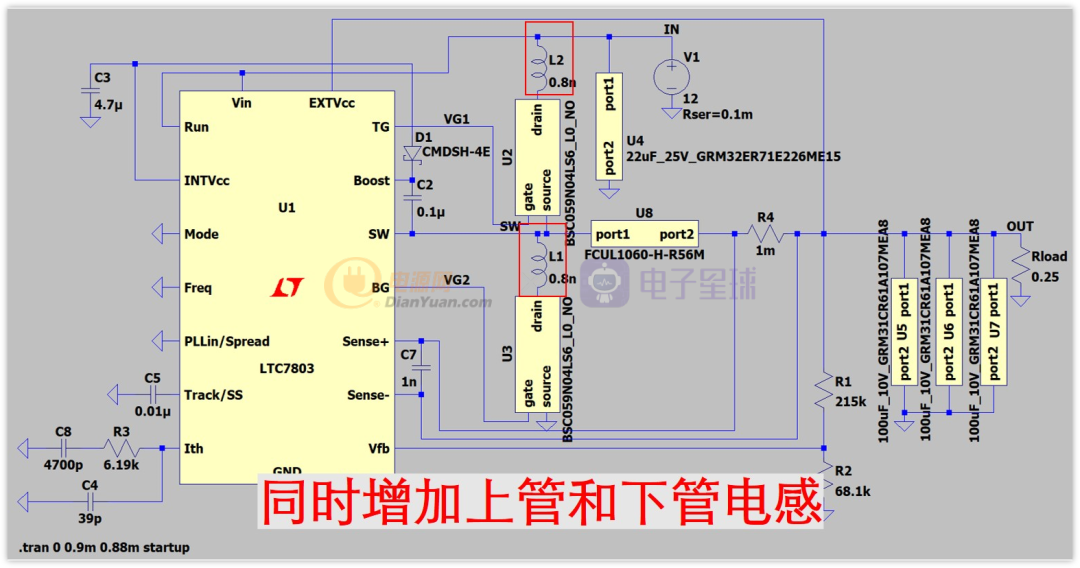

5、我们给上管和下管都加上0.8nH的电感,负载电流还是为13.2A

电路图如下:

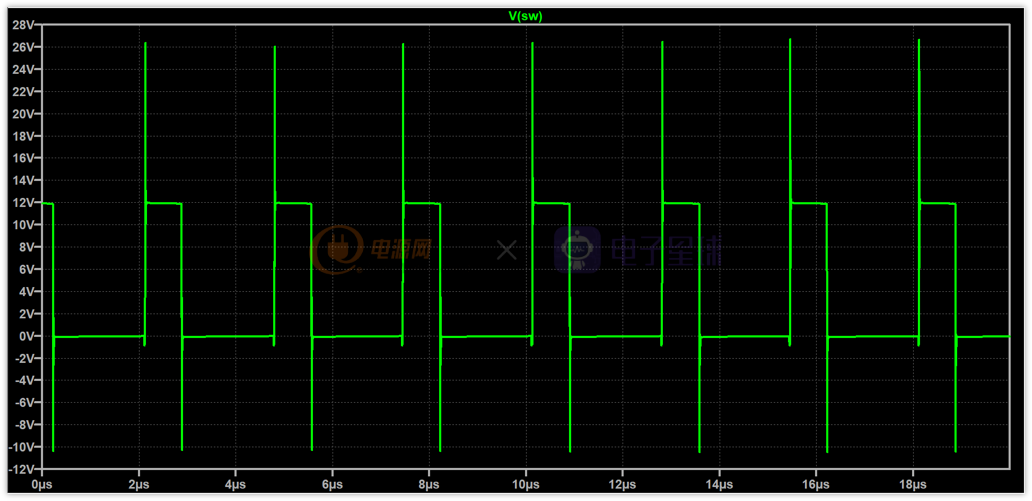

仿真的SW波形如下图:

这时,可以看到,上下尖峰同时存在。

上尖峰是14V左右,下尖峰是10V左右。

这里又存在一个问题了。。。

为什么电感都是0.8nH,下尖峰的值更小?

我同时查看Vgs与SW波形,发现,上尖峰振荡发生在上管导通,下管不导通的时间段

而下尖峰发生在死区时间,上下管子都不导通

死区时间,意味着功率电感的续流是通过下管的体二极管,我们知道体二极管有压降,会损失能量。

所以说下尖峰比上尖峰多了一个体二极管的损失能量,所以尖峰更小。

寄生电感相同时,那么下管尖峰一定比上管小吗?

我们接着看

6、上管和下管都加0.8nH电感,负载电阻增大到0.5Ω,负载电流减小一半,为6.6A

可以看到,电流改小之后,上下尖峰都减小了,这也与前面的分析一致。

不过现在上下尖峰都是7V左右,二者差不多,并没有像前面说的下尖峰更小,这又是为什么呢?

我们再打开功率电感电流和Vgs的波形

上升沿尖峰时,功率电感电流是最小的,功率电感续流需要走上管,也就是说最终上管的0.8nH所需要的达到的电流较小,这会导致尖峰比较小。

而下尖峰时,功率电感电流是最大的,功率电感续流需要走下管,也就是说最终下管的0.8nH所需要的达到的电流较大。这会导致尖峰比较大。

所以,上下尖峰的大小谁大谁小,视情况而定。

我们极端一点,如果这个buck工作在断续模式,那么意味着上管导通时,功率电感电流是0,也就是说功率电感需要通过上管续的电流为0,那岂不是上尖峰应该消失呢?

我们来看一下。

7、将负载电阻改为1Ω,负载电流为3A,buck进入断续模式,我们来看看上尖峰是否为0

SW波形如下:

可以看到,上升沿尖峰并没有消失,好像与前面的分析不符啊,什么情况呢?

我们看一下上管0.8nH的电感电流,功率电感电流在上升沿时的情况。

可以看到,在上升沿时,功率电感的电流确实为0,但是上升尖峰还是存在,因为0.8nH的电感是有电流存在的。

那这是为什么呢?

这是因为的MOS管的DS的两端有寄生电容Coss,在上升沿之前,下管导通,Coss的电压为0V,而导通之后,最终Coss的电压是为12V的,这期间就构成了LC的振荡电路。

除了以上这些,尖峰的大小还与哪些因素有关系呢?

很容易想到的就是MOS管的开关速度,这个我们可以在栅极加电阻,来增加导通时间。导通时间增加,在开关管切换的时候,

8、开关速度对尖峰大小的影响

在上下管串联0.8nh电感,负载电流为13.2A,MOS管栅极没有串联电阻时。

MOS导通时间大概是7ns左右,上尖峰高度为14V

我们在上管栅极添加10欧姆电阻,电路如下

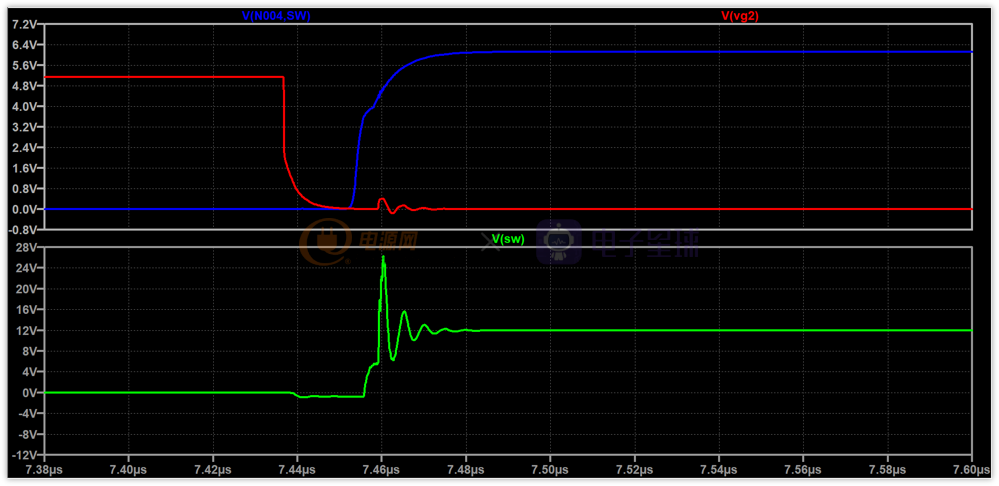

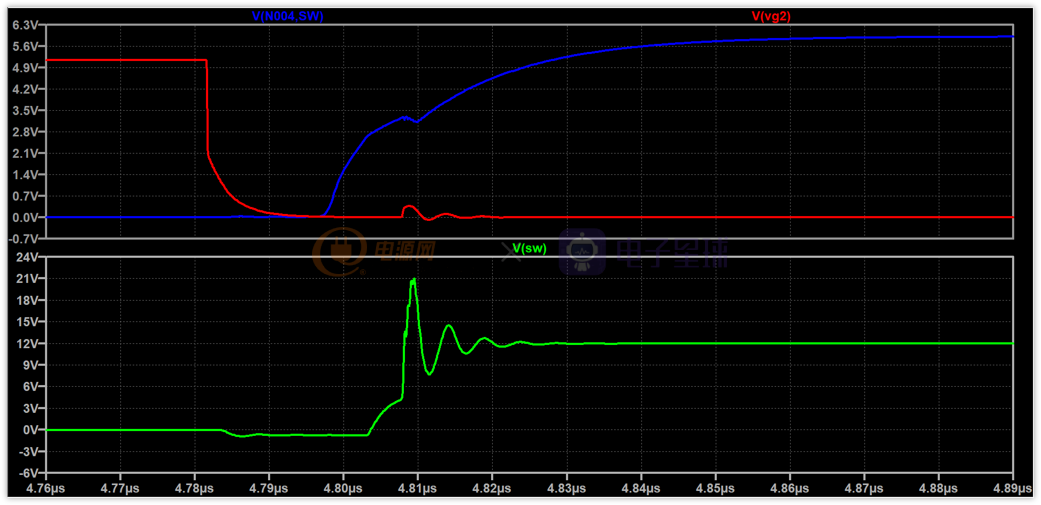

运行,Vgs的电压与SW波形如下图。

可以看到,上MOS管栅极加了10欧姆电阻之后,从截止到导通的时间大概是13ns,比原来7ns时间更长,另外,SW的尖峰幅度也从14V降低了到9V

总的来说,BUCK上下尖峰的产生,与线路中的电感是密不可分的,电感越大,尖峰也就会越大。如果上下管没有电感的存在,是产生了尖峰的。

除此之外,还与开关管的开通速度也有很大的关系,开通越快,产生的振铃尖峰也越高。

这个我估计有人就说了,你废了半天牛劲,整出一堆没用的。

我们一般用的BUCK芯片都是集成的,内部集成了MOS管,我们在线路上面也不会额外加电感,有什么用呢?

实际电路中的电感是如何存在的?

前面做的一系列实验,那个0.5nH/0.8nH电感,可以看作是线路中的寄生电感。

实际电路很复杂,芯片内部引线电感,PCB走线电感,滤波电容的等效ESL等等。

当然,芯片内部我们没法改变,我们能改变的就是输入滤波电容的位置,芯片好好接地。通过优化PCB Layout降低走线电感量。

可能有人就说了,走线电感,听着这么玄乎,真的有这么大的影响吗?

确实是真的。

我上面仿真电路放的电感最大也才0.8nH,可以看到,引起的尖峰已经很大了。

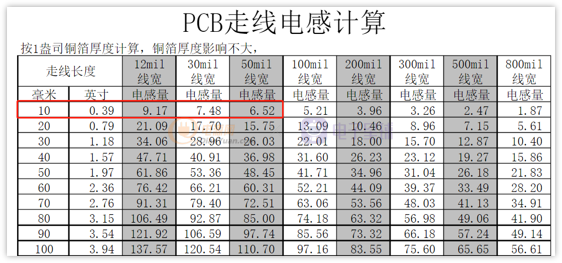

而0.8nH的电感量什么概念呢?到底大不大?

如图所以,1盎司铜厚,线宽50mil,走线长度10mm的电感量是6.52nH。可能我们输入滤波电容会放得很近,但是一般距离也有个2mm左右吧,这样走线电感也差不多1nH。

所以呢,在研究振荡尖峰这个问题时,走线电感是不能忽略的。

而事实确实也是如此,我们用示波器测量实际电路的时候,都是会量到这个振荡尖峰的,只不过有大有小而已。

在设计中,选定了BUCK芯片之后,我们能做的其实不多。

就是尽可能的将输入滤波电容放得离芯片更近,巴不得直接将输入滤波电容跨接在芯片的输入管脚和地管脚上面,这样输入环路最小。

这一点也应该是PCB layout里面最重要的一点吧。

有的DCDC芯片的管脚分布并不好,PCB layout时可能需要将输入滤波电容放到PCB板背面去,这个时候就需要特别注意了,过孔一定要尽可能多打几个。

为啥要多打过孔呢?

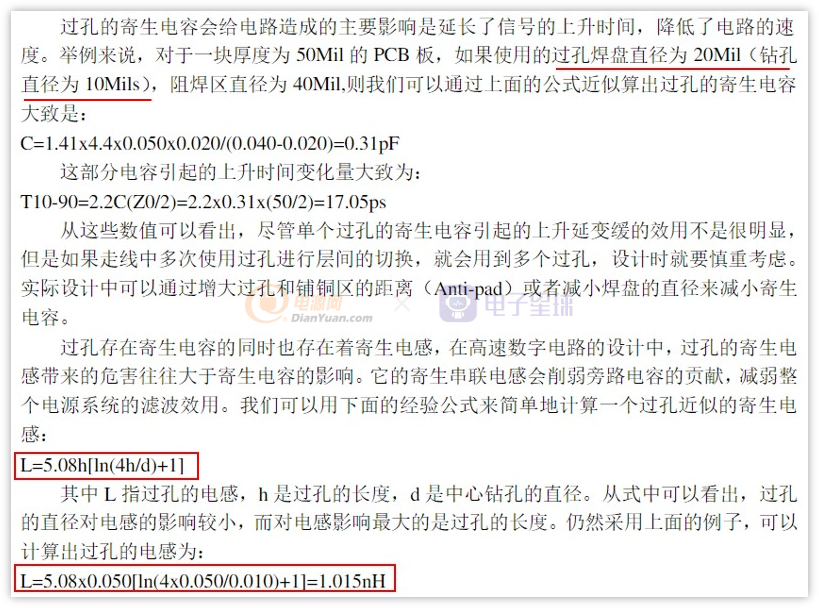

自然是因为过孔的寄生电感也是不能忽略的。

从上图可以知道,10/20mil的过孔的寄生电感达到了1nH,这电感量也是不小的。

所以我们在PCB layout的时候,如果是电容放置在背面,一定要多打些过孔,因为电感并联,总电感量是减小的。

多打过孔并不仅仅是考虑过流能力

在过流能力够的情况下,如果一个老工程师要求你打几个孔,或者把孔径加大。或许你认为是在为难你,也许是别人站的高度更高。

小结:

文章有点长,做了大量的仿真与分析,主要结论如下:

1、死区时间是同步buck中必然存在的,如果用示波器测到在开关切换时,有个负压的台阶,请不要惊慌,那是正常现象

2、寄生电感是BUCK上下沿振荡尖峰存在的必要条件。在做电路设计时一定要注意减小寄生电感。

3、开关速度越快,寄生电感越大,那么振荡尖峰也会越大。

4、振荡尖峰与PCB Layout的关系非常大。