MOS管在电源应用中作为开关用时将会导致一些不可避免的损耗,这些损耗可以分为两类:

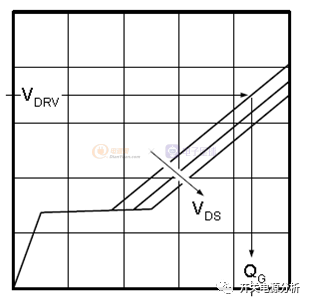

一类为器件栅极驱动损耗。前面我们说过:MOSFET的导通和截止过程包括电容CISS的充电和放电。当电容上的电压发生变化时,一定量的电荷就会发生转移;需要一定量的电荷使栅极电压在0和VDRV之间变化,变化如下图所示:

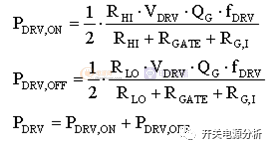

这个图表曲线给出了一个栅极电荷与栅极驱动电压成函数关系的在最恶劣条件下相对精确的估计。常用来生成这些曲线的参数是器件漏源截止电压。VDS(off)影响Miller电荷(曲线中平坦曲线下面部分),也就是在整个开关周期中所需的总电荷。在上图中一旦得到了栅极总电荷,那么栅极电荷损耗就可用下面公式计算:Pgate=VDRV * QG * fDRV;式中VDRV是栅极驱动波形的幅度,fDRV是栅极驱动的频率。这个公式中的QG * fDRV项,它给出了驱动栅极所需的平均偏置电流。驱动MOSFET的栅极损耗在了栅极的驱动电路上。在每个开关循环中,所需要的电荷必须流经输出驱动阻抗、外部栅极电阻和内部栅极网格阻抗。这样的结果是,功率损耗并不取决于电荷流经阻抗元件的快慢。我们可以将驱动功率损耗可表示为:

在上面的方程式中,栅极驱动电路用有阻抗的输出代替,但这个假设对于金属半导体的栅极驱动是无效的。当双极性晶体管在栅极电路驱动中被用到时,输出阻抗变为非线性的,而且公式将得不到正确的结果。为保险起见,假定栅极阻抗很小(<5)而且大部分损耗浪费在驱动电路中。假如Rgate足够大,足以使IG低于驱动双极型的能力,那么绝大部分的栅极功率损耗浪费在Rgate上。

除了栅极驱动功率损耗外,还有由于大电流和大电压在较短的时间内同时出现造成的传统意义上的开关损耗。为了保证开关损耗最小,这个持续的时间间隔必须尽量得小。观察MOSFET的导通和截止过程,应该减小开关过程中第2和第3个阶段的时间(无论是导通过程还是截止过程)。这个间隔是MOSFET的线性工作区间,此刻栅极电压介于VTH和VGS,Miller。漏极电压在开关间转换时,将会引起器件电流变化而且到达Miller平坦区。

在高速门驱动电路设计中领悟这点是十分重要的。它强调突出这样的事实:门驱动最主要的特性就是它在Miller平坦区电压附近的拉电流和灌电流能力。峰值电流能力,是在有输出阻抗时最大电压VDRV条件下测得的,和MOSFET的实际开关性能有很少联系。真正决定器件开关时间的是在栅源电压,也就是,在输出为5V的情况下(MOSFET的逻辑电平是2.5V)时栅极驱动电流的能力。

MOSFET的开关损耗的粗略估计可使用在开关期间第2和第3个阶段关于门驱动电流、漏极驱动电流、漏极驱动电压的简单线性近似。首先必须确定门驱动电流,分别为第2和第三阶段做准备:

假设IG2为器件的输入电容充电电流,在电压从VTH变到VGS,Miller;IG3是电容CRSS的放电电流,在漏极电压从VDS(off)变到0时,大致的开关时间为:

在t2时间内,漏极电压是VDS(off),电流从0倾斜变化到负载电流IL,而在t3时间内漏极电压从VDS(off)变到0。再次使用波形的线性近似,各自时间内的功率损耗近似为:

式中的T是开关周期。总的开关损耗是两部分的和,由此可得出下列表达式:

即使较好的理解了开关的过程,但是要精确的计算开关损耗几乎是不可能的。原因是寄生感性分量将会显著的影响电流和电压波形,也会影响开关过程的开关时间。考虑到实际电路中不同的漏极和源极感应的影响,将会导出一个二阶微分方程来描述电路中的实际波形。由于那些变量,包括开启电压、MOSFET电容值、驱动输出部分等等,有很大的误差,上述的线性近似对于MOSFET开关损耗的估算是可行的,是比较合理的。