运放1:理想运放与虚断虚短的来源

作者:硬件工程师炼成之路

今天开始,聊一聊运放吧,之前很多兄弟们也提了这个要求。正好我最近也想深入看看运放方面的,那么就借这个机会一步一步再搞一搞吧。

运放这个器件相对于电阻,电容,三极管,MOS管等器件算是比较复杂的,而且电路中也常用,出问题的情况也多,显然一篇文章根本就说不明白运放,因此,我可能要写很多期。具体多少期,写哪些内容,我一向都是不做计划,随心所欲,兄弟们有需求也可以提,我可以看情况安排。

背景介绍完了,那么就开始了。

第一步,理想运放

首先,第一个问题,我为什么要说理想运放呢?

因为一般来说,我们了解一个东西,都是先将它当做理想来看的,这样最为简单,也最容易懂。

当我们拿到一个陌生的电路,首先我们肯定是要知道这个电路是干什么用的对不?

这个时候我们就先不用考虑电路中器件的非理想特性,比如先不考虑温漂,漏电,寄生电感,寄生电容等等这些。我们就先把它当做理想的,然后看这个电路到底实现了什么功能,运放电路一般也是这么分析的。

等我们知道这个电路是干啥用的,然后再看看器件的哪些特性会导致这个电路失效,或者说不按照预期的工作,这个时候就要考虑非理想特性了……【继续阅读】

变频错相控制方法中时序管理的设计与思考

作者:杨帅锅

这是最近的一些只言片语的思考,一些零散不成体系的想法。后面如果有新的想法,再继续更新。本人能力有限,如有错误恳请帮忙指正,谢谢。

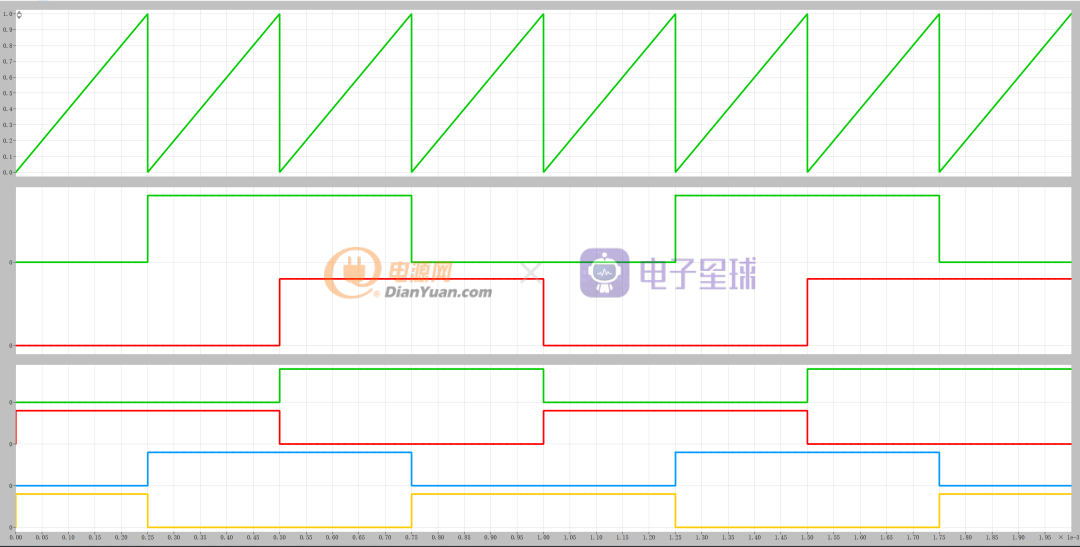

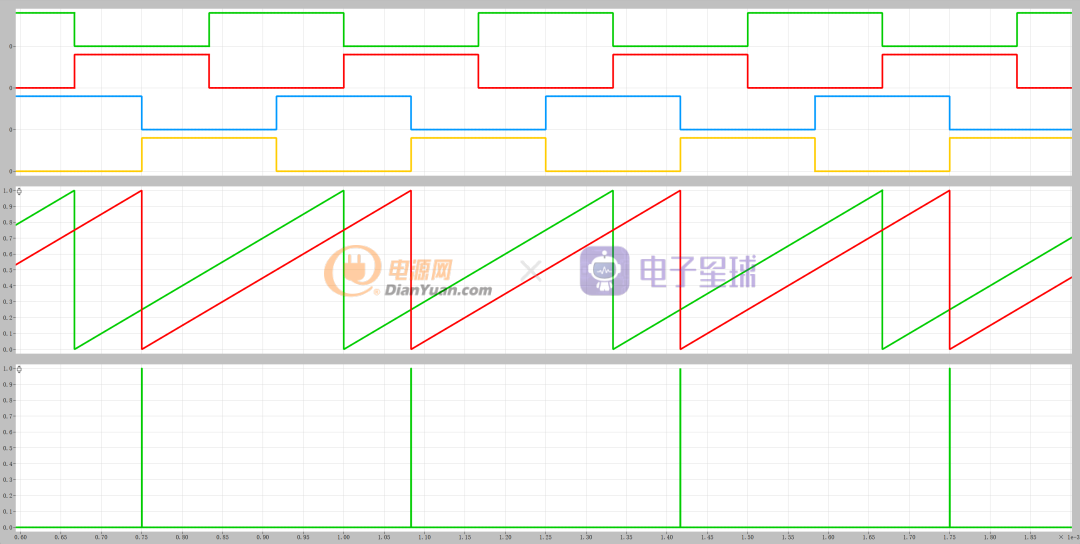

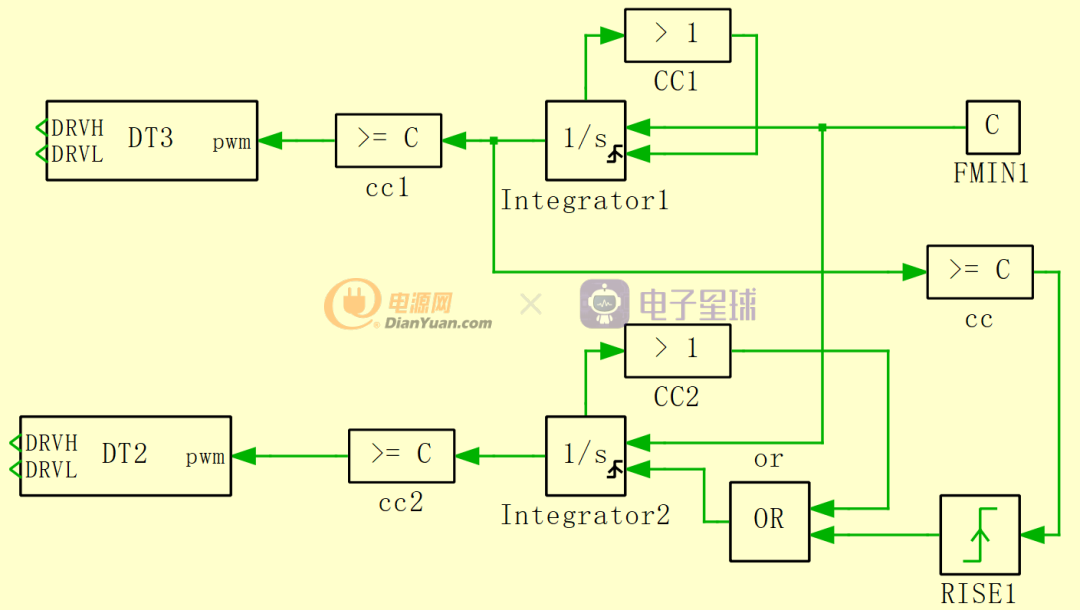

在比如LLC和CRM的两相交错控制中,我们需要同时变化频率又需要保证相位以设定角度工作。我们简单的以两相LLC交错90度的实现上来看,变化频率时,还需要保证角度正确,就需要事先知道频率变化后的周期长度,然后在去计算出滞后的时间,可见:

从上图来看,我们可以用时钟信号或者说是PWM RAMP的长度标志为开周期的25%,这样利用D触发器分频后,可以很容易得到滞后90°这个位置,然后用这个位置去开启B相,即可实现LLC的变频滞后90度的PWM输出。

在以这种方法的实现中,90度的位置基本上被固定,没用办法实现在滞后角度上的调整。同时PWM RAMP的频率x4后,在变化开关频率时,至少需要4个PWM RAMP才能稳定,理论上来说,动态时的频率和相位的误差会更大。

如果用两个PWM RAMP,使用PHASE A的90度时间点去启动PHASE B的计数。这样的动态响应应该会更好,这个方法也更容易在DSP中实现,可见:

使用两个PWM RAMP的0.5周期长度点做LLC的50%占空比点,用PHASE A的周期25%点做PHASE B的复位点,实现为:

其实LLC来说是要简单一些,因为作为频率控制变量可以事先在反馈中知道。CRM PFC中实现ZCD来做周期的复位信号时,就不同于LLC了。它无法使用事先的预知的周期终点来做相位管理,因为CRM的错相控制需要知道前一个开关周期长度,然后假设在相邻的两个周期的长度差异不大的情况,然后根据周期长度来计算出50%点的位置,再发出PHASE B的复位信号,可见……【继续阅读】

谈谈对电感的理解

作者:EMC小白

网上谈论电感的文章很多,不做过多评论,谈谈自己的理解,不到之处多多理解。

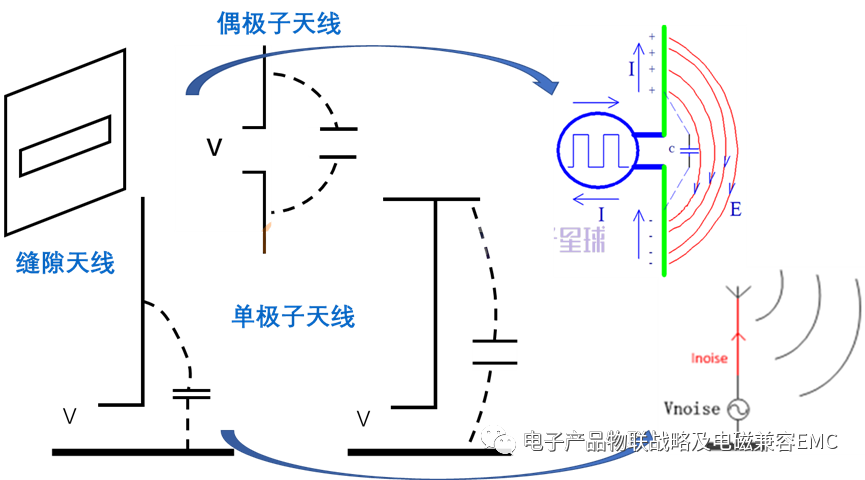

先来两句总结的话:1.闭合的回路导体叫电感,未闭合的回路导体叫“天线”;

2.流过导体的磁通量关注电感数值是多少,电流大小是多少,导体产生的感应电动势跟电感大小,电流变化率有关。

先谈谈第2条,我们知道闭合回路感应电动势的大小等于磁通量的变化率,即E=*ΔΦ/Δt,用电感表达式为L*di/dt,问大家一个问题,为什么要换算成电感的表达式来计算,很简单,方便计算和理解,如果我们不换算成L*di/dt,对待一段闭合回路的导线,则ΔΦ=Bs,S为环路面积,为定值,此时ΔΦ=dBs/dt,dB怎么变化,怎么理解,磁感应强度B网上给出的理解是单位面积通过的磁力线匝数,首先dB肯定是变化量,但是怎么跟导体的截面积,长度,围绕的面积挂上钩呢,这个公式对于我们计算感应电动势没有帮助,而换算成L*di/dt,则好容易理解的多,首先L肯定是固定值,di/dt对应的电场的变化率,因为变化的电/磁场产生磁/电场,变化率跟最初的变化场是一致的,那么这个感应电动势就直接跟这段闭合回路的电感值L成正比关系,理解了这个,下面就好办了,直接估算电感值就能知道感应电动势是多少。提个问题,为什么要强调闭合回路,那是因为L*di/dt是通过电流反推电压是多少,没有了闭合回路,E=*ΔΦ/Δt仍然成立,但是此时后面的公式不成立,至于感应电压值是多少,应该可以通过天线知识进行理解,本文不做深入研究,所以我才会最前面提到闭合的导体叫做电感,未闭合的导体叫“天线”。

闭合回路中,既然磁通量和感应电动势都是跟电感感值L强相关,我们有必要重点研究电感。

首先看两个公式导体电感感值L=5d[ln(2d/r-3/4],其中d对应导体长度,r对应导体截面积半径,还有一个公式环形线圈电感感值L=32*R*ln(4R/D),R对应环形半径,D对应导体截面积,当然我们还不能忽略两个数值,其中一个是磁导率u,还有一个线圈匝数,这两个数值都是跟电感L成正比,但是这两个公式怎么理解。

电感的定义是导体在1A电流下对应的磁力线匝数,我们看第一个公式,发现电感感值跟导体长度正比,跟导体截面积半径成反比,我们从磁力线匝数角度来理解,首先导体长度边长,那么磁力线的匝数会变多,截面积变大,电感L为什么反而变小呢,这是因为当截面积变大时,电流的密度会降低,磁力线会变得稀疏,反而变小,这个是经验值,可以考虑强行记忆。

对于第二个公式,环形半径R变大,则电感感值L变小,这个就需要考虑互感的因素,因为是闭合回路,平行的导线电流方向相反,两根导线的磁力线匝数会彼此抵消,从而总的磁力线匝数变小,即总的电感感值变小,所以对应环形电感,电感感值跟半径R成正比,对应导体的截面积,这个道理跟前文是一致的,电感感值跟导体截面积成反比。

上面讨论的两种感应电动势,都是电流直接流过导体产生的,即感应电动势是由变化的电场产生的,那么由变化的磁场产生的感应电动势怎么理解呢,我们还是回到闭合回路上来,当闭合回路的磁通量发生变化时,产生的感应电动势同样可以由流过的电流反推出来,此时可以将该闭合回路看成是单匝线圈,同样是跟回路半径R成正比,导体半径成反比。谈到这里,我们就不难理解,我们经常要保证回流路径短了,其实准确是半径R要小,对于同样的面积,扁平状的电感感值要小于正方形的电感值,即同等面积情况下,右侧的电感感值要大于左侧的……【继续阅读】

STM32芯片引脚为什么有那么多组VDD?

作者:硬件笔记本

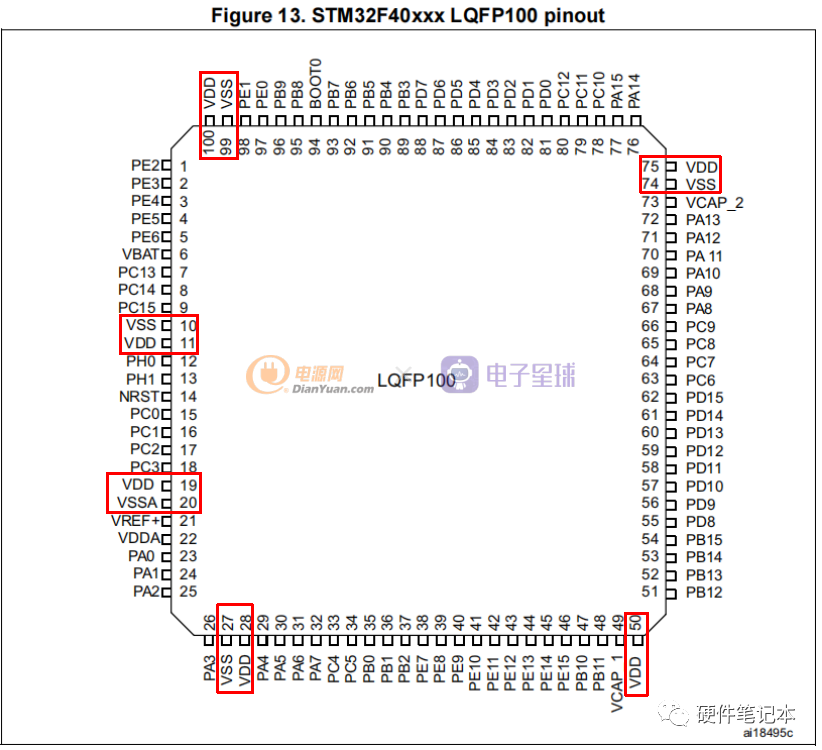

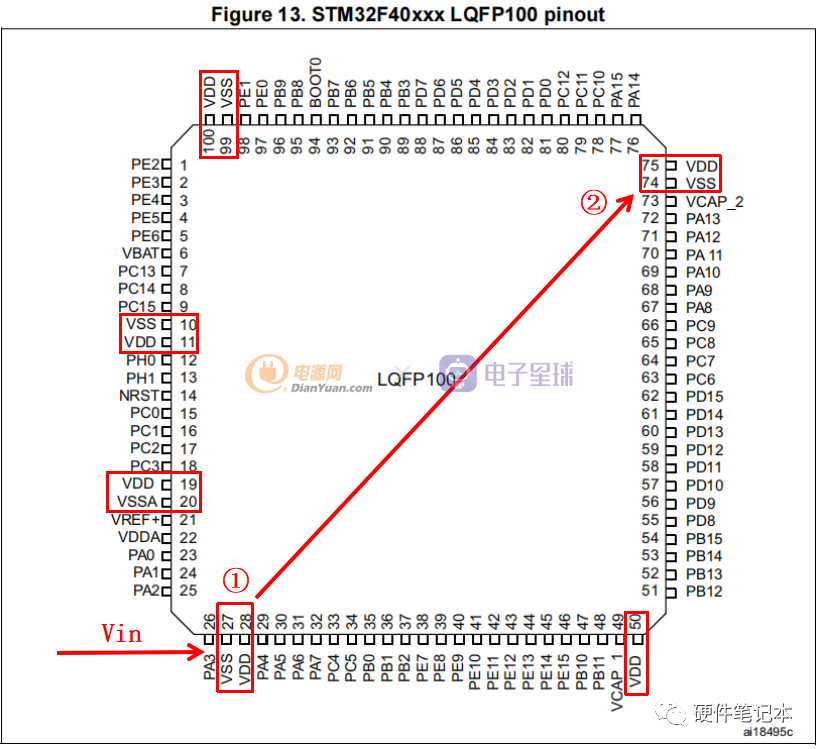

做过单片机产品的朋友都知道,STM32芯片有多组VDD和VSS,如下图:

那么为什么有这么多引脚呢?少一点不好吗?引脚越少,PCB走线越容易。

其实芯片这样设计是有原因的。

1、增加电流供应能力

单片机IO口输出电流的能力是有限的,传统单片机的IO口一般为10mA左右,现在单片机的IO口一般为20-25mA。

多个IO口加起来,相当于增加了很多供电通道,扩大了电流供应能力。相比单个引脚的VDD,增强了可靠性。

如图,假如一个IO口流过的电流是20mA,三个IO口就是60mA。

2、方便就近取电

为了方便描述,我画了一个如下示意图。

假如只有一组VDD,从①处供电,当②处需要用电时,只能沿着箭头所示路径流动,可以看出距离较远。

当负载增大时,VDD电流产生突变,路径距离越长,产生的压降越大,电源波动越明显,从而影响单片机的正常工作。

如果此时,在单片机②处直接外接电源VDD,路径最短,电源最稳定……【继续阅读】

产品可靠性设计-辐射敏感度的测试与整改

作者:杜佐兵

一个重要的测试试验是确定外部的射频场是否会对产品产生影响是辐射抗扰度测试。对于商用产品测试标准为IEC 61000-4-3。试验的频率范围通常为80~1000MHz。具体数值取决于产品所处的环境或其实际使用的环境。施加的场强电平范围为3~20V/m。该测试是在半电波暗室内进行的,使用宽带天线在受试产品的方向上辐射射频场强。使用半波暗室的目的是避免对其它通信业务的干扰。一些军用、车辆或航空与航天标准,要求施加的场强为200~1000V/m,测试的频率上限到18GHz或更高。

对于商用产品的测试,射频信号通常为1KHz的正弦AM调制,调制深度为80%;对于军用和航空与航天试验,通常使用调制频率为1KHz的方波或持续时间很短的脉冲调制。这种调制设计用来对音频整流问题进行测试。

比如,如果射频信号通过半导体或在音频或其他模拟电路中进行整流,那么低频调制可能会引起偏压混乱或会破坏敏感的模拟电路。

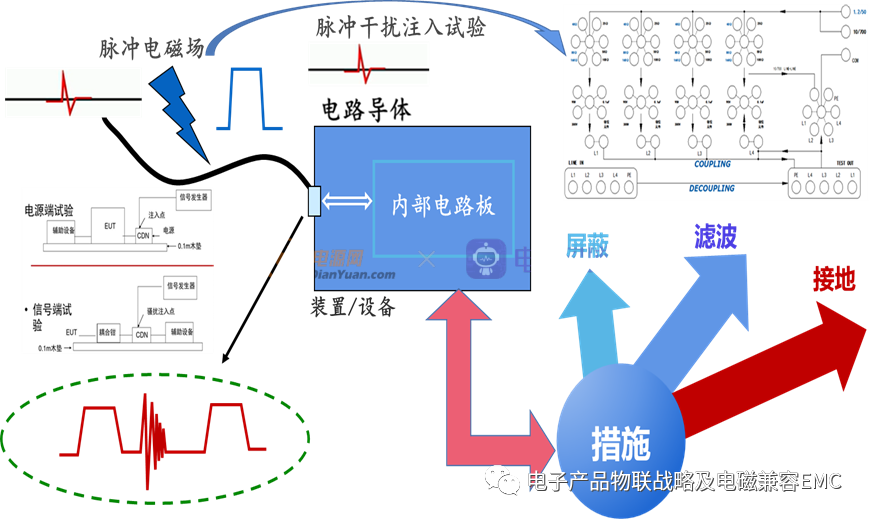

测试和模拟如下图所示,也因此根据实验通常也有屏蔽、滤波、接地的改善措施。

辐射敏感度问题的检查和诊断

在大多数情况下,辐射发射是辐射敏感度的相反的测试过程。原因是产品上向外产生辐射的发射天线也是接收天线。

比如,电缆及外壳上的缝隙也能作为接收天线,能把射频场传输给产品,并且能潜在地引起干扰或者使系统重启。

(1)电缆的屏蔽层与外壳或屏蔽壳体搭接的不好。

(2)使用“猪尾巴”端接电缆的屏蔽层。

(3)屏蔽面板之间的外壳或壳体搭接得不好。

(4)视频显示LCD/LED具有大的孔缝。

(5)I/O连接线或电源电缆的滤波不好。

(6)关键电路处的射频旁路不够充分,比如CPU/MCU的复位线或模拟输入或传感器输入……【继续阅读】