我是Sig008,从事信号、电源完整性工作,喜欢钻研,喜欢交流,今后会多把一些理论知识以简单易懂的方式梳理出来,供大家一起交流;

大家也可以添加我的个人微信,进一步交流讨论:LLFF_5021

上期文章说到,信号经过电容后的影响,对于相当宽频段的信号而言,直接通过电容是没有问题的。

当然,上面只研究了电容以及电容的寄生参数本身的影响,下面来看一下,电容焊盘的影响。

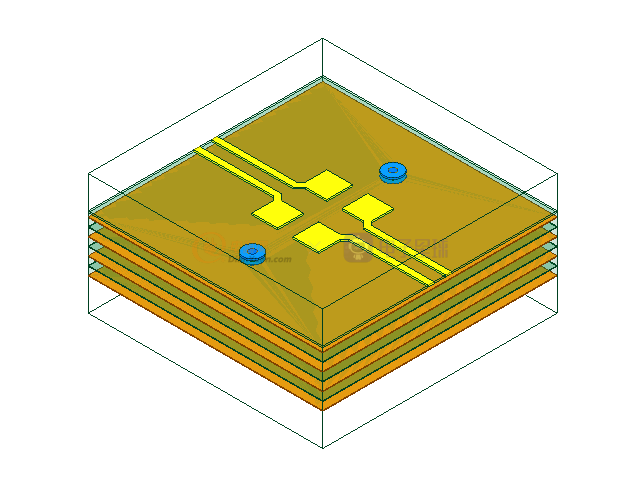

对于如下0402封装的电容焊盘结构,传输线在经过焊盘时,由于焊盘尺寸变宽,明显阻抗是不连续的,对如下模型进行仿真。

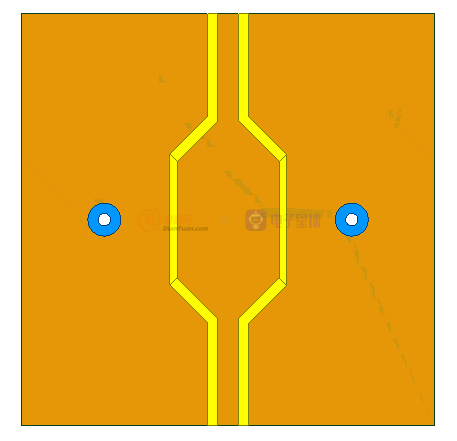

为了消除结构引入的影响,将传输线建立模型如下:

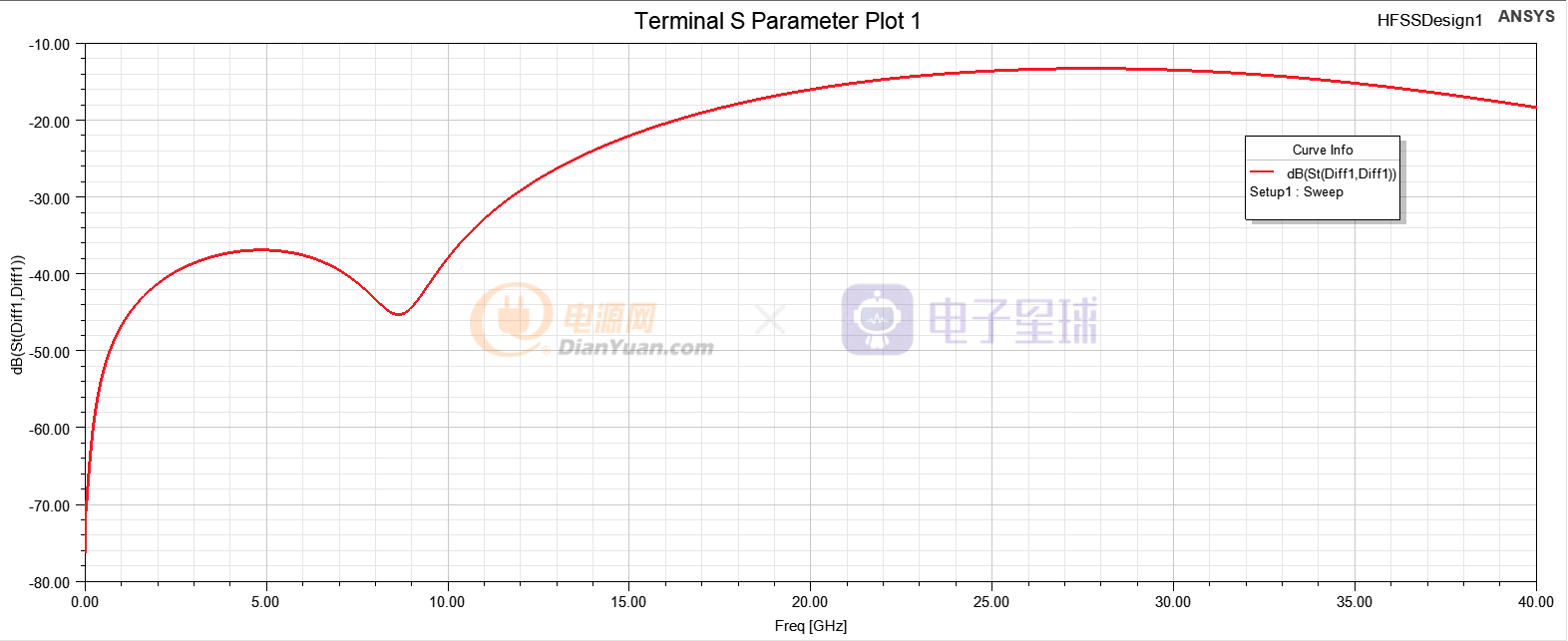

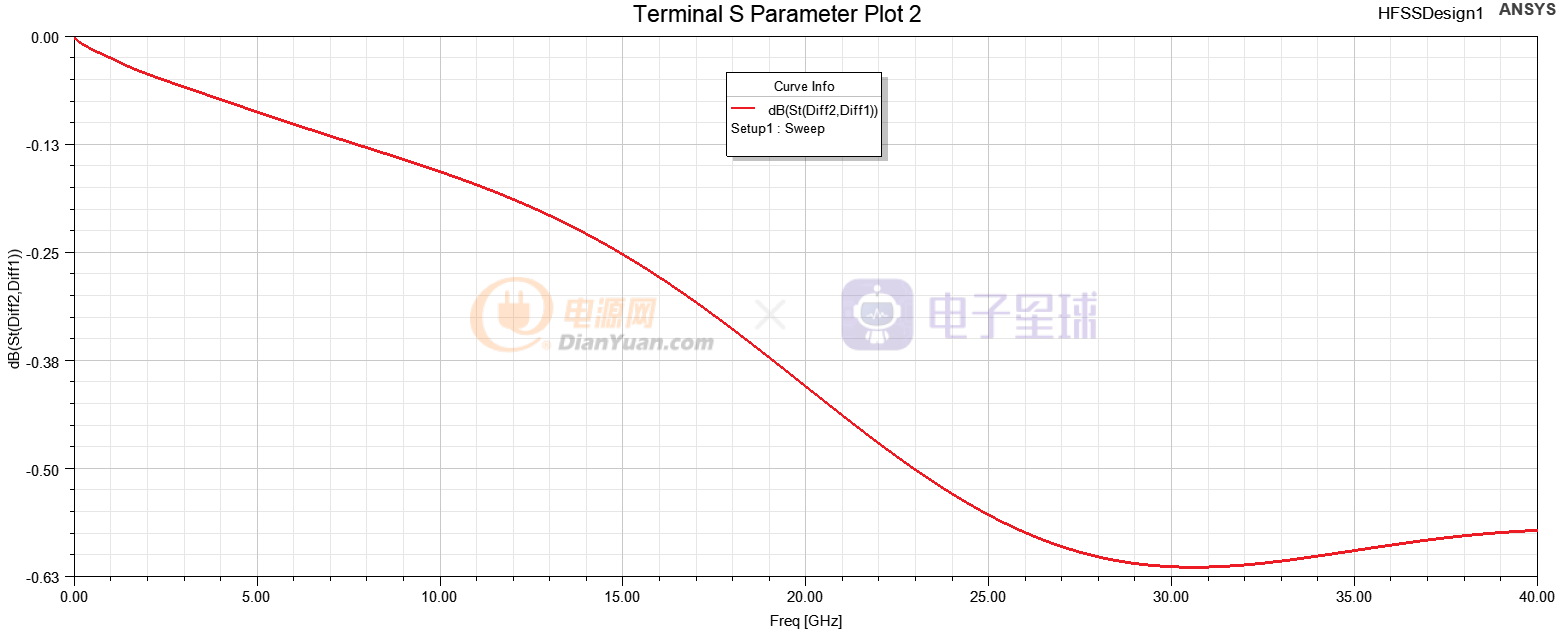

传输线的S参数如下:

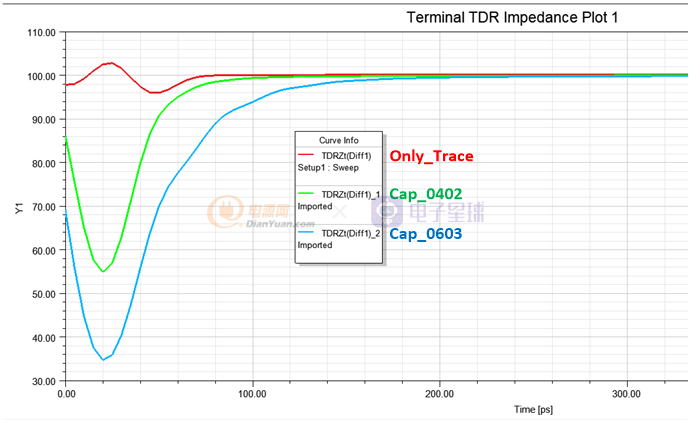

在10ps上升边时的TDR如下:

加上0402封装的电容焊盘后,S参数如下

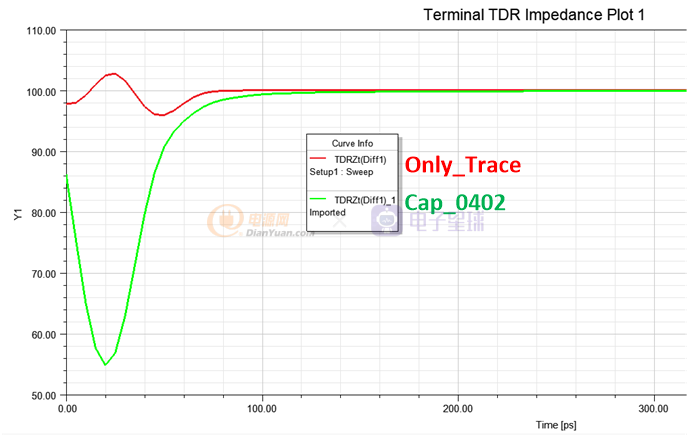

在10ps上升边下的TDR如下:

100ps上升边下的TDR如下:

通过TDR可以直观的看到,加上电容焊盘后,阻抗跌落很多,而这也对S11造成了很大影响;

这里需要注意不同频率信号感受到的阻抗是不一样的。

我们来看一下,信号在通过两种路径后的波形:

先来看看100MHz信号,上升边沿为100ps:

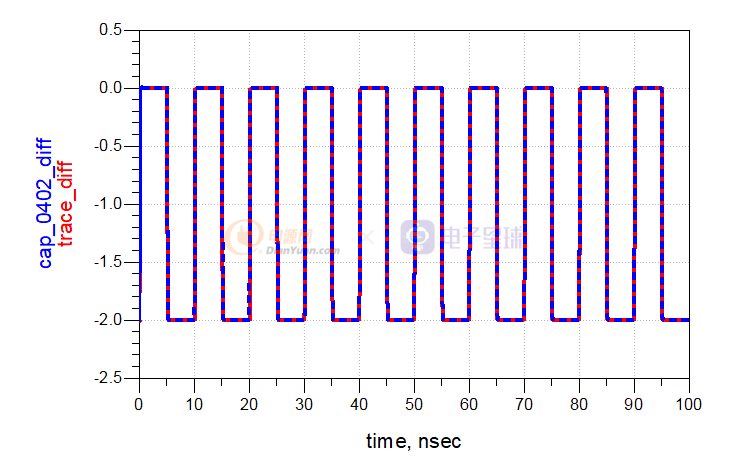

感觉信号没有受到影响,下面看3.2Gbps信号:

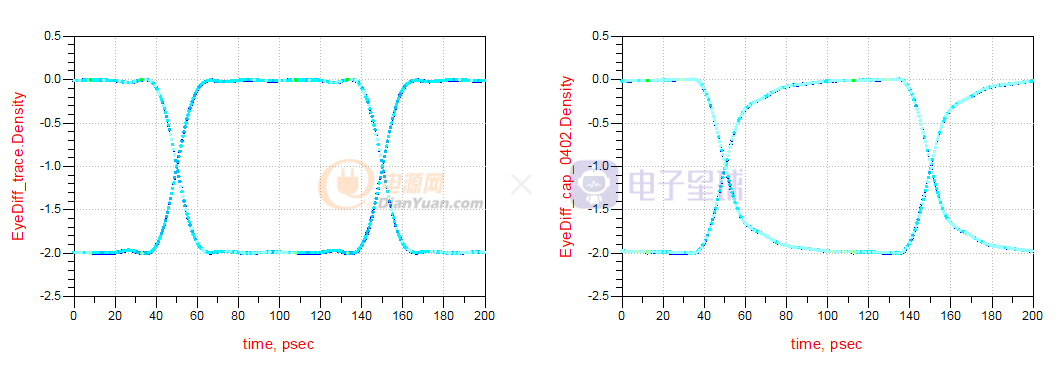

似乎也没什么影响,继续看10Gbps:

稍稍有些影响,到目前为止,似乎感觉焊盘对信号的影响不大;

但是现在还不能说焊盘这里没有影响,因为,现在只考虑了电容焊盘这里,没有考虑其他阻抗不连续,这也就是为什么还要考虑电容的位置;

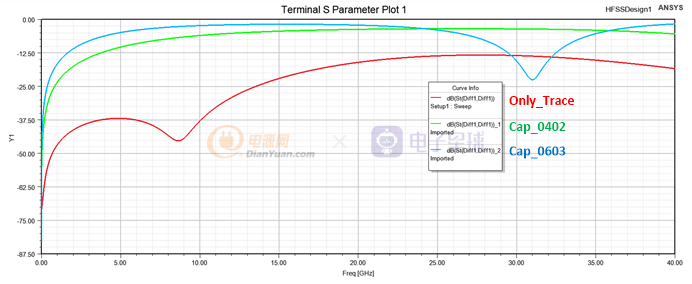

我们继续看一下0603封装电容焊盘的S参数:

在10ps上升边时的TDR如下:

在100ps上升边时的TDR如下:

可以看到,封装越大,阻抗越小;

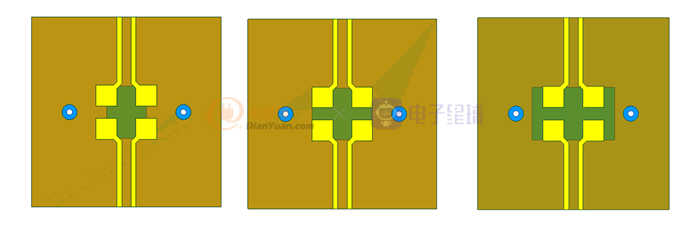

我们先来看焊盘这里阻抗如何优化,非常简单的做法就是,将参考层掏空,我们先来将L2层掏空,也就是在焊盘这里参考第四层,0402封装掏空尺寸分别如下:

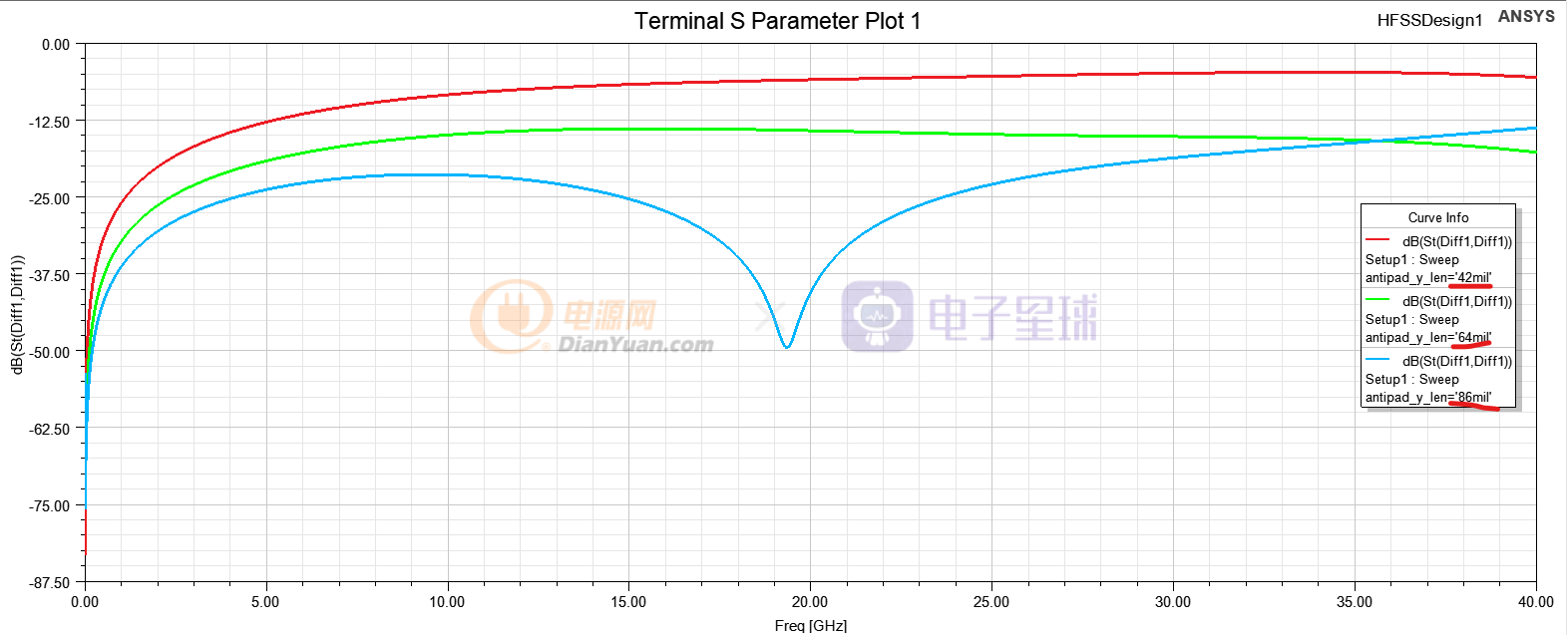

S参数如下:

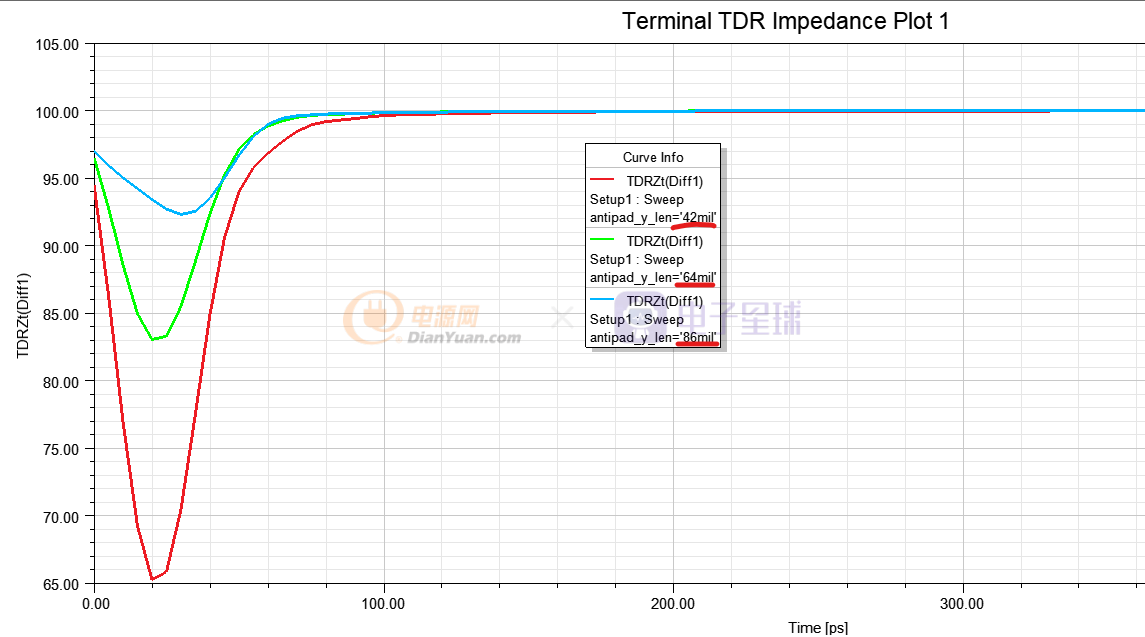

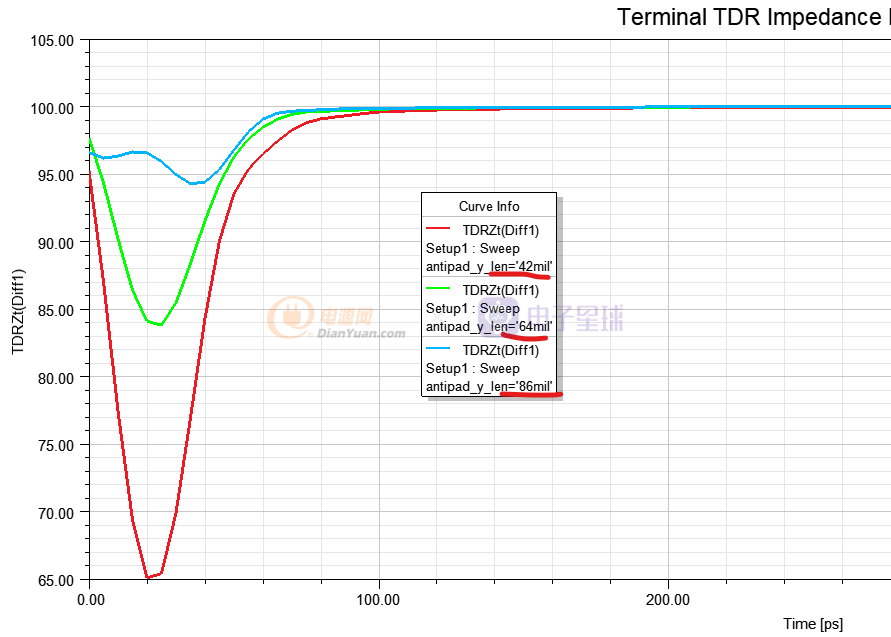

10ps时的TDR如下:

对于0402的焊盘而言,在第2层进行掏空,掏空后,焊盘参考第四层,可以看到这样的趋势,掏空尺寸越大,阻抗越大,尺寸稍稍大于焊盘尺寸时,阻抗比较好。

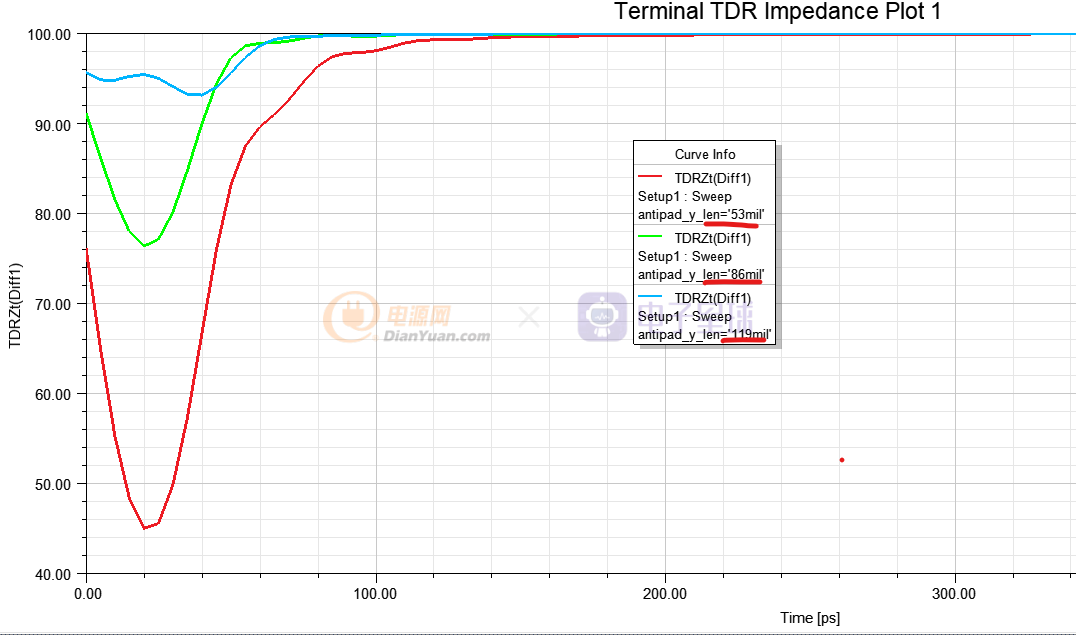

下面看一下,继续将第四层也掏空,此时焊盘参考第六层,10ps时的TDR如下:

阻抗进一步抬高一些;

到现在得到如下趋势,掏空尺寸越大,阻抗越高,参考层越靠下,阻抗越高,掏空尺寸稍稍大于焊盘尺寸最好,大概参考第四层或者第六层比较好,具体还是要视具体叠层和结构而定。

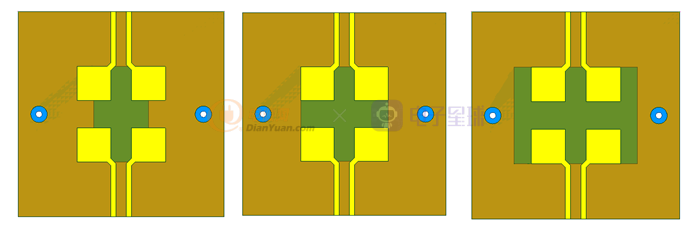

对于0603封装焊盘的掏空尺寸如下:

0603封装焊盘模型

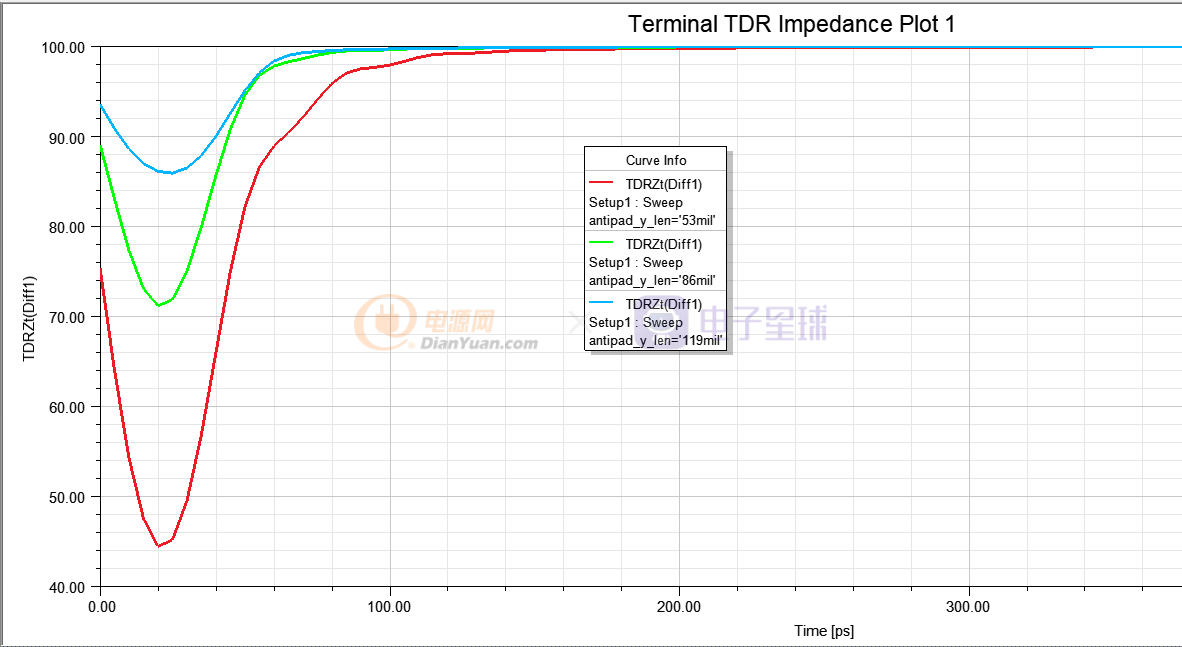

将第二层掏空后,此时焊盘处参考第四层,TDR如下:

将第四层掏空后,此时焊盘处参考第六层,TDR如下:

对于0603封装的焊盘仍然可以得到如下趋势,掏空尺寸越大,阻抗越高,参考层越靠下,阻抗越高,掏空尺寸稍稍大于焊盘尺寸最好,大概参考第六层比较好,具体还是要视具体叠层和结构而定。

由于篇幅原因,我们先讨论到这里,先来搞清楚焊盘对阻抗的影响,以及焊盘下方掏空尺寸对阻抗的影响,下一篇我们来看电容位置的影响。