大家好,这里是大话硬件。

今天想分享一篇关于大话硬件群里的,时钟预留电容工位的问题。

01 问题背景

前段时间在大话硬件群里有人提问,SPI的时钟信号线上串接上了电阻,并且预留了电容C的工位,该如何解释?

群里有几个人对这个问题进行了解答,一致认为是EMC的需求。在RE测试时,预留的电容焊接上能起到非常大的作用。

背后详细的原理和原因到底该怎么解释呢?

02 单板时钟辐射

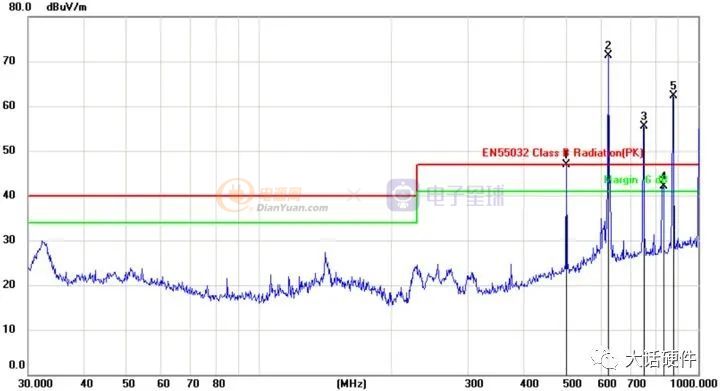

在电磁兼容辐射测试时,出现超标比较多的案例都是单板上的时钟辐射超标。例如下面这张图,高频段辐射明显超标。在不进行后续分析的情况下,可以初步判断,80%的概率是时钟辐射引起的。

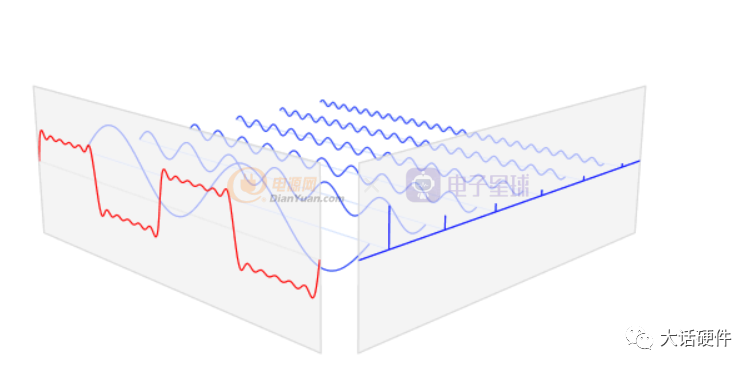

根据傅里叶变换,我们看到的时钟信号,实际上是由很多基波组成。只不过在时域上测试到的是固定周期信号,而在频域上测试就是离散的频谱。

例如下面这张图中(图片来源于网络),左边看到的是时域方波,而右边看到的是频域方波。

在实际的电路中,时钟是方波,数据也是方波,但我们一般都会认为高频单支辐射超标是时钟引起,而不认为是数据引起,这又是为什么呢?

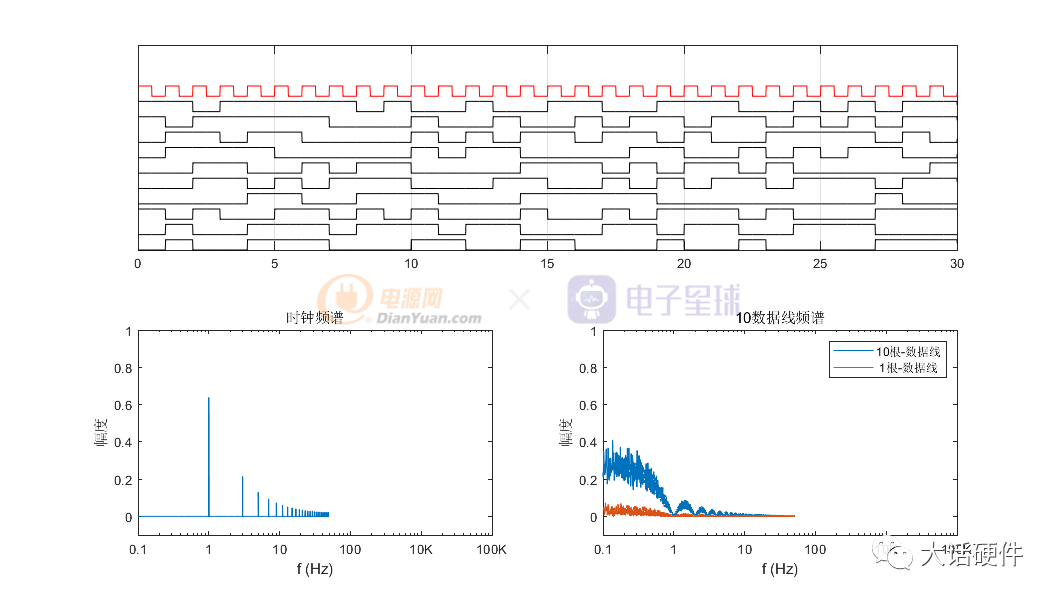

可以借助下面一张图来解释:(图片来源于网络)

时钟是固定的频率,在频域上是有规律间隔的单支能量,而数据在传输过程中,时域上的频率并不是固定的,几个时钟周期内可能都为高电平或者低电平。因此数据的辐射,不是单支的能量,更多的是以包络的形式出现。

根据上面的分析可知,图2中辐射超标为单支能量,而且都是高频,因此大概率是时钟的辐射引起。

03 时钟预留RC

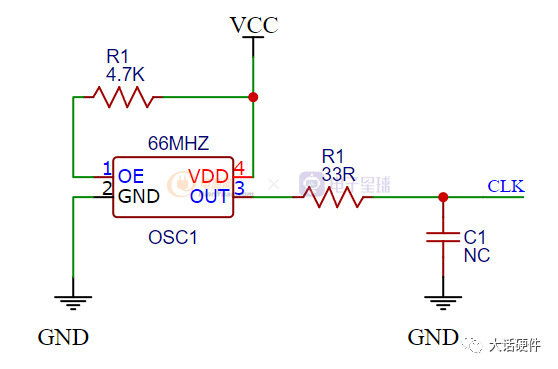

大话硬件群里的提问,他们设计的有源晶振电路下图所示。

电阻R1放置33Ω的原因是用来做阻抗匹配。IC半导体内部管脚输出脚的阻抗一般在22~55Ω之间,外面放置33Ω的电阻可以起到阻抗匹配的作用,降低信号的反射。

要分析电阻R的作用需要做信号完整性方面的仿真,可以仿真出来在源端接不同的电阻发生反射电压的大小。目前在一块没有对应的软件储备,详细的仿真和分析,后面学会了再补上。

在信号线上加电容,对于信号的影响,可以两个维度解释。

维度一:滤波的角度

电阻R1和电容C1形成了低通滤波器,对于高频信号有衰减的作用。因此对于时钟辐射的高频信号,RC可以在一定程度上让高频信号能量往外辐射更少,因此可以降低辐射。

详细的原理共和仿真可以看以前的文章《RC无源高低通滤波器》。这里不再赘述。

维度二:傅里叶变换

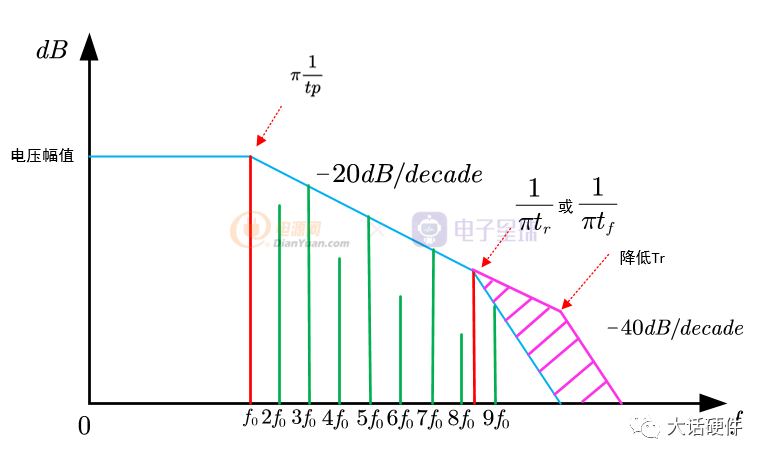

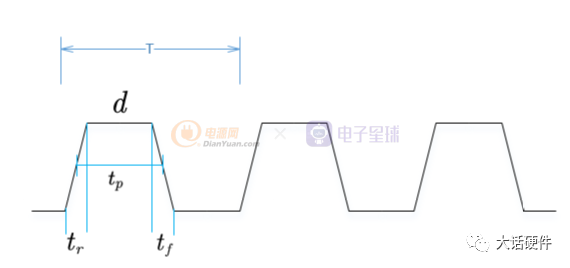

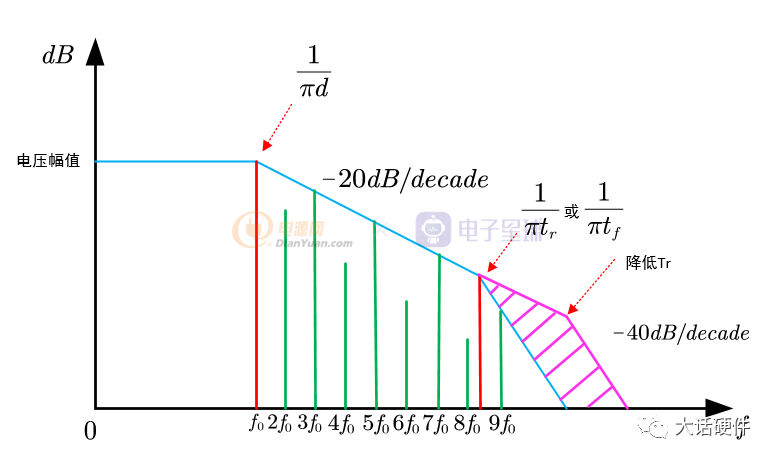

根据傅里叶变换,对于一个时钟信号,其频谱的包络在频域上有两个转折点,一个是半峰值时间Tp,一个是上升沿时间Tr。

时钟频谱的第一个转折点由时钟半峰宽度决定,经过该转折点时,幅度以-20dB/dec的斜率下降。

第二个转折点由上升沿或下降沿的时间决定,经过该转折点时,幅度以-40dB/dec的斜率下降。最后包络和横坐标的频率相交于一点。

那么,要降低时钟的高频辐射,比较有效的方式是增大时钟上升和下降的时间,第二个转折点就会更快地到来,对应的高频辐射就会更少。

例如下面的图所示,Tr越小,高频段的辐射能量越多,对应的辐射频段就会越高。

04 实际仿真

很明显,时钟电路中增加了电容C可以增大Tr,因此时钟的包络第二个转折点会向横轴前移,因此高频段的衰减就会更快。有利于RE辐射的测试。

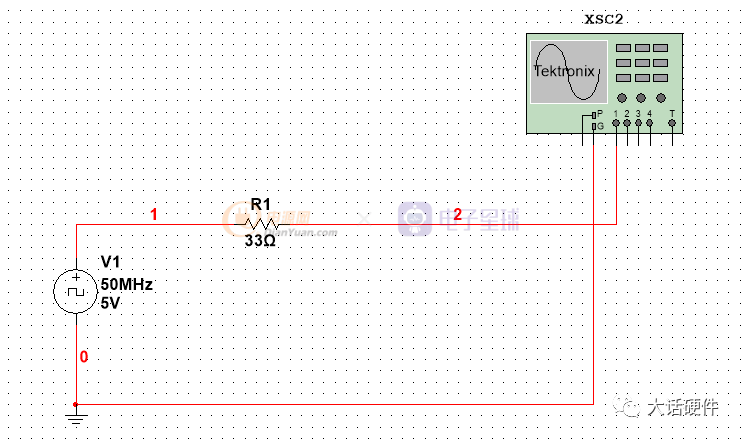

使用下面的图进行仿真,V1模拟时钟信号,输出为标准的5V方波,频率为50MHz,串阻33Ω

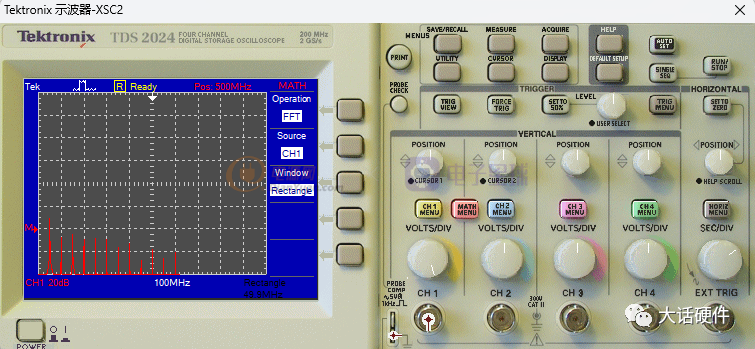

进行傅里叶分析后的频谱

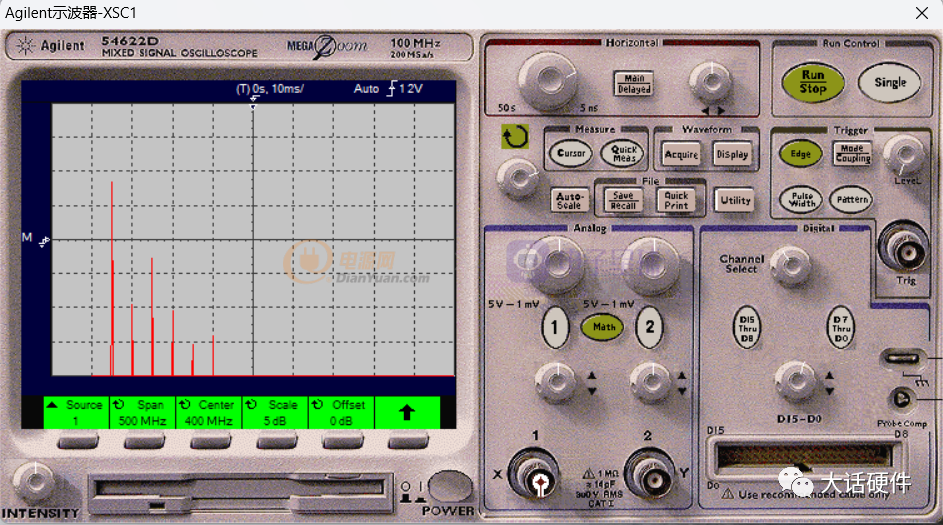

从仿真上可以看出,时钟的频谱呈现单支的能量辐射,目前示波器只显示到了100MHz。换个Agient的示波器看起来效果更好一点。

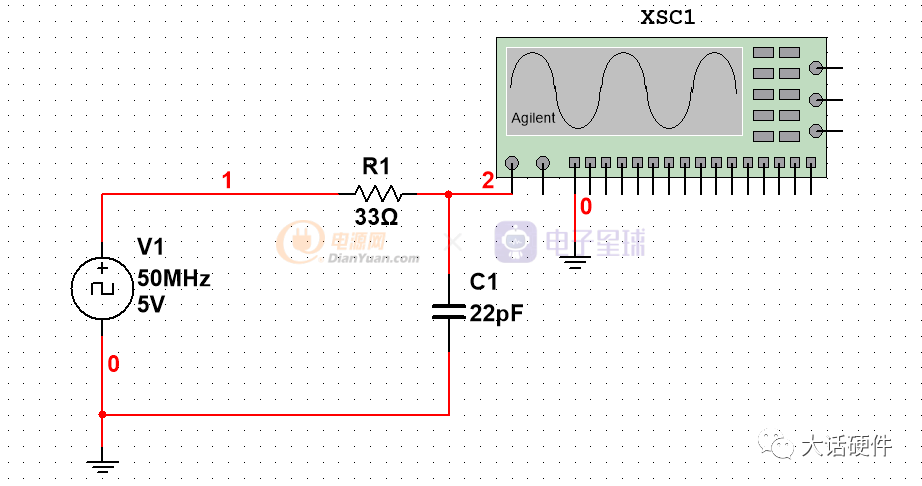

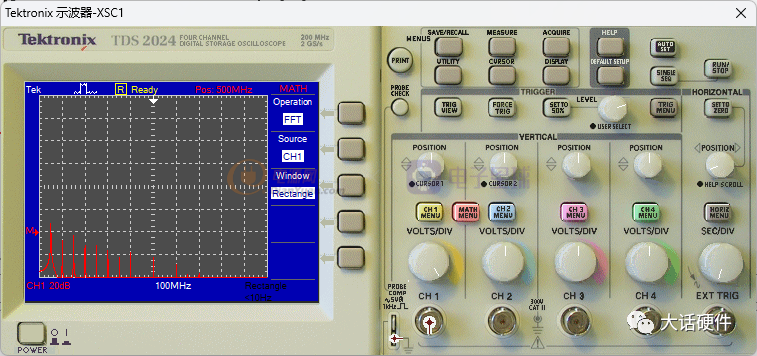

在时钟输出端增加22pF的电容,继续仿真。

从仿真结果可以看出,加电容后时钟的高频段的单支能量明显比未加电容要少。在中心频点400M以上的部分几乎没有,而未加电容时,400M以上的还有2个单支的能量。

05 EMC能力提升

根据上面对时钟分析的相关结果,可以把相关的理论用在静电,浪涌防护的接口设计中。

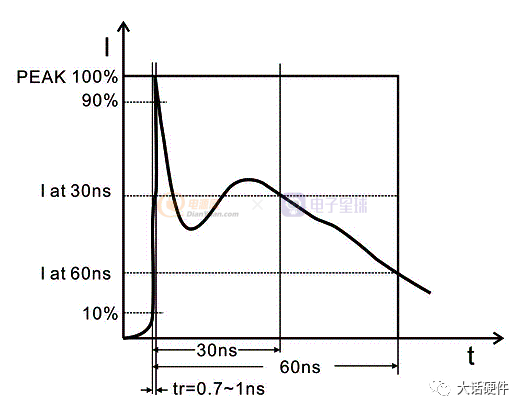

例如,静电测试标准的静电波形,根据波形的上升时间Tr=0.7~1ns,可以计算出静电的频谱宽度会达到450MHz。

如果要在接口做静电的滤波设计,比如使用电容将静电泄放到地上,必须选择100pF,470pF,1000pF这样容值小的电容,而不是选一个200uF的大电容去做静电的滤波设计。

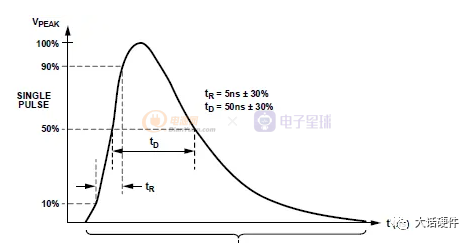

同样,在EFT测试中,标准波形是下面这样,根据Tr时间是5ns,那么可以计算出频谱的宽度达到65Mz

此时选择EFT的滤波器件,就要选择0.1uF的滤波电容,或者镍锌磁环,镍锌磁环的滤波频段基本都在50MHz以上。而不是再去选用一个1000pF的电容。

06 问题总结

根据前面的分析可以,在时钟上预留一个RC工位,在做辐射测试是很有必要的措施。一般电容C不焊接,如果EMC摸底测试发现时钟信号超标,那可以将该电容焊接上,对整机的EMC辐射是有帮助的。

这个电容在取值时,不是随便取值,10~100M的时钟信号,经验值一般取10~30pF即可,既要保证时钟上升沿不能太缓,又要保证RE的通过。

同时,对于这个辐射包络的问题,还可以用在EMC其他防护器件的选型上。值得大家深入的研究。