大家好,我是广元兄。很高兴和大家分享信号完整性的相关知识。希望大家点赞,分享。有什么问题加微交流学习,微信号【SI_Basic】。

Slogan:一起学习,共同进步!

信号完整性的工作,很大一部分是对PCB走线规则的设定以及走线优化。规则设定得好是一个PCB设计的基础,也是最关键的部分。所以,设定规则来管控风险比出现风险解决来得更重要。预防管控的能力是未来信号完整性工程师的必备基础技能。预防管控PCB走线的风险,最最基础的知识就是熟知常用走线规则。

01

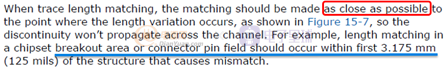

线长匹配的原则是等时。考虑信号在表层和内层速率不同,所以一般建议就近匹配等长,这也就是很多资料里提到的“动态等长”。下图也给出了就近匹配的不同方式:

整条链路的等长匹配,如果P/N差别比较大,会在走线层面比较空的地方进行3W2S,也有在PAD区域绕线来达到匹配。如下图所示:

02

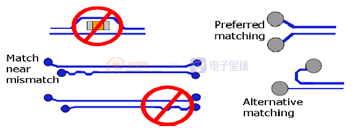

高速信号建议走内层,就是为了做阻抗的管控。

阻抗误差范围:微带线+/-15%,带状线+/-10%。

03

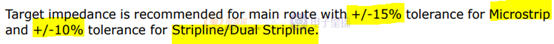

玻纤效应影响,走线锯齿状,对应信号速率走线长度的管控,如下图:

04

消费类的一些产品会选择走双带线。双带线(Dual Stripline) 上下错开,不重复(Offset>0),最好是垂直走线;D2(4~9mil)。

05

过孔处阻抗突变的优化,过孔阻抗和反焊盘的大小、孔径、焊盘大小都有关系。参考层面发生改变,GND回流孔距离上也要注意,有的资料给出的距离≤100mil。

06

SMT连接器的处理方式,有的是相邻层挖空,也有推荐挖空15mil,一般是往下两层走线层,但要注意第四层是否是地层参考的问题。

当然,PCB设计规则不仅仅是这些走线规则的问题,从产品开始的叠层设计就需要管控,避免非对称叠层,板材的选择(PP&CORE),铜箔类型等等,再到走线层面规划:高速信号优先,高速信号残桩问题(高速产品),双带线模型走线问题(消费类产品)。

任何一款好产品的设计不是一个点,而是多个点的,不是一方面,而是多方面的优化结果。