引言

作为半导体行业资深工作者,我经常接触到电源的设计工程师,发现不管是电源的老手,高手,新手,几乎对控制环路的设计感觉讳莫高深,基本上靠半导体IC前端的IC-Designer进行理论及搭建小信号的变换器研究.通常我们对反激电源系统其有电感及小信号的环路系统,其系统的相位及增益的补偿设计研究比较多,也比较容易;补偿器的bode图也很容易设计图表化!(所以大部分IC公司对反激及BOOST电源系统设计补偿资料比较完备-由于变换器的小信号系统在环路中设计相对容易),目前我有客户在说LLC的增益和相位怎么计算?希望能通过直观的数据进行分析;由于LLC系统变压器双向励磁工作,需要额外附加变换器的小信号系统,由于其分布参数及系统的复杂性其理论数据存在比较大的差异,需要环路分析仪进行实际的数据测量。

应IC使用者需求,通过理论和测试的方式-介绍如何快速确定系统相位增益设计及系统稳定性;

1.环路稳定性评价指标

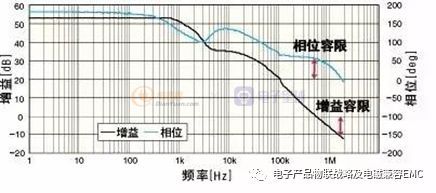

衡量电源系统稳定性的指标是相位裕度和增益裕度。同时穿越频率,也应作为一个参考指标。

(1) 相位裕度是指:增益降到0dB时所对应的相位。

(2) 增益裕度是指:相位为0deg时所对应的增益大小(实际是衰减)。

相位裕度,增益裕度,穿越频率,如图(波特图)所示。

相位容限即相位裕度,增益容限即增益裕度(图示为单端反激的系统)

环路稳定性测试接线图(环路有小信号环路)

2.如下针对系统使用的LLC架构 选择控制IC-两通道LLC/LED背光驱动设计

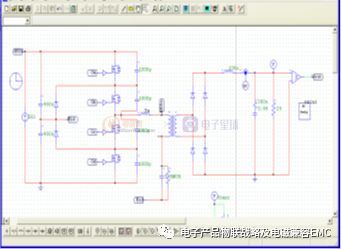

原理图设计方案如下:如何快速确定系统相位增益设计及系统稳定性?

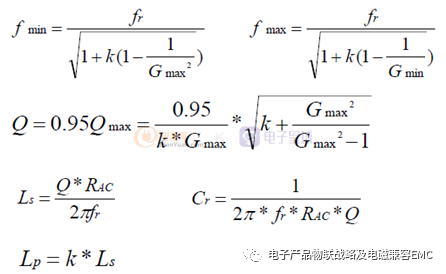

3.LLC系统方案的设计;其主体变压器的谐振参数及规格如下;

PFC输入:380V-400V 输出160V/0.56A 2Channel 系统效率>92%

变压器设计规格参数:

变压器EE50/PC40 NP=52T NS=36T NP/NS=1.444

LP=550uH-±10% Ls=160uH-±10% Cr=22nF

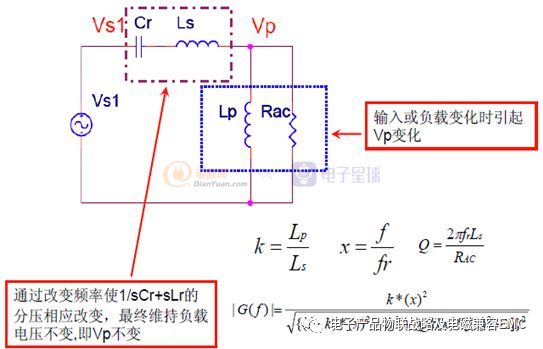

4.对LLC建立等效模型如下;

通过LLC变压器谐振网络和已知参数得到数据的推导结果如下:

注意:

① 理论上,高增益大于1.8是可能的,不过,这将导致严重的循环中谐振电流和恶化的效率。实际上,增益小于1.8是可以接受的

② 大增益可通过减少K因子。然而,变压器耦合K太小会影响结果和效率。

设计细节可参考:《谐振电源:LLC的设计与分析!》

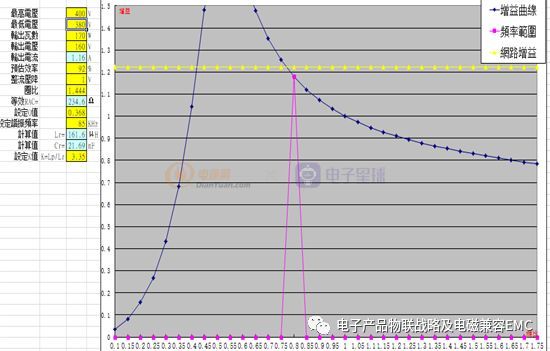

5.通过模型带入变压器及谐振设计数值,得出如下设计曲线图

设计结果:Q=0.37 K=Lp/Lr=3.35-3.43 网路最大增益=1.2236 <1.8 is OK!

6.我们对系统进行实际的相位分析时,需要建立变换器和小信号系统;

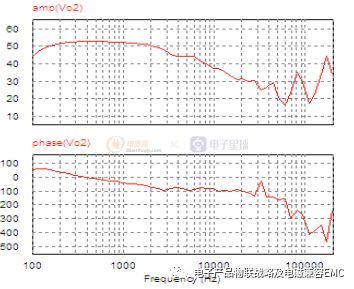

环路分析仪-是环路设计最方便的工具;使用环路分析仪直接得到系统的开环 增益相位曲线;我们对模型进行仿真如下:输入4.上述参数-补偿器的bode图

LLC系统的小信号环路测试原理图

系统仿真得到的LLC 环路增及相位控制图;

7.本设计中IC-LLC的工作频率范围由IC/RT引脚决定,其工作范围请参考产品规格书-DS ;

通过补偿器的Bode图,LLC要工作在零电压开关模式;同时通过环路设计减小MOS开关的电压电流应力;

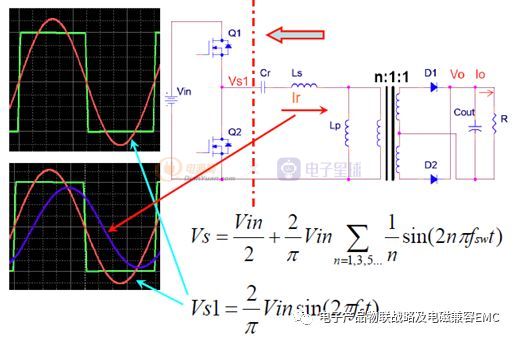

8.根据LLC的工作特性,为了更简易的分析其相位关系 我们可以将次级输出返回到变压器原边的开关节点确定其相位是否满足要求;等效原理图如下:

LLC-ZVS的条件:电流落后于电压,即Zin为感性--频率增加,阻抗增加!对于本控制IC-设计机理 LLC 需要满足ZVS的条件

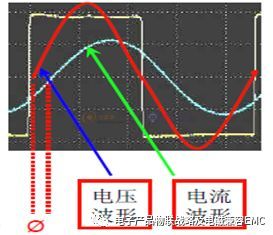

9.测试上述模型的关联相位>0Deg <40Deg 时 其设计补偿相位>30Deg <72Deg

在图中相位差Ø为0是感性&容性的分界线

ZVS的条件:电流落后于电压,即Zin为感性--频率增加,阻抗增加

10.在本设计IC应用中 PFC输入:380V-400V /输出160V/1.16A 工作平台;

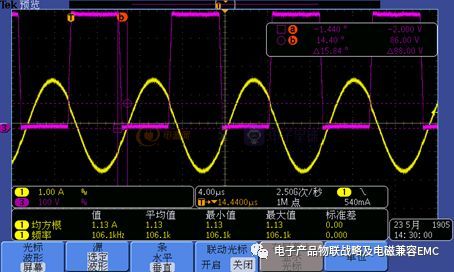

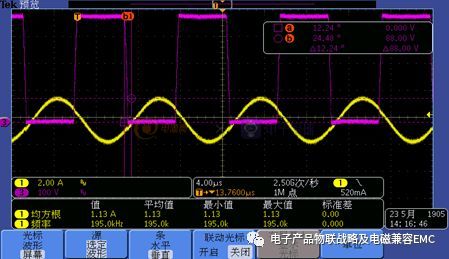

关联相位在不同谐振参数测试结果如下:

15.84Deg

12.24Deg

CH1:节点电流; CH3:节点电压

设计结果:Q=0.37 K=Lp/Lr=3.35-3.43 网路最大增益=1.2236 <1.8 is OK!

变压器工作模型相位差=12.24Deg/15.84Deg 补偿相位>30Deg <72Deg满足要求; is OK!

综合以上,我们可从以通过上述的设计软件及节点波形的测试来快速确定系统相位增益设计及系统稳定性!