在线路上用示波器测试地线时,如果电路板布局良好,大电流和高电压的伴地环路面积越少时,地线上的干扰毛刺基本不会存在。相反,如果违反基本的电路器件布局及高低压走线规则时,则会在系统上产生高频干扰,同时在正常的输出电压上就会产生电路的毛刺电压,即我们所说的噪声电压。这种噪声电压会噪声系统的复位及死机现象,严重时会噪声芯片的永久失效。

1.测试评估方法

用示波器直流电压档(或交流电压档)可选择参考地线用示波器的鳄鱼夹连接,信号端连接地线的不同位置。同时也可测试干扰源端地线布局的相同位置,同时评估地线上的干扰噪声电压的毛刺及尖峰的幅度。如果幅度及毛刺尖峰电压的时间既高且长时,这种干扰对电路的影响是致命的。还可使用示波器鳄鱼夹直接连接信号端组成一个感应环。用示波器直流电压档(或交流电压档)来检查周边器件的干扰辐射信号的强度。强度大的地方说明是信号的干扰源的发源地。从而查找干扰信号的大致位置再进行评估。

2.地线干扰信号的波形及参考

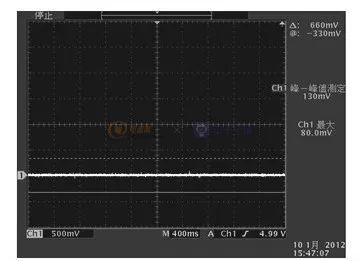

正常的地线干扰信号波形如下:

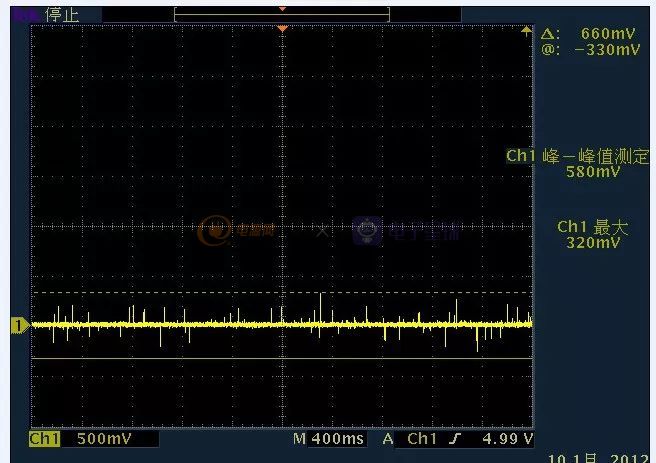

异常地线干扰噪声电压波形如下:

3.地线噪声干扰电压的案例分析

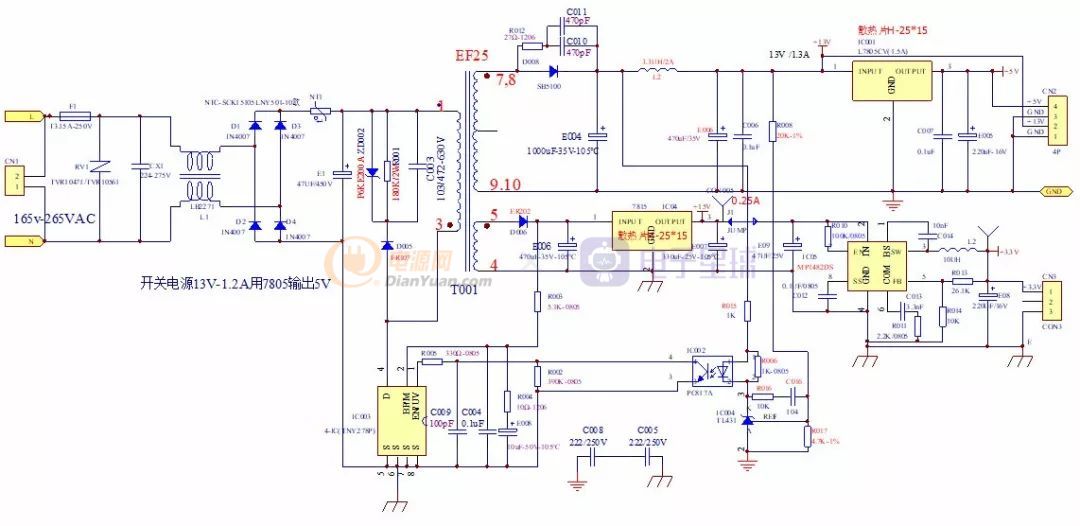

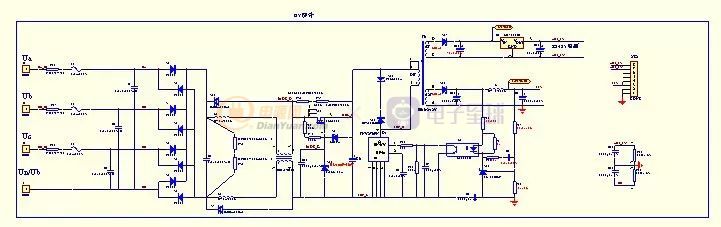

A.设计方案原理图

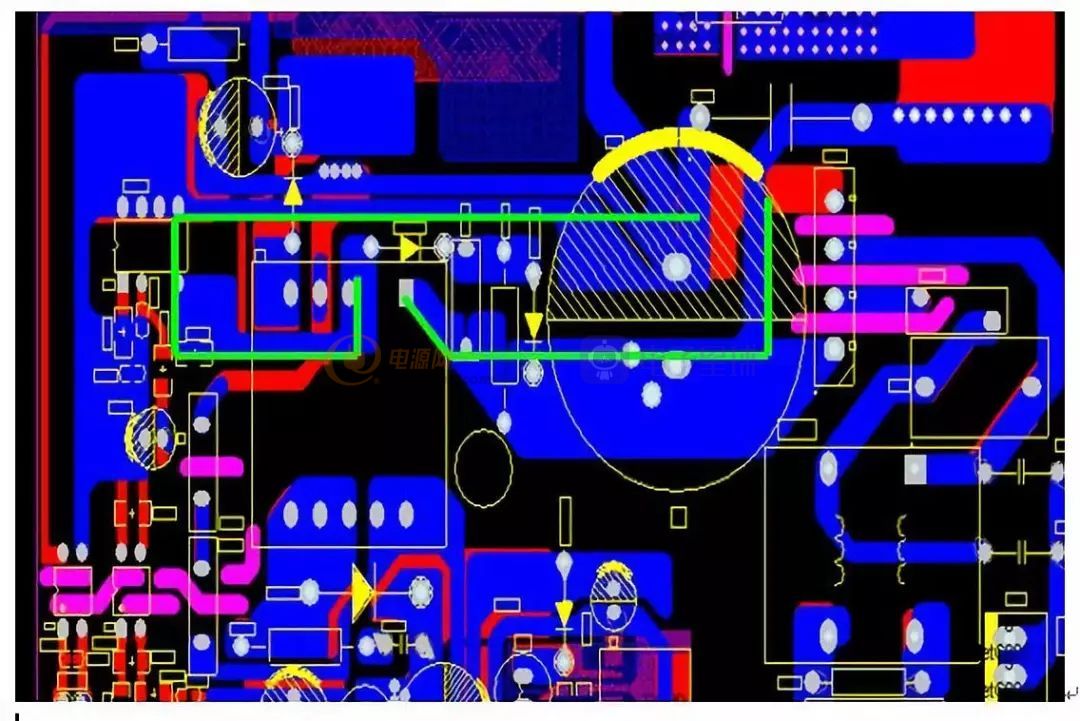

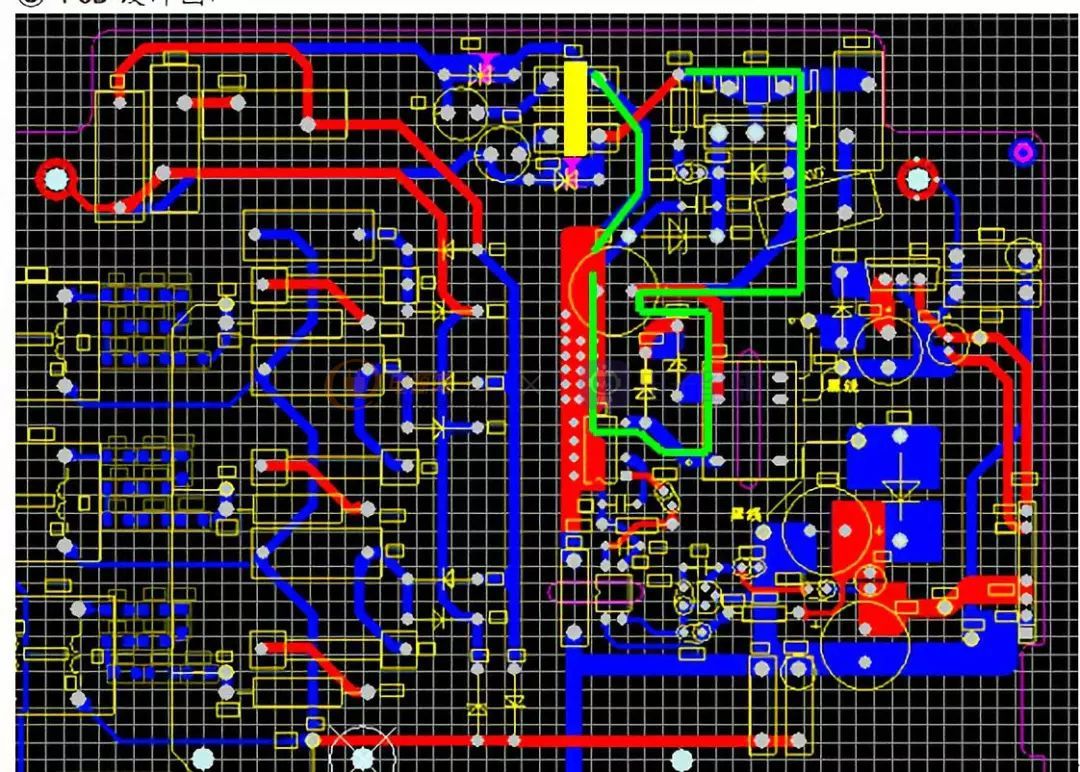

B.对应的PCB设计

说明:绿色包络是其主电路电流的环路面积。

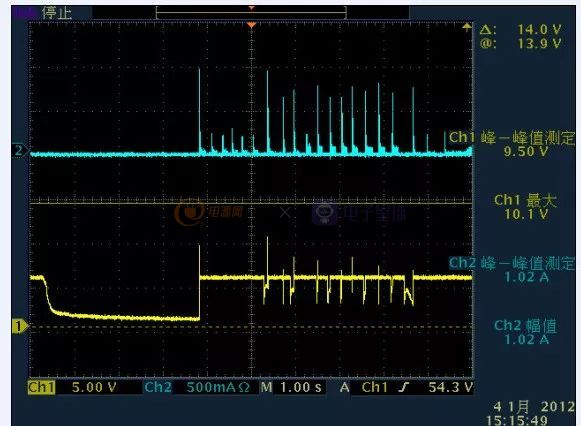

C.对电解电容的地线进行噪声电压测试-地线上存在较高的噪声电压!

D.测试开关芯片EN控制引脚在不同的地位置受干扰波形情况

说明:开关芯片的EN控制引脚出现较多的负电压现象!

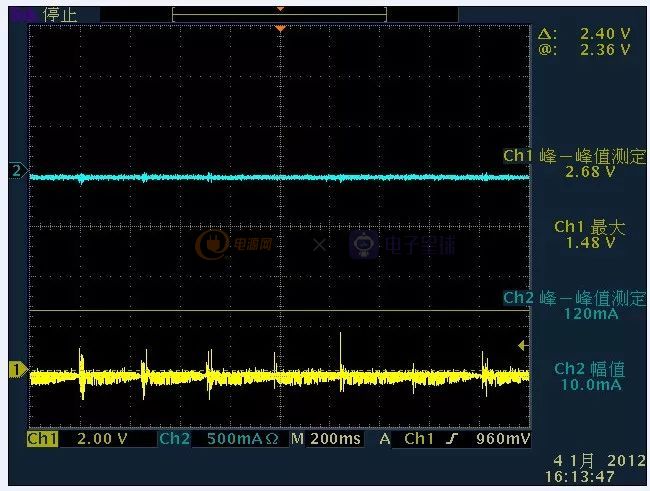

E.开关芯片的源极S脚与芯片EN引脚的控制波形

说明:其开关芯片EN控制脚的干扰电压消失。

因此:电路在进行PCB布局时要求开关芯片的源极S脚到主电解电容的地线的长度越短越好,阻抗越小越好(走线宽度要适当加宽)。

优化好的参考PCB设计如下图:

说明:其主电路环路面积小,地线短而粗。

F.电源带满载时,地线上的干扰电压测试情况如下:

说明:此时地线上基本没有噪声干扰电压。

因此合适的PCB器件布局会给电路的可靠性带来好处。

4.大功率器件的布局及地线铺设,产生地线的噪声电压的影响情况

A.设计方案原理图如下:

B.PCB设计图

说明:

⑴在电路中高压MOS及其控制电路是干扰源。

⑵开关芯片的主电流回路的环路面积还比较理想。

⑶降压MOS的走线电流环路面积过大。

⑷将电路进行开关电源芯片BP/M引脚的工作波形测试进行分析。

⑸将高压MOS的D,S脚短路不工作时开关芯片的BP/M引脚噪声电压消除

⑹在高压MOS回路中对地线的噪声电压进行测试分析评估,分析高压MOS在工作时的高频振荡情况。这种振荡已经造成芯片的锁死保护!

高压MOS在电路中时,电源往复启动时的开关芯片的BP/M引脚波形

绿色为高压MOS管的启动及工作电流

黄色为开关芯片的BP/M引脚的电压波形

说明:在电源系统在往复启动上电工作时电源有时会进入锁死保护状态。

开关芯片系列的特点及工作特性的资料。

1.流进BP/M脚的电流大于5mA且持续30 us以上时触发锁存关断功能。30 μs 的滤波可以防止由噪音或输入瞬态变化而引起的误触发

2.断开AC输入使得输入电容放电•当BP/M脚电压跌落到4.8V以下时锁存关断被重新复位。

C.短路高压MOS时的电源往复启动时的开关芯片的BP/M引脚波形:

绿色为高压MOS管的启动及工作电流

黄色为开关芯片的BP/M引脚的电压波形

说明:此时电源无锁存关断现象BP/M引脚消除了上冲的噪声电压。

D.对电源及高压MOS的地系统进行波形测试情况。

高压MOS在电路中,对主电解电容的地的波形测试

说明:在电路的结构上系统还存在地线的噪声干扰。

5.其它几种噪声波的形成及抑制措施

A.几种噪声波形

B.图示给出几种常见噪声波形。

现对这些噪声波的形成原因及相应的抑制措施简述如下:

(1) 噪声波形如图示(a)所示。

形成原因:辅助电源或基准电压稳定性不够所致。

抑制措施:在相关部位并大电容。

(2) 噪声波如图示(b)所示。

形成原因:布线不合理,引起交叉干扰。

抑制措施:调整布线。

(3) 噪声波形如图示(c)所示。

形成原因:由于变压器漏磁对采样形成干扰而引起自激,导致出现正弦振荡。抑制措施:变压器要适当加以屏蔽,且屏蔽层要接地。改进变压器绕制工艺。(4) 噪声波形如图示(d)所示。幅值变化随机、无规则。

形成原因:在于采样电阻所加电压过高或印制板绝缘不良。

抑制措施:改进采样。

(5) 噪声波形如图示(e)所示。

形成原因:整流二极管反向恢复期间引起的尖峰。

抑制措施:在二极管上并电容C或RC。

C. 上面几种方法已成功地运用于相关方案的验证上。

但由于产生尖峰干扰原因很多,因而其抑制措施也要视具体情况而定。只要对具体电路作出具体分析,找出干扰源,采取相应的抑制措施,就能取得较好的抑制效果,同时地线干扰噪声因PCB的设计问题,其噪声电压就会影响系统的可靠性设计了。