在很多嵌入式系统或者是低压供电端用的比较多,为了实现系统的小体积,目前市面上几MHz的buck变换器IC层出不穷,如此高的开关频率也会给系统带来一些扰动,尤其在传导和辐射方面。同步降压转换器的高频传导和辐射发射基于硬开关期间产生的瞬态电压 (dv/dt) 和瞬态电流 (di/dt) 发生。 这种电磁干扰 (EMI) 在设计和认证周期中是一个越来越令人烦恼的问题,尤其是考虑到功率 MOSFET 的开关速度增加。

先来分析高频回路是什么样子?

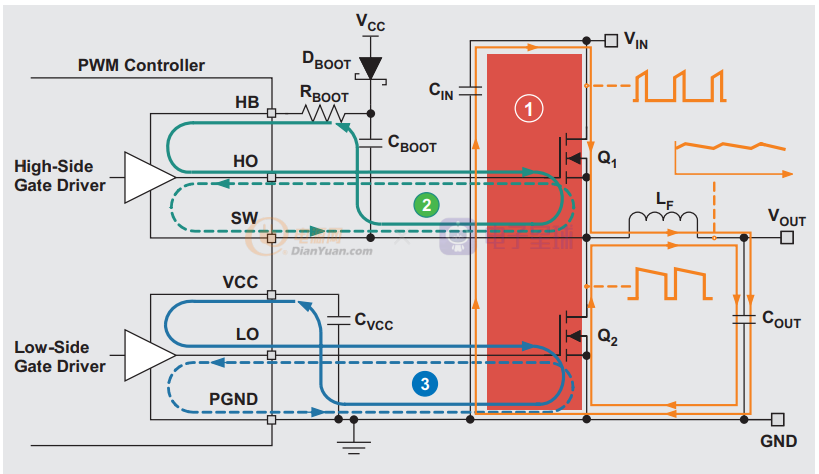

有效高频功率回路电感 LLOOP 是总漏极电感 LD 和共源电感 LS 的总和,由输入电容和 PCB 走线的串联电感LPCB以及封装电感产生 的功率 MOSFET。 正如预期的那样,功率环路电感与输入电容器-MOSFET 环路的布局高度相关,如图 1 中的红色阴影区域所示。

图1

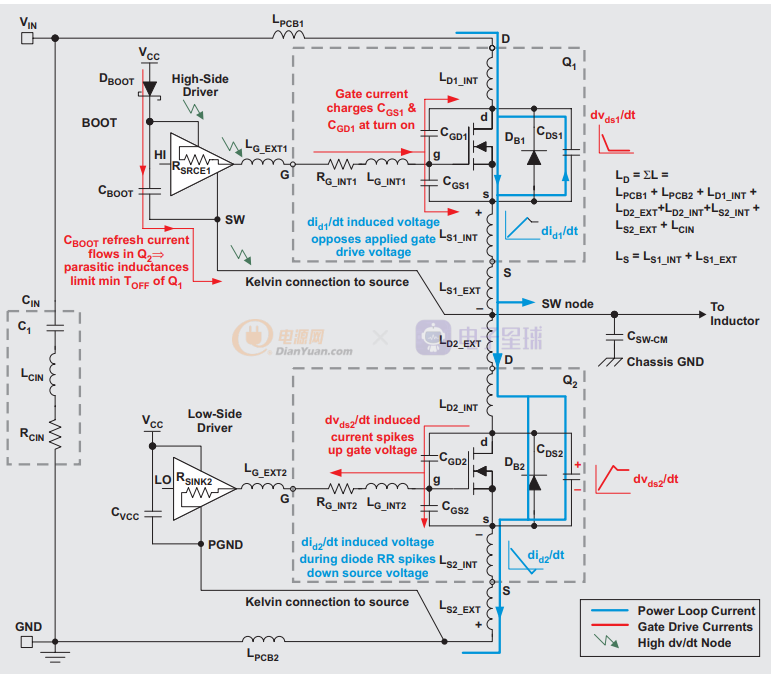

同时,栅极回路自感 LG 包括来自 MOSFET (主要是封装形式)和 PCB 走线布线的寄生参数影响。 对图 2 的检查表明,Q1 的共源电感在电源和栅极环路中都存在。 它会增加开关损耗,因为电源回路的 di/dt 会产生一个负反馈电压,阻碍栅源电压的上升和下降时间。 导致组件应力增加的另一个因素是 Q2 的共源电感,它会在体二极管反向恢复期间导致低侧 MOSFET 的误导通。

图2

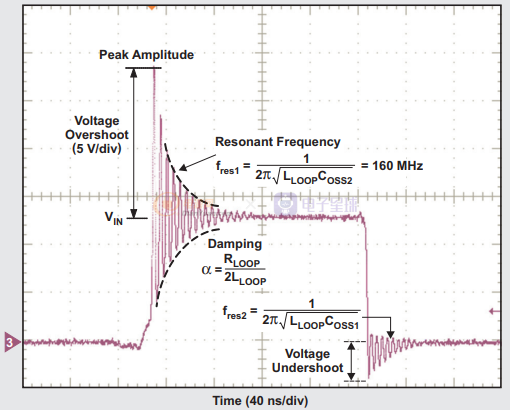

经过上图分析,基本可以确定高频噪声的来源就是回路中,杂散电容和电感之间谐振引起,那么我们再来分析一下等效电路,可以通过波形的变化来进行参数优化。图4中SW 电压波形,MOSFET 开关期间存储的寄生能量会激发谐振。

图4

高于 VIN 的开关电压过冲和低于接地 (GND) 的下冲分别在上升沿和下降沿期间很明显。 振荡幅度取决于环路内部分电感的分布,随后的振铃由有效环路交流电阻衰减。 这会导致 MOSFET 和栅极驱动器的电压应力,并且还与宽带辐射 EMI 的中心频率相关。

请注意,谐振期间的两个重要方面是谐振频率和该谐振处的损耗或阻尼因子。主要设计目标是通过最小化功率回路电感来尽可能高地推动谐振频率。这减少了存储的无功能量并降低了谐振峰值电压。 此外,由于趋肤效应,阻尼因子在较高频率处增加。

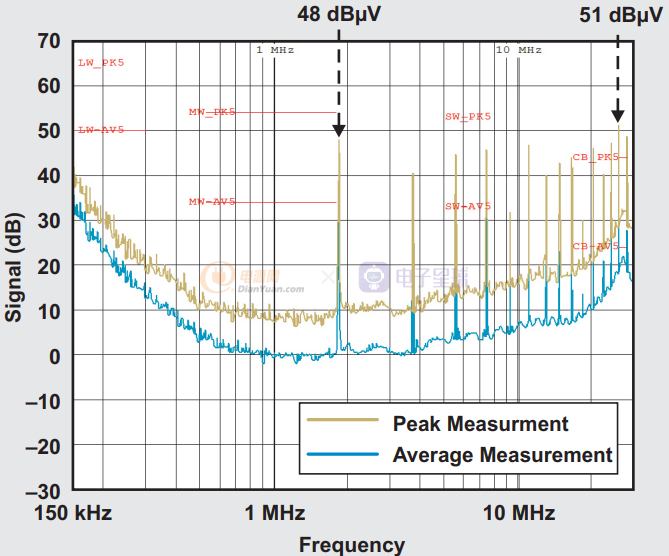

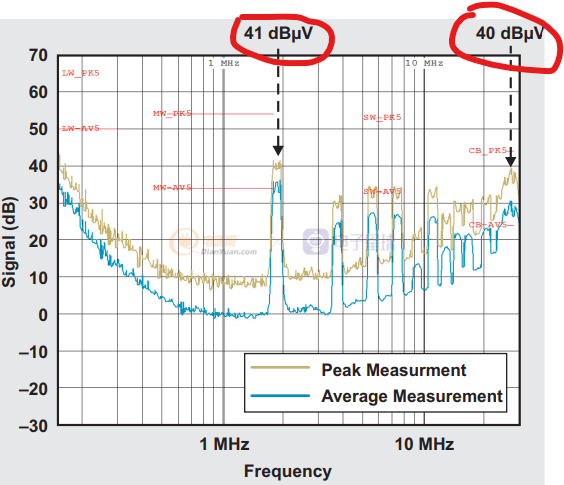

在该情况下,我们测试一下传导:150 kHz 至 30 MHz 的 CISPR 25 class 5传导发射测量

当 PCB 布局固定时,集成在同步降压控制器中的各种降噪功能在后期设计阶段处理 EMI 时最有用。 例如,不对称栅极驱动压摆率控制、外部时钟同步、内部振荡器和用于自适应调谐的动态跳频,以避免汽车控制系统中敏感的 AM 无线电频段。 在同步期间或当 DEMB/SYNC 引脚被拉低以降低噪声和射频干扰时,轻负载下的脉冲跳跃被禁止。为了增加可靠性,该器件的额定负 SW 节点和栅极驱动瞬态为 –5 V,持续时间长达 20 ns。在PCB布局中,应该尽可能减少功率回路,避免长走线,可以选择面积铺铜减少各回路。整改后测试看看效果。

整改后,使得满载时频率抖动,耗散高频能量,在频谱中就没有很高的能量峰值。另一方面减小回路面积,敷铜的意义在于会减小地线阻抗,提高抗干扰能力。