前面我们讨论了自举电容、正负驱动电容的取值方法,目前市面上很多PC电源所用低成本拓扑----双管正激用的比较多,还有移相全桥、双管反激等半桥或者是不对称半桥拓扑,那么对于这种拓扑我们所用的驱动就会涉及到隔离驱动器,涉及到隔离驱动我们就不得不去关注隔离驱动变压器如何去设计,驱动能力的大小取决于变压器设计的是否合理,那么这篇文章就会举例说明隔离驱动变压器的设计方法。

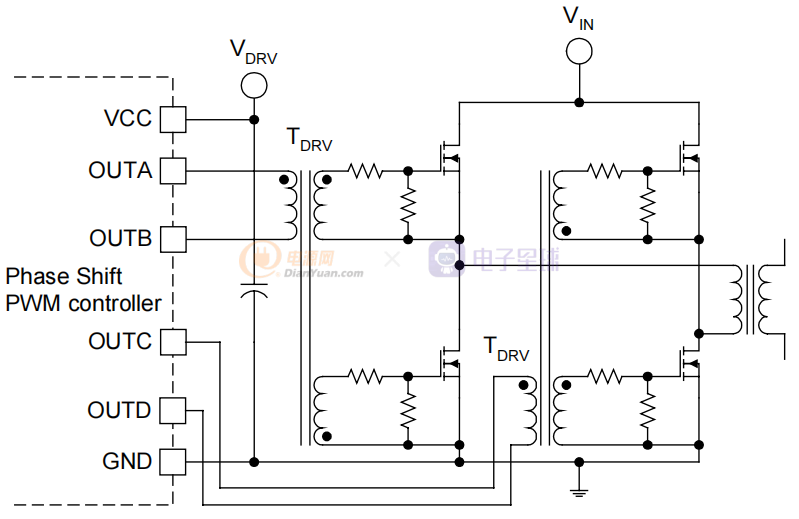

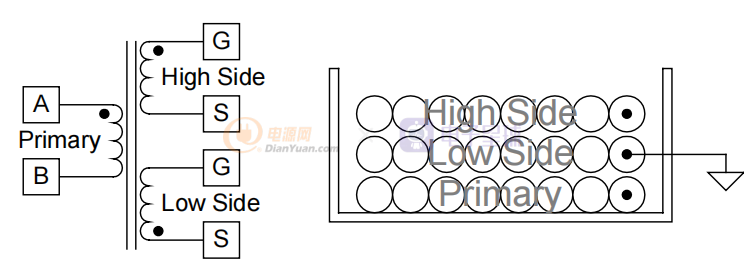

移相全桥变换器的栅极驱动变压器将根据以下示意图进行设计:

在此示例中,板上PWM 控制器具有四个大电流输出驱动器。 栅极驱动变压器设计基于以下信息:

fCLOCK=400kHz 时钟频率

fDRV=200kHz 驱动变压器工作频率

DMAX=0.5 驱动变压器最大占空比

VDRV=15V 驱动电压

第一个任务是选择磁芯尺寸。 经验丰富的设计师可以根据以前的经验为首次尝试选择合适的磁芯。 但即便如此,就像解决所有磁性问题一样,栅极驱动变压器设计可能需要几次迭代。 对于此应用,选择了无气隙的 Ferroxcube RM5/I 磁芯。 材料的首选选择是 3C94,因为它在可用选择中具有最高的磁导率和在 200kHz处具有最低损耗。

Ae=24.8mm2 磁芯有效截面积

Ve=574mm3 磁芯体积

BSAT=0.35T 磁芯材质磁饱和密度@100℃

AL=2µH/turns2 等效电感

BPEAK=0.1T 稳态运行时的峰值磁通密度。 请记住,在瞬态操作期间,由于占空比不均匀,变压器的磁通可能会移动。 通常,3:1 的余量是可取的。

∆B=0.2T 稳态运行中的峰峰值磁通密度

在这些情况下,从数据表中查找铁芯损耗。

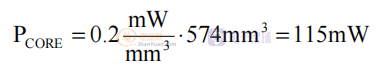

PV=200kW/m3 3C94 磁芯在BPEAK=0.1T 和 200kHz 的有效体积功耗。(为了清除计算可将单位转换至 0.2mW/mm3 )

PCORE = PV ⋅Ve

那么我们可以计算出磁芯损耗为:

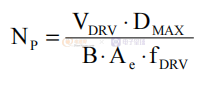

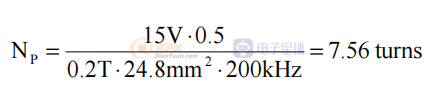

RM5/I 内核的功耗为 115mW,这是可以接受的。 接下来,根据以下公式计算初级匝数:

接下来,选择更高的整圈,NP=8 。 由于该栅极驱动变压器不需要电压调节,因此两个次级绕组也有 8 匝。 为了最小化漏感和交流绕组电阻,每个绕组应仅占据单层。 执行绕组设计需要以下数据:

Ww=4.7mm 线圈架数据表中的绕组宽度。

MLT=24.9mm 平均匝长也来自线圈架数据表。

考虑到终端N+1根线并排,对应的线径为:

根据美国线规表,最接近的较小直径线径是#25,其特征数据为:

dW=0.0199mils 重型(双重隔离)公称直径。 (0.0199mils=0.506mm)

ρW=32.37Ω/1000ft. 归一化导线电阻。 (32.37Ω/1000ft =0.1062mΩ/mm)

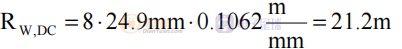

直流绕线电阻:

Rw,dc= NP ⋅MLT⋅ Ww

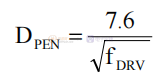

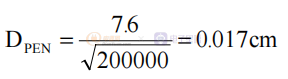

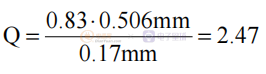

接下来,按照以下步骤根据 Dowell 曲线检查交流电阻:

查找 Q=2.5 的 Dowell 曲线图,单层曲线给出 RAC/RDC=3 的比值,因此绕组的交流电阻为 RAC=3⋅21.2mΩ=63.6mΩ,这是可以接受的。

最后一步是计算磁化电感和电流值:

基于磁通电流的有效值可以得到线损:

该结果表明绕组损耗在栅极驱动变压器中占比很小,几乎可以忽略。 高磁化电感和低绕组电阻是实现栅极驱动波形低压降的最关键设计参数。 另请注意,铜损完全基于交流电阻,因为在理想的稳态运行中,绕组中没有直流电流。

最后,变压器的绕组排列如下所示。 初级靠近中心柱,然后是低侧和高侧绕组。 所有绕组都在单层中。 低侧绕组用作天然屏蔽,防止信号接地和浮动电路之间的寄生电容电流。

后续文章,我会根据前面所讨论的一系列驱动设计问题,放在一个具有参考地和浮动地的有源钳位电路中逐步设计驱动电路例子,更好的展示驱动电路设计的过程和合理性。