经此一事,痛定思痛!以后做电源,变压器必须自己设计!要不然,自己吹亏还不知道!

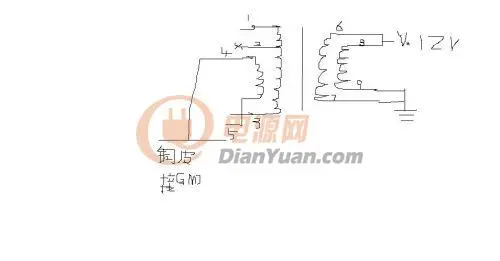

言归正传:现在这款电源,实测最大VDS高达580V。选用的MOS是8N60的,耐压600V。这样的情况肯定不行!目前的变压器匝数是:初级30匝,次级4匝。宽电压输入、输出12V/5A,初级电感480UH,吸收电路R:62K,电容10nf.初级漏感12UH左右。绕法是三明治绕法!磁芯是:PQ2620的。

在不更换MOS型号的条件下,怎样通过变压器设计的改动来实现把VDS降下来?

有意朋友建议我:减小圈数,扩大匝比!但是我很怀疑:用公式Vds max=Vin max + (Vo/Vd)/(N2/N1)。倘若把匝比扩大,VDS两端电压会更高!和变压器厂的工程师沟通了也是这个结果!

俺现在还不精于变压器设计!请路过的朋友帮忙出招!

谢谢!