大家好,我是砖一。

今天给大家分享一下上拉电阻和下拉电阻的实战应用,希望对你有用~

一,上拉/下拉电阻的定义

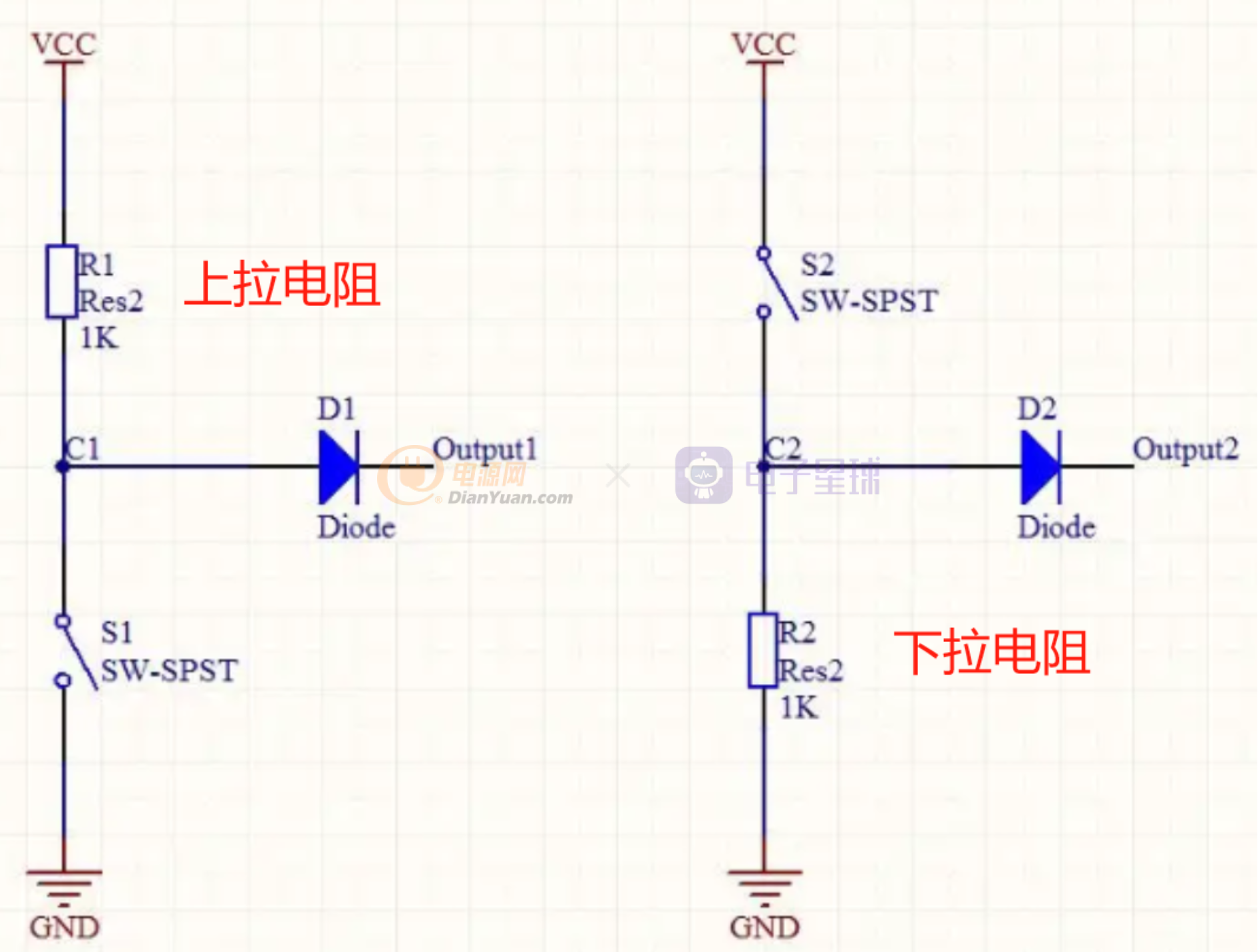

在我们元器件种类中,并没有实物的上拉和下拉电阻,为啥这样叫?是因为应用的功能不一样,从而决定它的名字哈,但是终归还是电阻。类似于电容中的旁路电容,使用环境定义名字,但是本身还是电容。请看下图。

左图中的 R1 直接与高电平 VCC 连接,让闲下来的电阻状态始终维持在高电平,这时电阻 R1 就是上拉电阻。

右图中的 R2 直接与低电平 GND 连接,让闲下来的电阻状态始终维持在低电平,这时电阻 R2 就是下拉电阻。

二,上拉/下拉电阻的应用

钳位

拉电流

增强抗干扰能力

阻抗匹配

2.1

钳位

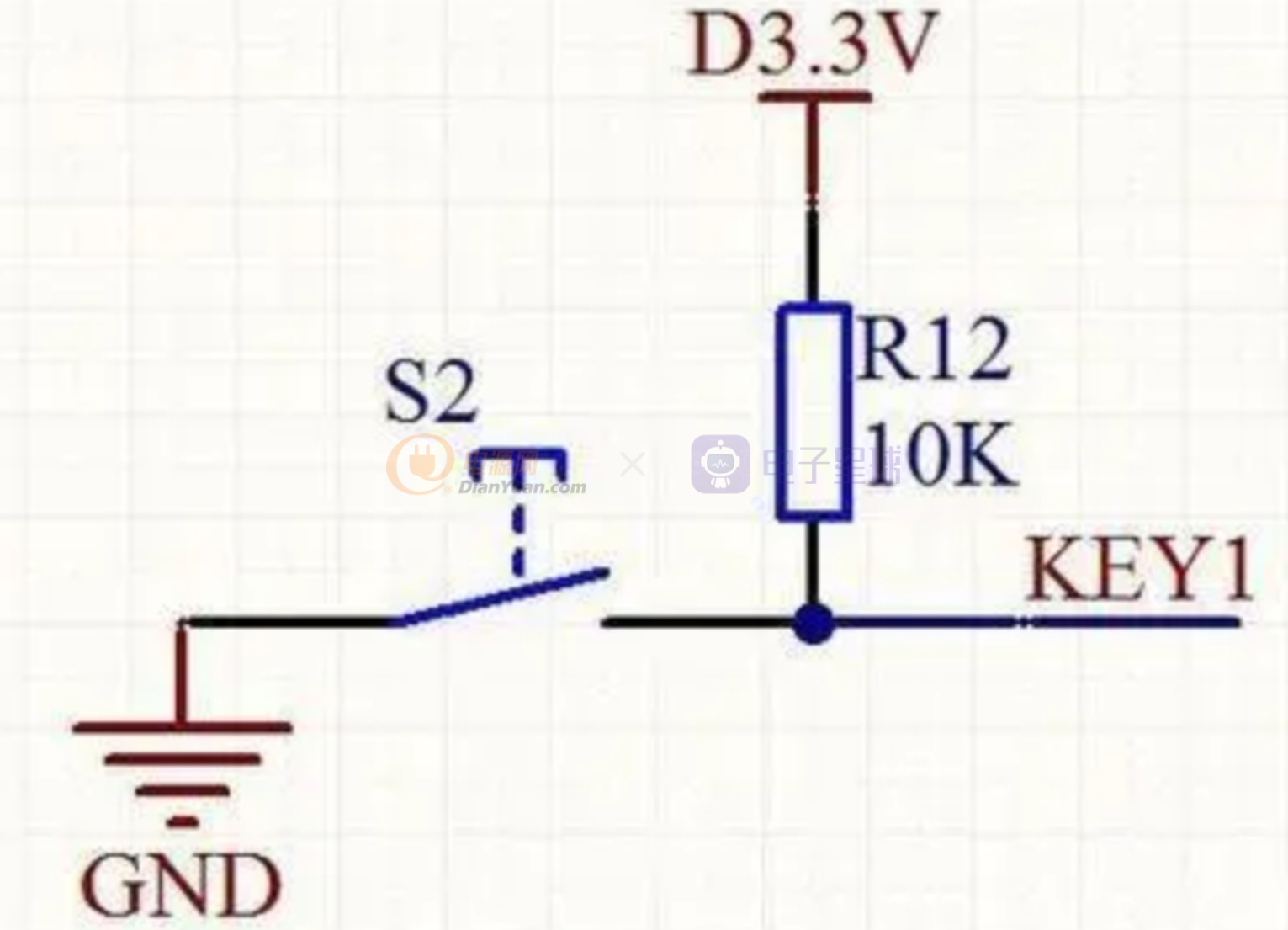

钳位,其实是使电平在一个稳定状态,上拉/下拉电阻比较常用的是这应用。

咱们首先要知道数字电路三种状态:高电平、低电平和高阻态(不确定状态),一些应用场景希望电平在上电开始时是高电平或低电平,不希望有高阻态的出现,那么就会使用上下拉电阻使管脚处于稳定的状态,同时也能实现限流作用,两全其美。

2.2

拉电流

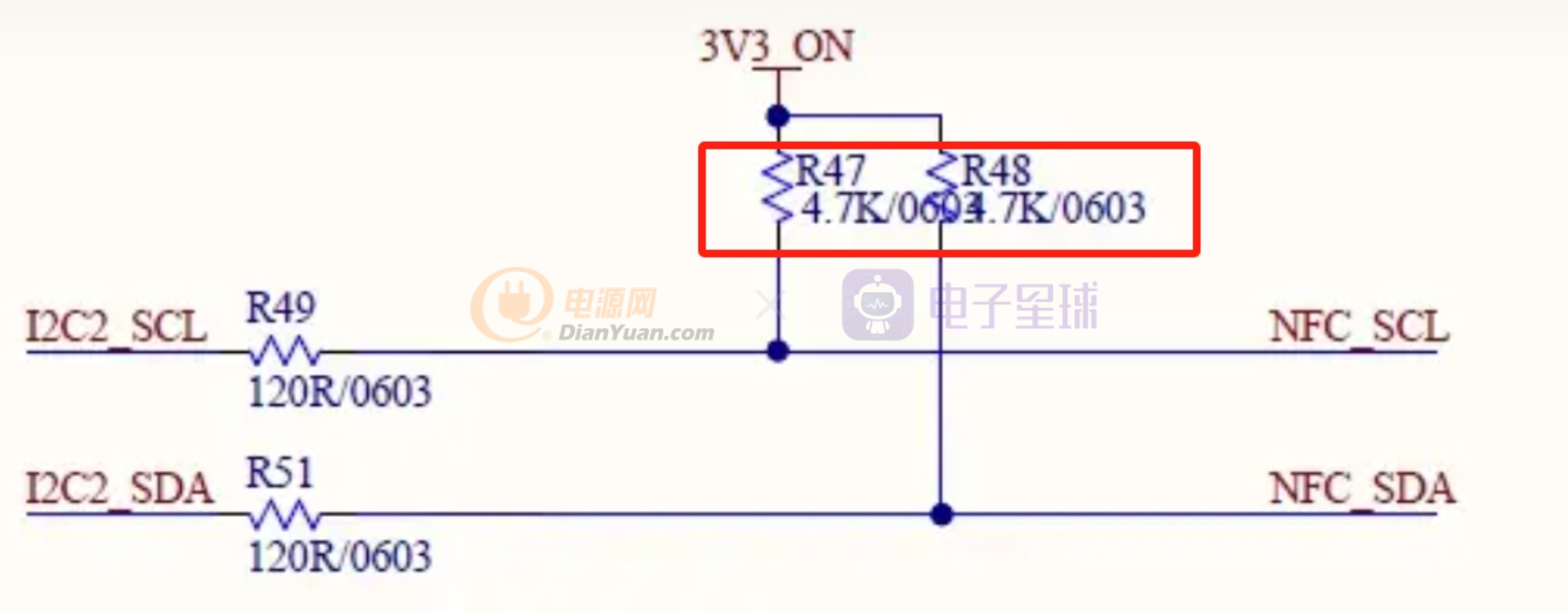

I²C 通信总线会有输出驱动能力不足的问题,那是因为 I²C 总线的输入输出结构采用的是开漏的结构, 而开漏结构不能够自主得到高电平,所以需要通过外部上拉电阻来的实现 I²C 通信过程中的高电平。上拉电阻的大小取决于 I²C 不同模式时的拉电流大小。

所以我们加上拉电阻可以增大电流,也叫拉电流(Source current);下拉电阻用来吸收电流,也叫灌电流(Sink current)。

2.3

增强抗干扰能力

为了防止静电对芯片造成损坏,一些 CMOS 芯片手册里,一些不使用的管脚会加上拉电阻,这样会提供泄放电荷的通路,从而提高芯片输入信号的噪声容限增强抗干扰能力,如下图 Layout 图 11-1(以德州仪器 TI 的 8 位移位寄存器 SN74HC65 为例讲解)。

2.4

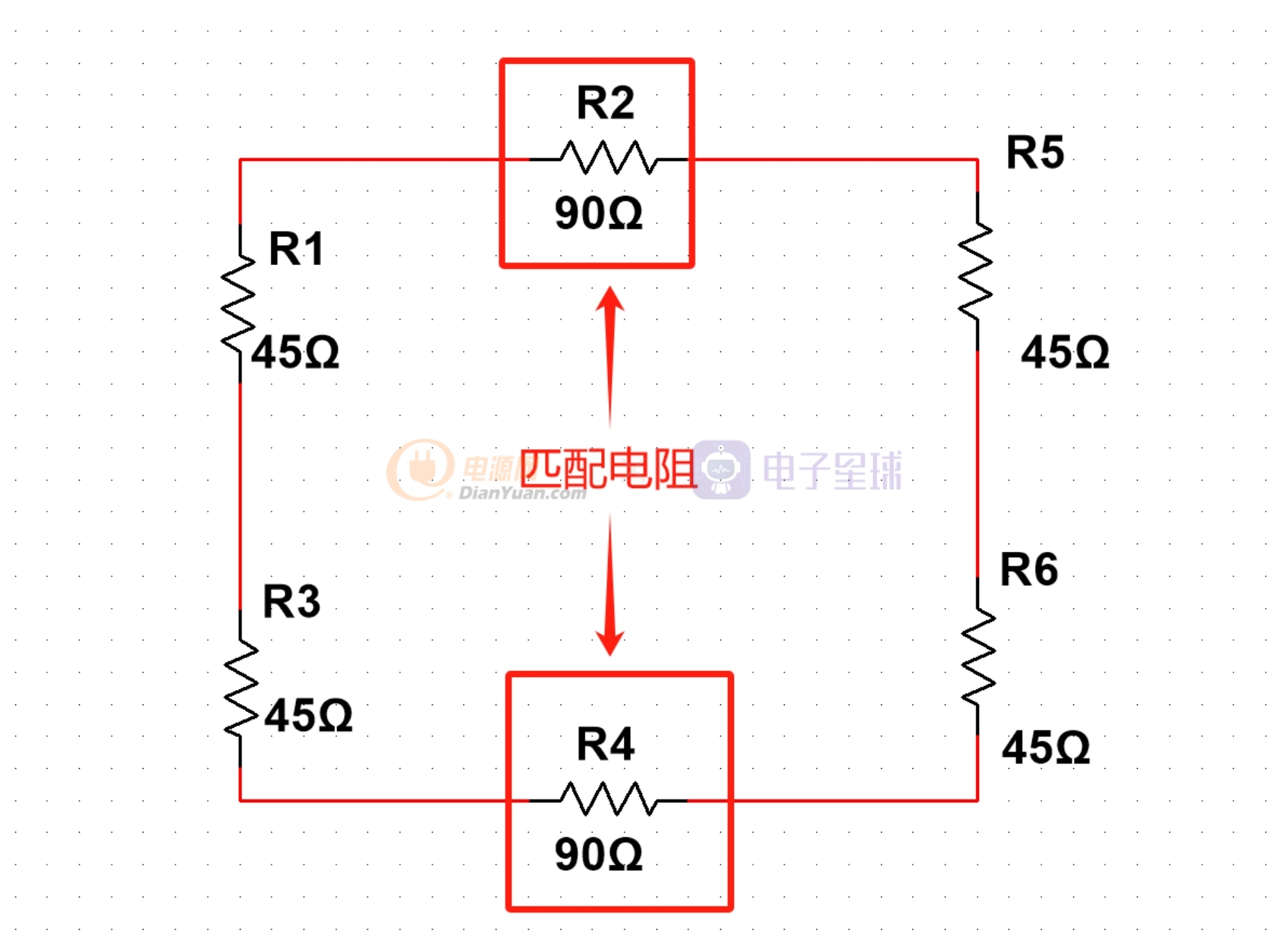

阻抗匹配

阻抗匹配,它是指通过调整输入阻抗和输出阻抗来使得电子器件满足一定条件,通常该条件是使得系统传输功率最大或者使得信号反射最小。例如,无线传输系统中需要匹配射频发射设备和接受天线的阻抗以此来实现传输功率最大化,这样我们会听广播的时候会更清晰。

三,阻值选择

一般来说,阻值都是老工程师的经验选择,上拉电阻阻值有 4.7k ,10k等。

(1)根据阻值不一样,上拉/下拉电阻可以分成强拉和弱拉。

拉电阻阻值越小,表示上下拉的能力也就越强,但是功耗也就越大。

(2)在高速电路中,过大的上拉电阻可能会导致信号的上升沿边沿不够陡峭,过小的上拉电阻可能会导致信号的低电平值增大,如果低电平比 0V 高,会导致低电平值被判为高电平导致数据出错,出现事故。

(3)如果对于内部本身自带的上下拉的 IO 口,若 IO 口带上拉,低功耗时可以将此引脚设置为高电平输出或者高阻,可以减少一部分的功耗;下拉同理,设置为低电平或者高阻减少功耗。

好了,今天的文章内容到这里就结束了,希望对你有帮助。

铁铁,我们下一期见,如果觉得我的文章还不错,请帮忙

三连支持点赞/在看/转发~