PI有很多反激电源方案,做的都很不错,要想设计好一款电源重要的掌握是对变压器特性,这次就来说说反激变压器漏感的影响。

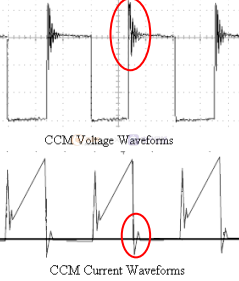

漏感是不能耦合到二次侧的电感,分布在变压器的整个线圈中,跟绕组是串联关系,因为能量不能向二次侧释放,所以会在开关管关断时刻会产生较大电压尖峰。

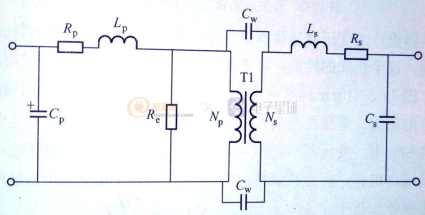

对反激变压器工作过程有影响的漏感,不仅仅包含初级不能耦合到次级的电感,还包含变压器二次绕组的漏感通过匝比折算到初级的漏感,以及布线所产生的电感,通过匝比折算到初级的电感即

漏感的影响:

漏感将使电路波形产生振荡,增加MOSFET的电压应力与发热,使电源的整体EMI性能变差。

抑制这个开关尖峰一般方法有:

(1) 增加Snubber电路,钳位峰值电压,并将部分的损耗转移 。

(2)优化变压器的绕制工艺,调整PCB Layout,达到漏感最小化的目的。

(3)选用窗口面积宽的磁芯骨架。