本文介绍用74373芯片进行微处理器IO口扩展的方法。

1.为什么要进行IO口扩展?

在电路设计的某些时候,微处理器(如单片机)IO口不够用了,此时该怎么办呢?利用辅助芯片进行IO口扩展是个简单直接的方法,能用较少的成本增多IO口。

2.常见的扩展方法有哪些?

IO扩展的方法一般有一下几种:

(1)利用串转并芯片扩展。这需要一个数据引脚一个时钟引脚,还需要若干控制引脚。

(2)利用锁存/缓存芯片进行扩展,如74373。这需要若干数据引脚和少量的控制引脚。

以上的方法都是可行。虽然用锁存/缓存芯片数据引脚消耗较多,但是其数据引脚可以由若干个锁存/缓存芯片分时复用,所以只需要控制少量的控制引脚就能使其扩展能力倍数级增长。

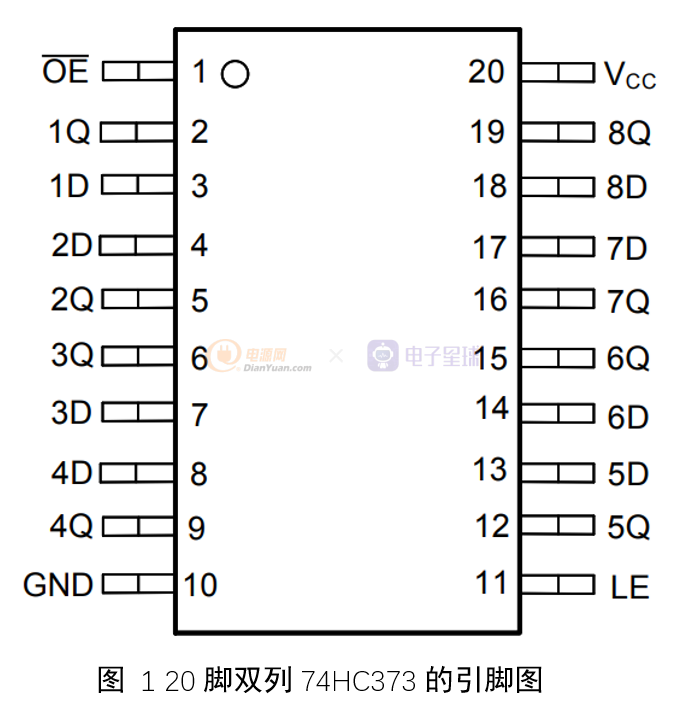

3.74373芯片介绍以及引脚定义?

74373一般有两种芯片,74LS373和74HC373。74LS373是TTL电路,74HC373是COMS电路,它们电平范围不一样,但两者实现的功能一样。本文以74HC373为例介绍。

74HC373是八路D 型锁存器,每个锁存器具有独立的D 型输入,以及适用于面向总线的应用的三态输出。所有锁存器共用一个锁存使能(LE)端和一个输出使能(OE)端。74HC373一般用于数字量信号锁存或缓存。

4.典型的扩展电路

4.1数字量输入扩展的原理和电路

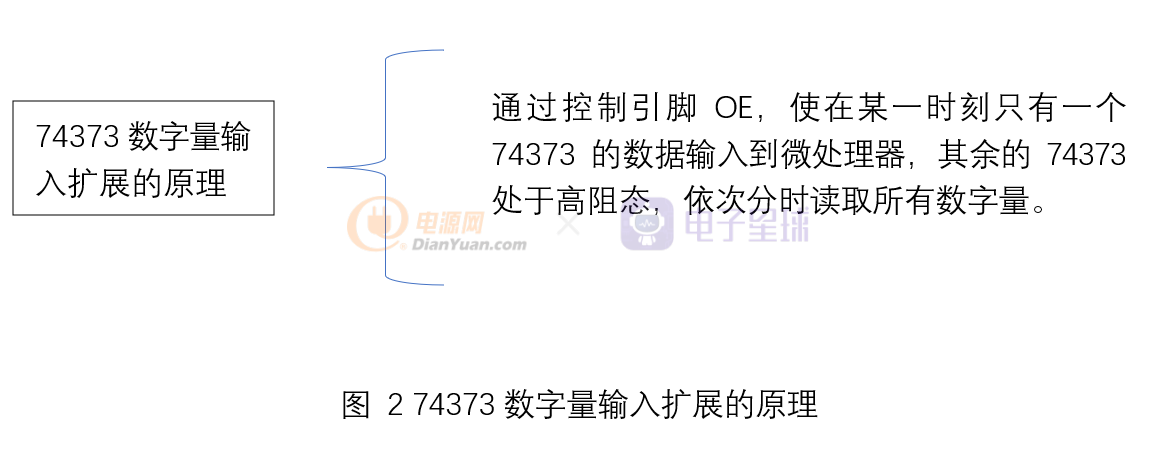

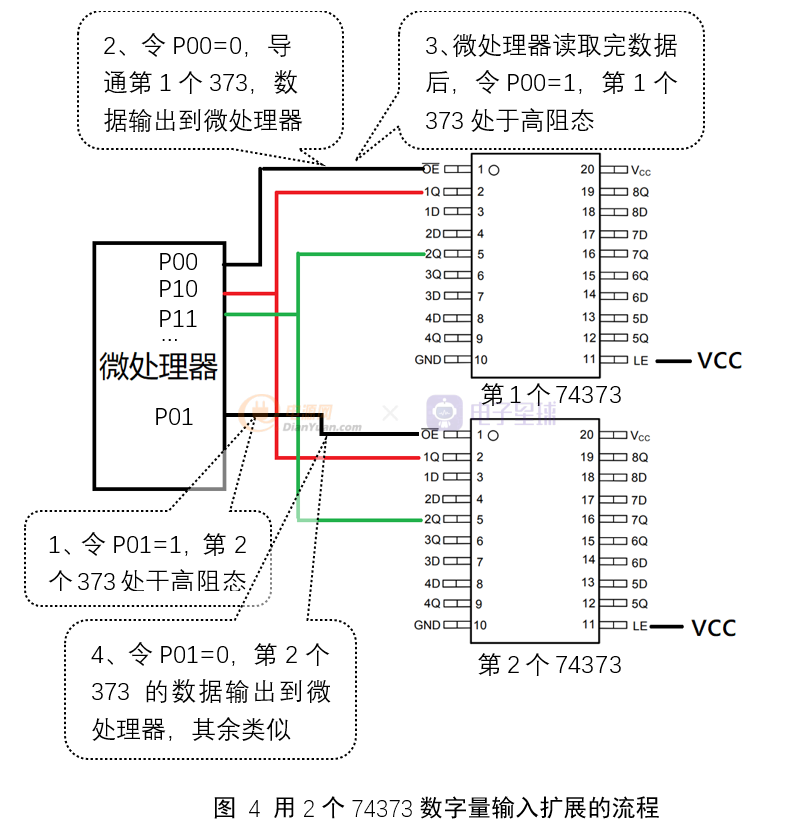

如图 3,为用2个74373扩展数字量IO口的电路,这个电路消耗了8个微处理器的IO口,达到了至少读取16个数字量的目的。如果再继续扩展,每新增一个74373,就可以多扩展8个数字量,很有优势。说明如下:

微处理器的引脚定义:

P00控制第1个74373的OE;

P01控制第2个74373的OE;

若干个74373的数据输出脚Q并联连接接入微处理器的P10- P17;

74373的D脚接来自外部的数字量,Q脚接微处理器,OE受微处理器控制;

74373的LE引脚接高电平使其进入随动模式。

扩展流程如下:

(1)、外部电路的1-8号数字量输入引脚接入第1个74373的输入引脚1D-8D, 外部电路的9-16号数字量输入引脚接入第2个74373的输入引脚1D-8D;

(2)、2个74373的输出引脚1Q-8Q并联后接入微处理器的P10-P17引脚;

(3)、用微处理器的P00控制第1个74373的OE, 用微处理器的P01控制第2个74373的OE;

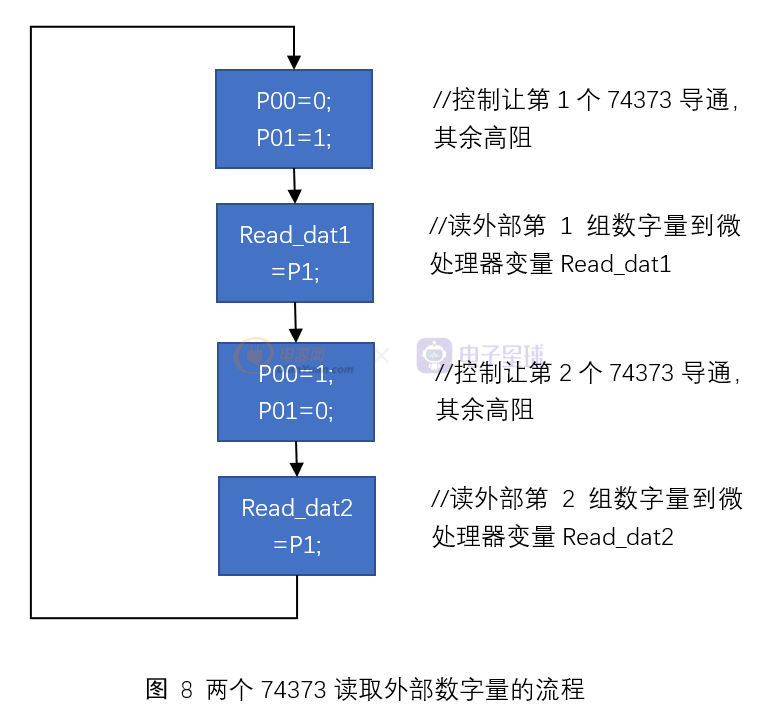

(4)、当微处理器要读取外部电路的1-8号数字量输入引脚时,令P00=0,P01=1,那么第1个74373的输出(对应1-8号外部数字量)会正常输入到微处理器,第2个74373的输出处于高阻状态,相当于断路。

当微处理器要读取外部电路的9-16号数字量输入引脚时,令P00=1,P01=0,那么第1个74373的输出处于高阻状态(相当于断路),第2个74373的输出(对应9-16号外部数字量)会正常输入到微处理器。

如此,实现数字量输入扩展。如果需要更多数字量输入扩展口类似操作即可,在后面,只需要多消耗一个IO口,就能获取8个扩展数字量。

注意,在某一时刻,只能有一个74373处于导通随变状态,其余必须处于高阻态,不然可能会产生电平冲突。

4.2数字量输出扩展的原理和电路

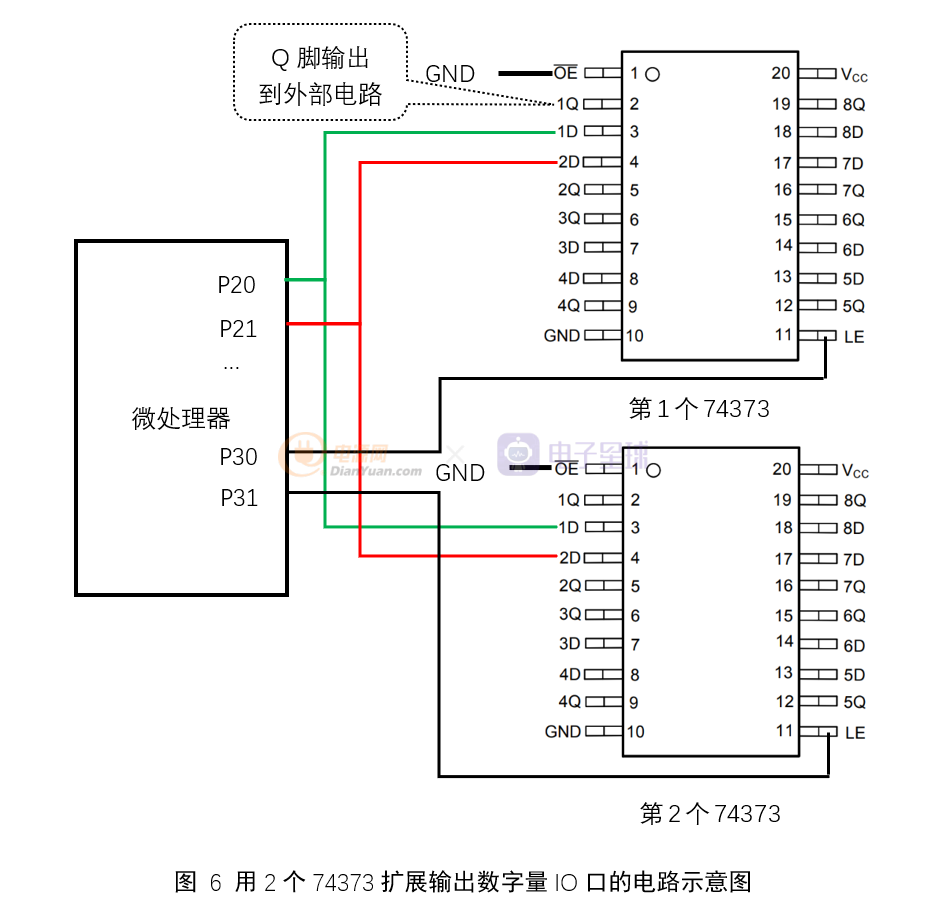

引脚定义:

若干个74373的数据输入引脚D并联连接接入微处理器的P20-P27;

74373的LE引脚受微处理器控制,OE引脚接地使其进入非锁存态;

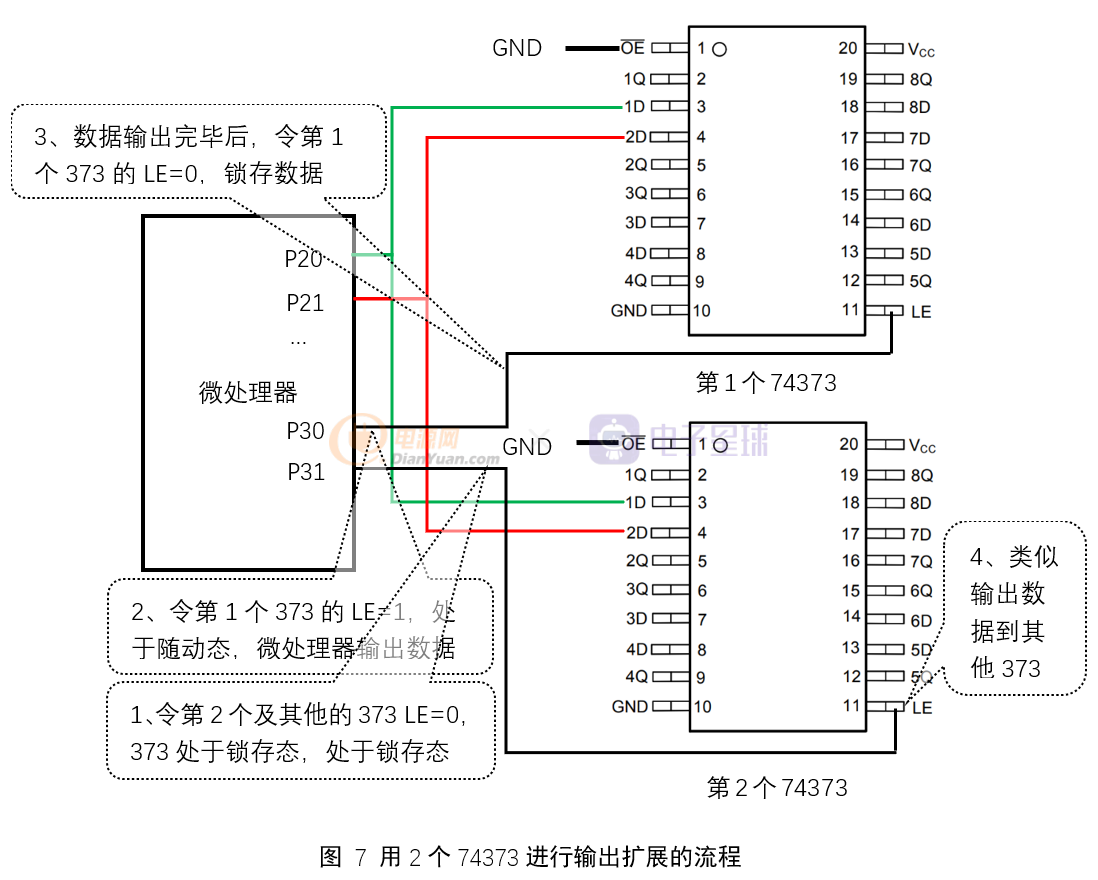

扩展流程如下:

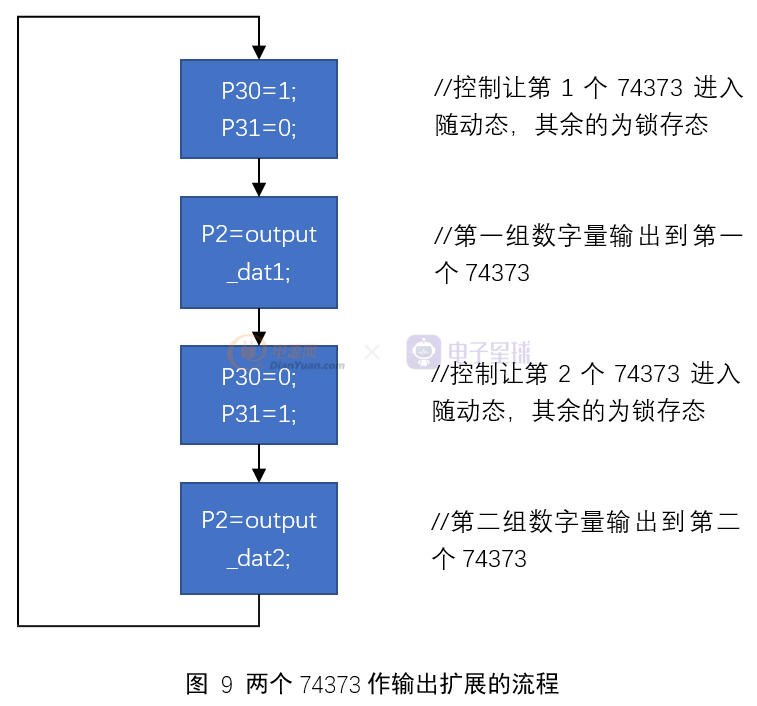

(1)、令第1个74373的LE=1,使其处于随动状态,并第2个及其他74373的LE=0,使其处于锁存状态;

(2)、微处理器把输出数据到第1个74373,输出完成后令LE=0,使第1个74373对微处理器传输来的数据进行锁存;

(3)、再使第2个74373的LE=1,使其处于随动状态,微处理器输出数据到第2个74373后再使LE=0令其锁存,这样,各个74373的输出位就保持了微处理器输出的数据,依次类似处理各个74373,达到输出扩展的目的。

74373的输出引脚Q,分别接到待控制的外部电路中。

5.典型的扩展程序流程

5.1数字量输入扩展的程序流程

数字量输入扩展的程序流程参考4.1中的过程描述,电路图参考图 3。程序流程图如下:

5.2数字量输出扩展的程序流程

数字量输出扩展的程序流程参考4.2中的过程描述,电路参考图 5。参考程序流程如下:

以上为利用74373进行数字量扩展的要点,关键是用好用作输入时对OE引脚的控制,用作输出时对LE引脚的控制。每次操作的最小数据单元为8位,即一个字节。

完。