随着FPGA性能越来越强,数采链路越来越复杂,供电系统就成为系统的一个需要特殊注意点。

对于系统设计人员来说,由于数字处理系统的采样带宽越来越宽。出于环境和成本方面的考虑,系统设计人员不断尝试降低总功耗。一般而言,ADC 制造商建议采用低噪声LDO(低压差)稳压器为GSPS(或RF 采样)ADC 供电,以便达到最高性能。然而,这种方式的输电网络 (PDN) 效率不高。设计人员对于使用开关稳压器直接为GSPS ADC 供电且不会大幅降低ADC 性能的方法呼声渐高。

解决方案是谨慎地进行PDN 部署和布局布线,确保ADC 性能不受影响。讨论了线性和开关电源的不同之处,并表明GSPSADC 与DC-DC 转换器搭配使用可大幅改善系统能效,且不会影响ADC 性能。

高带宽、高采样速率ADC(或GSPS ADC)可以具有多个电源域(比如AVDD 或DVDD)。特别是相控阵领域,可能出现多达10+、100+乃至K级的电源域。

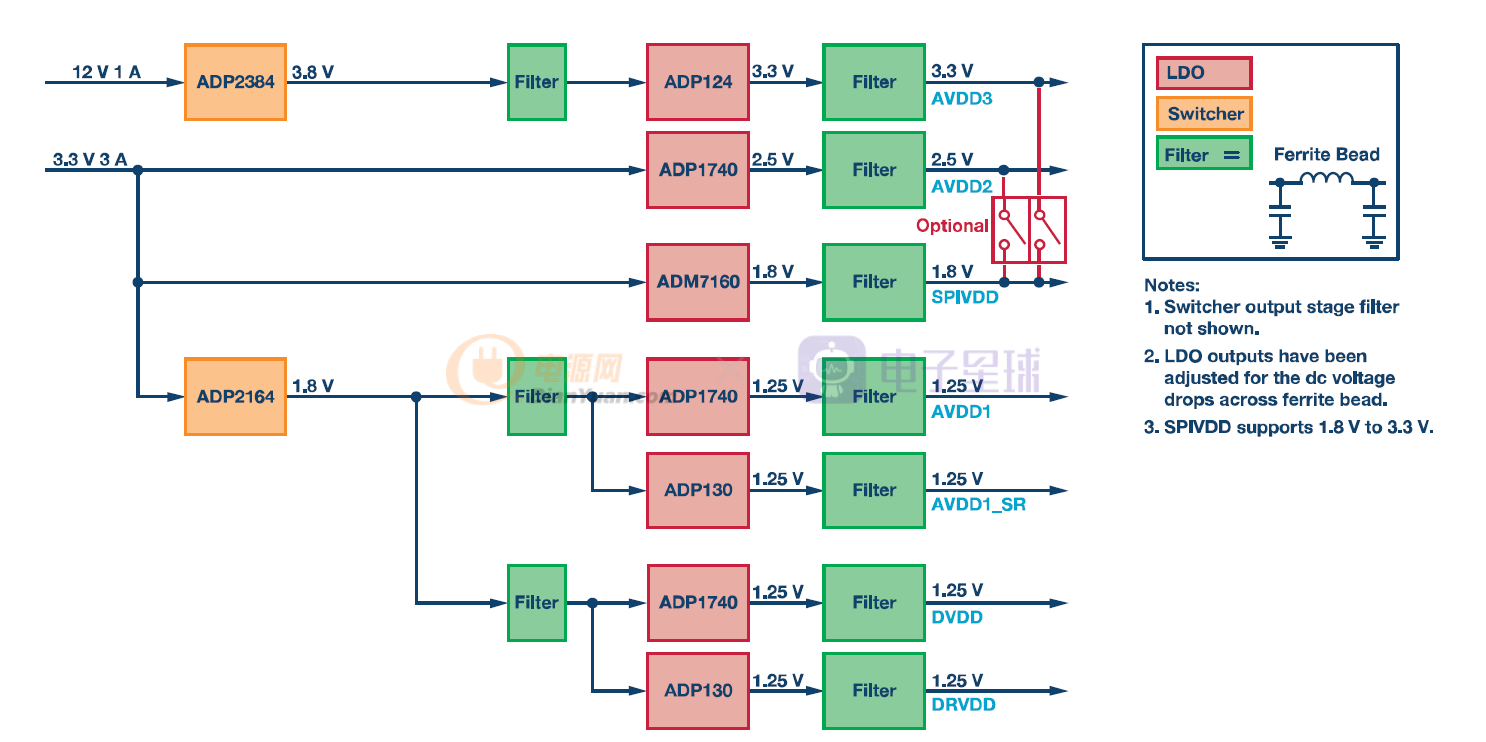

图示是AD96802:一款14 位、1.25 GSPS/1 GSPS/820MSPS/500 MSPS JESD204B 双通道模数转换器,采用65 nmCMOS 工艺制造。这款GSPS ADC 具有7 个不同的域(AVDD1、AVDD1_SR、AVDD2、AVDD3、DVDD、DRVDD 和SPIVDD),以及3 个不同的电压:1.25 V、2.5 V 和3.3 V。ADP23843 和ADP21644 DC-DC 转换器用于使电压下降到可控水平,以便LDO 能够在不进入热关断的情况下进行稳压操作。这些电源域和各种电压的日益普及是在这些采样速率下工作所必需的。它们可以确保各种电路域(比如采样、时钟、数字和串行器)之间具有正确的隔离,同时使性能最优。正是因为这个原因,ADC 制造商才设计了评估板,并推荐详细的电源设计方案,确保最大程度降低风险,使性能最大化。例如,图1 显示了AD9680评估板使用的默认PDN 的功能框图。根据Vita57.1 规格,电源输入来自FMC(FPGA 夹层卡)连接器供应的12 V/1 A 和3.3 V/3 A电源。

显而易见,这是一种昂贵的解决方案,有7 个LDO 稳压器,每个域一个。这款PDN 也许是性能最优的,但肯定不是最具性价比或运行成本效率最高的。系统设计人员认为部署含有多个ADC 的系统非常有难度。例如,相控阵雷达方案包含成百个AD9680,全都以同步方式工作。要求系统设计人员为上百个ADC的每一个电压域都分配一个LDO 稳压器是不合理的。

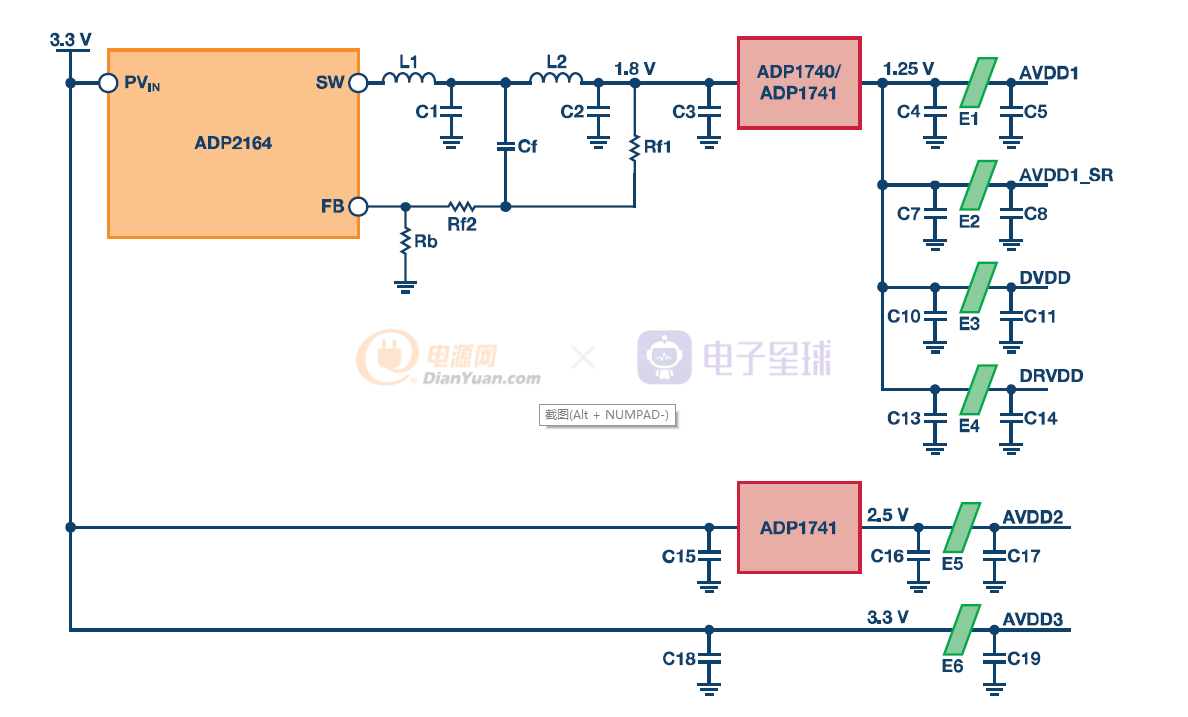

一种更具性价比的PDN 设计方案是将具有同样电压值(比如所有的1.25 V 模拟域)的域组合起来,然后用同一个LDO 来驱动。这样可以减少元件数(以及物料清单—BOM—成本),如下图所示。

当然,我们还有更进一步的优化方案,这个就需要我们均衡考虑了。此文抛砖引玉,希望能有更多的讨论与分析。