LLC电路DC特性修正方程探讨-电源网 https://www.dianyuan.com/bbs/2449603.html

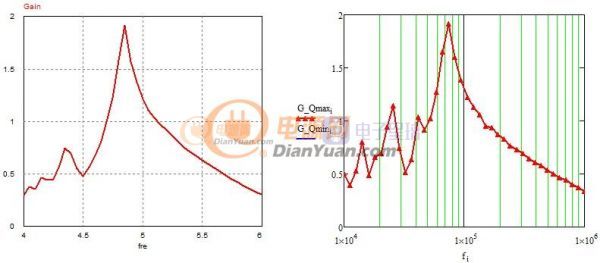

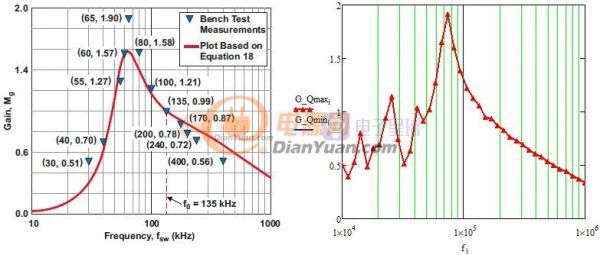

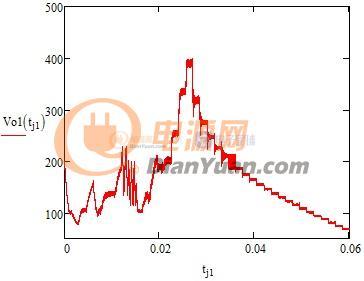

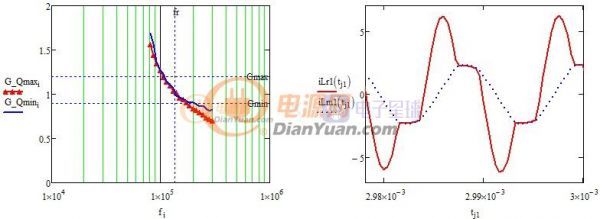

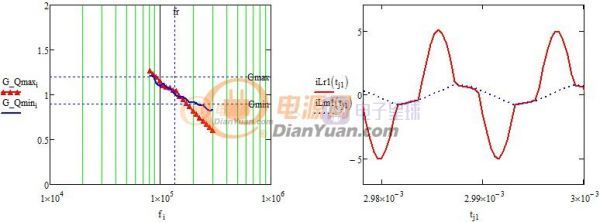

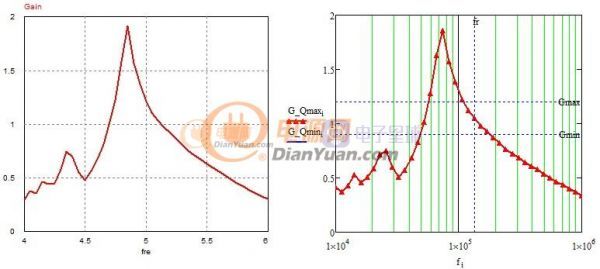

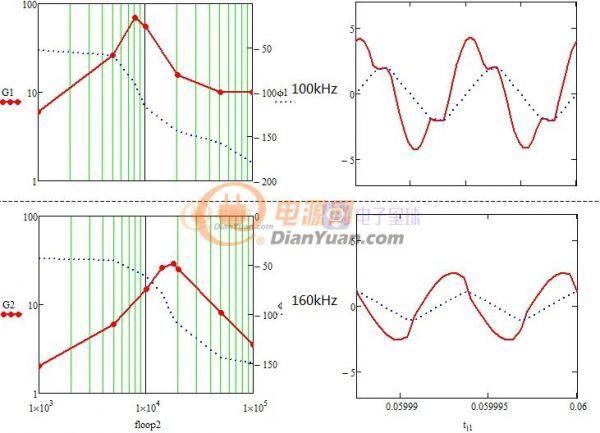

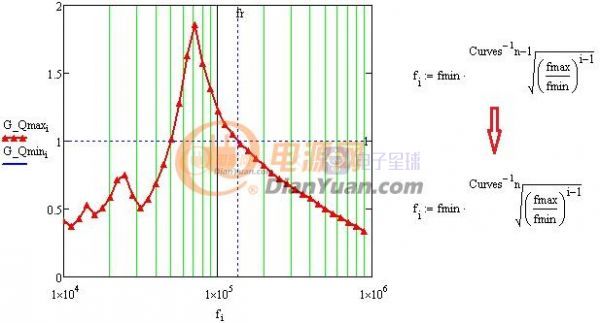

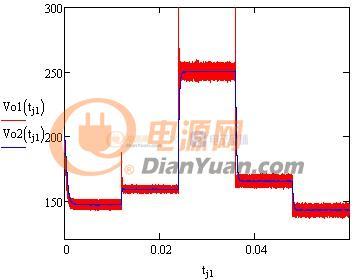

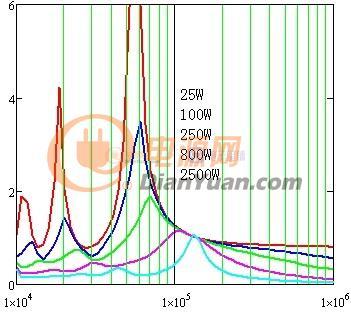

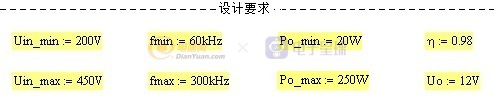

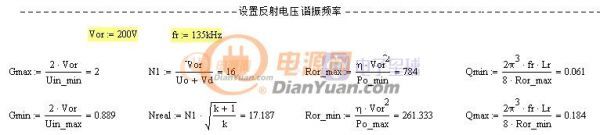

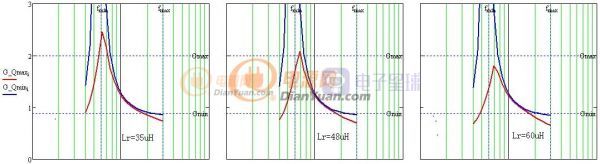

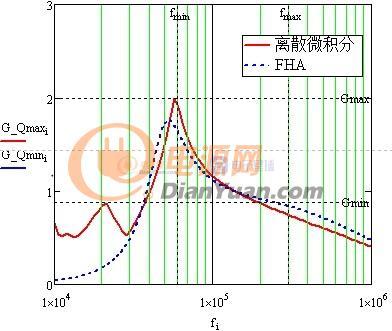

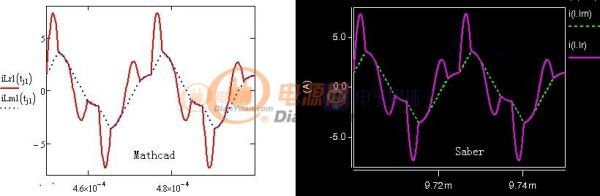

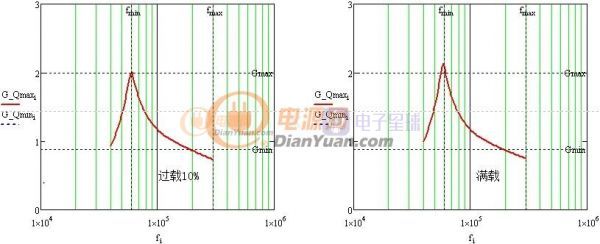

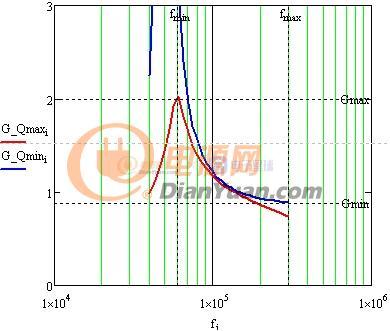

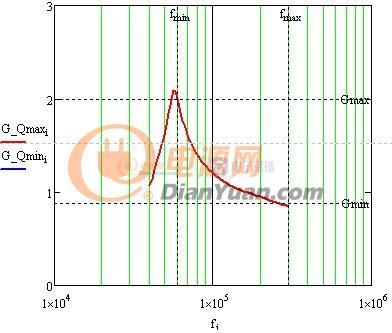

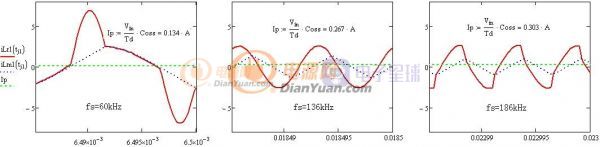

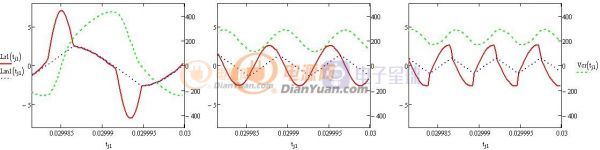

在上述帖子中采用多段正弦波拼接够成LLC波形,由于包含超越方程没能得出解析解所以整个运算下来速度并不快。这里还有一个采用解离散微积分的方法,限于水平结果还不够精准,方法先分享出来以后再做改进。

LLC_DC增益Rev01.rar(Mathcad文件)

LLC_DC增益Rev02.rar(Mathcad文件,修正了表达式)

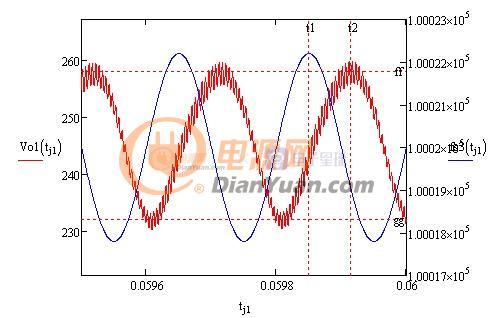

LLC_DC增益Rev03.rar (修正穿越频率处增益不为1的问题,输出增加低通滤波器)