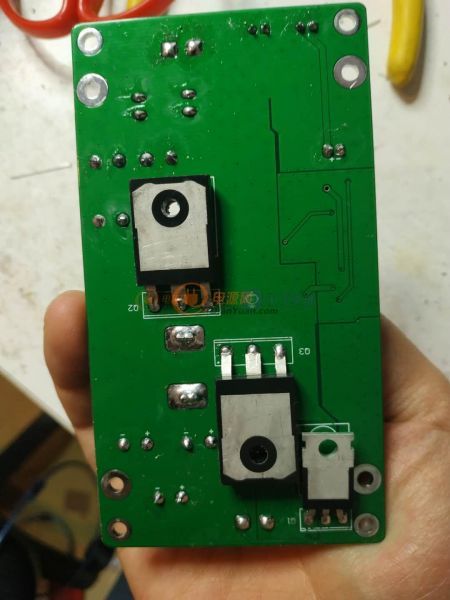

小弟近期设计了一款恒压横流充电模块,成品出来后带载能力差,带载1A输出电压即被拉低1V,请教各位前辈是哪里出的问题。

附件PDF为原理图,输入dc36V,输出29.4V,横流阶段最大电流15A.拓扑为降压同步半桥 。现在问题是带载能力问题,横流正常。请各位前辈不吝赐教。

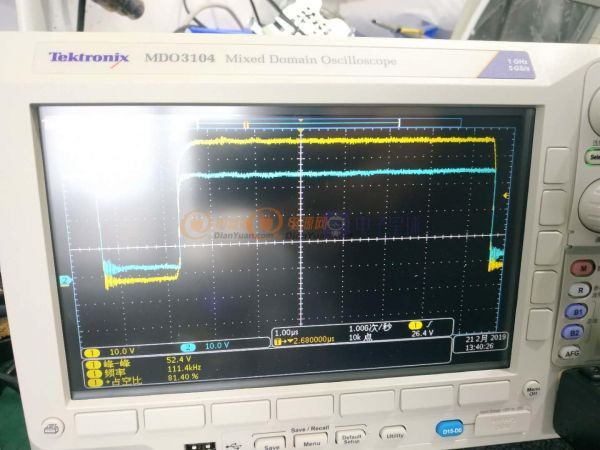

这是高端mos GS波形

小弟近期设计了一款恒压横流充电模块,成品出来后带载能力差,带载1A输出电压即被拉低1V,请教各位前辈是哪里出的问题。

附件PDF为原理图,输入dc36V,输出29.4V,横流阶段最大电流15A.拓扑为降压同步半桥 。现在问题是带载能力问题,横流正常。请各位前辈不吝赐教。

这是高端mos GS波形