0和1的故事-2

市面上铺天盖地的是各类功能芯片,做单片机开发的工程师应该更有体会.需要什么功能,只需要增加相应的集成芯片就行了,至于说芯片的工作原理,也就仅仅局限在技术手册层面的理解吧.

都知道数字电路其实就只有两个状态,开和关.但是几乎所有的数字系统都是由开和关组成的,这就是数字电路的力量,也是它深深吸引我的地方.

我想把数字电路的学习研究当作自己的业余爱好,慢慢地学,慢慢地练,一点一点的积累自己的技术,不急躁,不浮躁,打呆仗,打硬仗,这样走下去总会有一点收获吧.

和诸位有此志向的朋友们共勉.

先将准备写的知识点罗列出来吧,这一帖想接着<<【我是工程师第四季】0和1的故事>>继续写.先期准备先写一点通过三极管实现各类门电路,接着准备通过各类逻辑门电路组建常规的功能电路,诸如计数器,加法器,锁存器,触发器,存储器,译码器,移位寄存器,存储器等数字电路,最终目的是想通过各类逻辑电路搭建出一个简易的CPU出来.

工程量非常大,权当自己的业余爱好,这样没有压力,应该可以长久的坚持下来.

逻辑门电路搭建CPU,目前主流的方法是通过FPGA实现,需要掌握VERLOG语言,直接用逻辑门电路制作CPU周期长,费时费力。不过我还是想先用逻辑门电路搭出来,这样对于底层的原理会理解的更加透彻深刻。

先从最基本的逻辑门电路的实现开始吧,有兴趣的朋友可以一起学习。越来越觉得把电子技术当作爱好比当作谋生的手段能够走的更远,走的更长。

欢迎大家一起讨论学习数字电路的知识点,以前我认识的工程师给我灌输的观点是模拟电路难学,数字电路简单。其实真实的情况并不是如此,数字电路个人认为非常的繁琐,和模拟电路比较,有过之而无不及。简简单单的两个状态开和关或者说零和一就可以几乎囊括了电子世界的大半个江山,这简单吗,很显然不简单。说数字电路简单的朋友,其实大多数人对于数字电路的理解仅仅是门外汉都算不上的层次。

广大的电源工程师其实很多人都不懂数字电路,至于底层驱动的编程,CPU结构的理解,RSIC架构和CSIC架构的区别,不同指令集的理解等等,其实几乎都不懂,很多人连涉及的层次都达不到,仅仅是根据自己的理解就大言不惭的告诉新手们,数字电路简单。个人觉得这是对广大新手能力的扼杀,同时也是对刚入门的新人的极大的不负责任。

接下来准备写点用逻辑门组成的时序逻辑和组合逻辑电路,常规的各类触发器等等。慢慢写,学习鸿哥好榜样,用一辈子的时间去学习,去写帖子,写高质量的帖子,帮助更多的迷茫的新人们,同时也希望诸多老鸟们能一起加入进来共同讨论学习,谢谢。

曾经的我很迷茫,也理解新手们刚步入这个行业的痛楚,希望通过自己的努力能够将电子技术写的通俗大众一点,帮助更多的后来者扫清入门阶段的障碍。限于自己的水平,我自己遇到很多问题,也是边写边学边练。我想只要勤奋,总能在电子技术有所收获吧。

努力,和有志于电子技术行业的朋友们共勉。

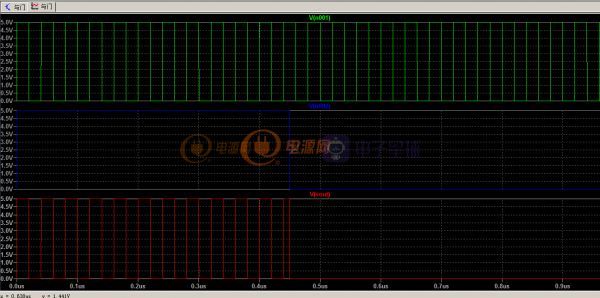

针对与,或,非门再进行一些补充吧。

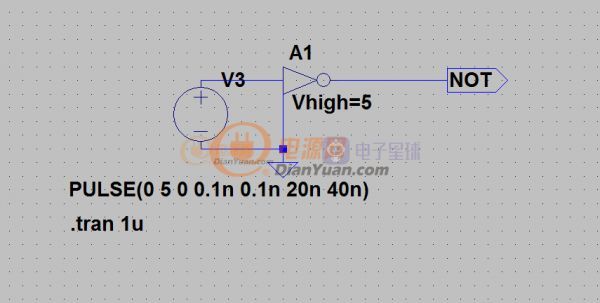

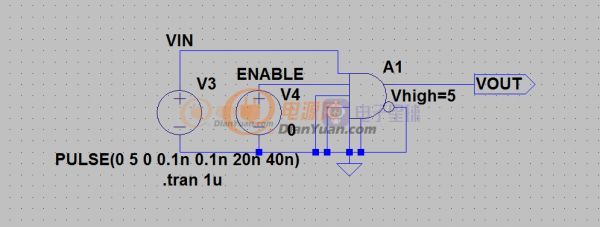

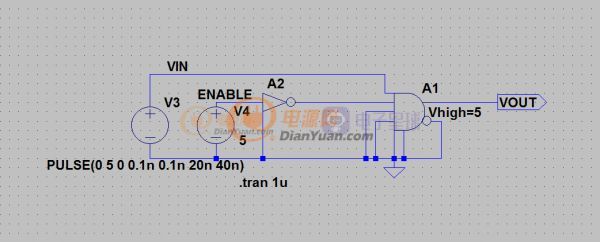

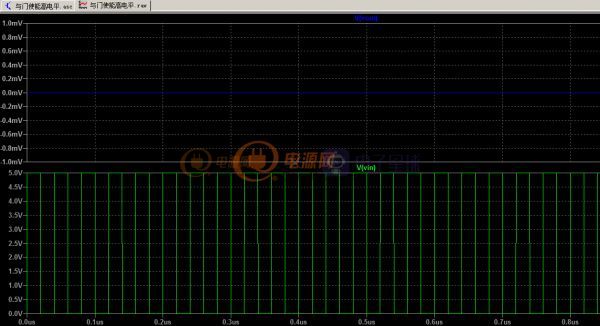

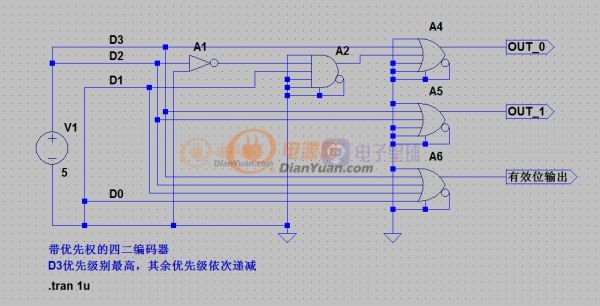

先说与门,之前帖子中提到与门有一项比较重要的作用就是作为使能端口的应用。其实原理很简单,最直观的方法是观察与门的真值表便可一目了然。

与门相当于乘法运算,有零即为零,全一才初一。作为双输入与门,如果其中一个门作为使能端,一直处于低电平状态,另一个输入端口不管是何种状态,输出固定为零。当使能端口置一,另一输入端口则可以将数据输送至输出端口。

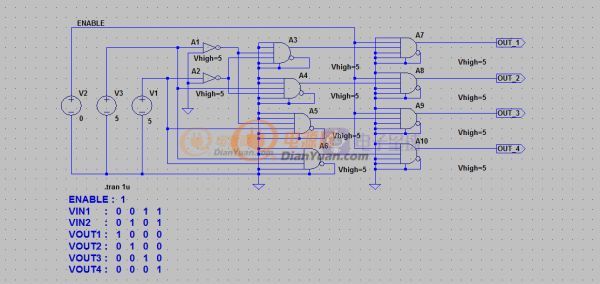

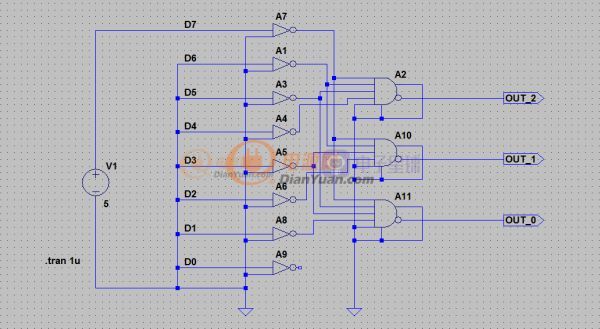

继续更新,上一帖讲解了译码器,接着就得讲讲编码器了。

编码器的原理相当于是译码器的逆过程,也就是将2^n的位码转换为n位的输出码。在信息的传输过程中,经常涉及到编码的过程。虽然原理很简单,但是真正应用都得时候,这是一门非常大的学问。比如在编码的过程中实现加密,信息传输过程中为防止掉包现象,需要加入校验位等等操作,那是相当的繁琐。

我在这里仅仅讲一点基本的编码器的逻辑实现方式,方便大家理解CPU的编码原理,先给大家来个简单的编码器,四二编码器:

今天抽时间讲讲多路复用器的工作原理吧。在CPU中,有三大总线,分别是数据总线,控制总线,地址总线。由于CPU内部的控制部件很多,涉及到的数据的传输也非常复杂,为了节省资源,不可能每个功能模块都配相应的传输线路,怎么解决这个问题呢。两种思路,第一就是通过三态门将不同的工作模块与总线相连。哪个模块需要传输数据时,就相应的将这一模块通过三态门连接到传输总线上。第二种方法就是多路复用技术,通过控制多路复用器的连接端口,在不同的时刻允许对应的端口与传输总线连接,实现数据的传输。

三态门和多路复用器的区别是,三态门的传输方式可以实现数据的输入和输出,也即是双向传输,而多路复用器一般只可以用于单向的数据输出。