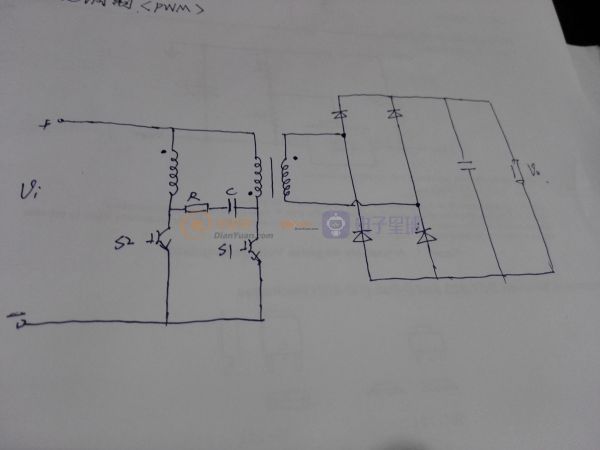

见到这样一个电路,求助一下大家,请问原边两个绕组之间的RC电路是用来干什么,谢谢!

推挽变换器

全部回复(14)

正序查看

倒序查看

现在还没有回复呢,说说你的想法

@east何文君

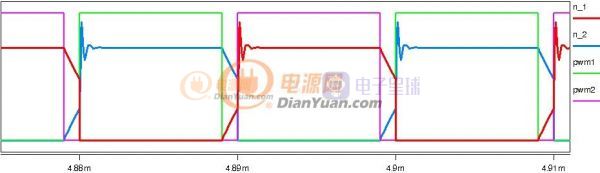

变压器初级两线圈是使用双线并绕的绕线方式,测试漏感值为3uH,MOS管两端是加有RC吸收电路的。我使用理想变压器模型分析发现是没有办法出现上述波形,所以可能是你说的是变压器漏感引起了上述波形,但是你能不能仔细分析一下这个过程。另外再附上减小占空比的测试波形以供分析。CH1:S1的Vds CH2:S2的Vge CH3:S2的Vds CH4:S1的Vge[图片]

理想变压器的电感量是无穷大的,仿真时要在理想变压器旁并联一个电感(励磁电感)来接近真实变压器。死区内的波形谐振频率比较低经分析应当是励磁电感和MOS管的寄生电容发生了谐振。

我用的参数,开关频率50Khz,励磁电感10mH,寄生电容300pF,你可以试一下。

0

回复

提示