FPGA技术目前已经被广泛的应用在模拟信号以及数字信号的采样系统设计中。在昨天的方案分享中,本文就为大家分享了一种基于FPGA技术的模拟信号采样系统设计方案,并针对这一方案的电源硬件设计进行了详细总结。在今天的分享中,本文将就这一方案中的软件设计和源程序设计进行详细介绍,下面就让我们一起来看看吧。

ADCINT设计

在本文所设计的这一基于FPGA技术的模拟信号采样系统方案中,本文所设计的ADCINT是控制0809的采样状态机。由ADC0809驱动程序生成的原理图如下图图1所示:

为了达到相应的程序控制要求,本文所设计的ADCINT的VHDL源程序如下图图2所示:

CNT10B设计

在很多利用FPGA技术所设计的信息采集系统中,都会设置有CNT10B,这直接关系到采样的精确程度。在本方案中,同样设置有一个用于RAM的9位地址计数器,它的工作时钟CLK0由WREN控制:当WREN=‘1’时,CLK0=LOCK0,LOCK0来自于ADC0809采样控制器,这时处于采样允许阶段,RAM的地址锁存时钟inclock=CLKOUT=LOCK0。这样每当一个LOCK0的脉冲通过ADC0809时采到一个数据,并将它存入RAM中。当WREN=‘0’时,采样禁止,允许读出RAM中的数据。把示波器接到DAC0832的输出端就能看到波形。CNT10B原理图如下图图3所示:

在本方案中,本文所设计的CNT10B的VHDL源程序如下图图4所示:

RAM8设计

在这一基于FPGA技术所设计的模拟信号采样系统中,为了达到设计要求,本方案所选用的RAM8是LAM_RAM,它有8位数据线和9位地址线。WREN是写时能,高电平有效。这一RAM8原理图如下图图5所示:

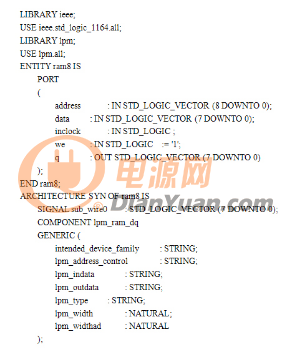

本方案中,为了达到高精度的信号采集设计要求,我们所设计的RAM8的VHDL源程序如下图图6所示:

(a)

(b)

图6 RAM8的源程序

系统顶层设计

在本方案中,我们所设计的这一模拟信号采集系统顶层原理框图如图7所示,图中D为8位数据输入,CLK为系统时钟输入信号频率,由系统时钟信号输入电路控制。Q为RAM8的8位输出,与DAC0832相接。

以上就是本文针对一种基于FPGA技术所设计的模拟信号采集系统的软件设计部分,所进行的方案分享,希望能够对各位工程师的设计工作提供一定的帮助。

声明:本内容为作者独立观点,不代表电源网。本网站原创内容,如需转载,请注明出处;本网站转载的内容(文章、图片、视频)等资料版权归原作者所有。如我们采用了您不宜公开的文章或图片,未能及时和您确认,避免给双方造成不必要的经济损失,请电邮联系我们,以便迅速采取适当处理措施;欢迎投稿,邮箱∶editor@netbroad.com。

| 微信关注 | ||

|

| 技术专题 | 更多>> | |

|

| 研发工程师的工具箱 |

|

| 智慧生活 创新未来 |