FPGA的出现解决了长久以来定制电路的不足,于此同时,还可服了原有可编程器件门电路数量不足的缺点。在FPGA中触发器是较为基础也是较为关键的部分,从基础的RS触发器中,延伸出很多不同分类不同功能的触发器,在本文中,小编将为大家介绍关于FPGA中RS触发器的难点理解。

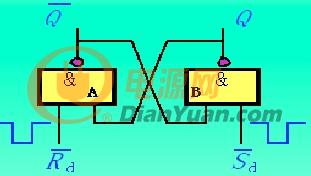

图1

图1是基本RS触发器原理图,具体工作原理网上有不少资料,这里就不进行仔细的讲解,下面就对一些新手在进行学习过程中遇到的与RS触发器有关的难点进行讲解。

关于负脉冲和低电平

所谓负脉冲,就是一个信号从高电平置为低电平,然后延迟一段时间后再置为高电平的过程,就像图1所示的脉冲。而低电平就没有返回高电平的过程。

关于Q端

无论是置“1”端还是置“0”端,操作的都是Q端,间接操作Q非端,刚开始经常会错误的以为Sd非端控制相应上面的端口。但实际上,Rd非端和Sd非端都是控制Q端,即Sd非端一个负脉冲,Q端置“1”,Q端如果原状态就是“1”,则加一个负脉冲后原状态不改变。Rd非端一个负脉冲,Q端置“0”,Q端如果原状态就是“1”,则加一个负脉冲后原状态不改变。

两个端口都加负脉冲的情况

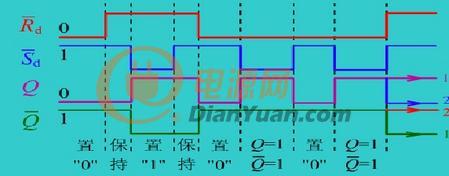

正常来说,两个端口是不允许同时加负脉冲的,因为一旦两端同时加负脉冲,则两个输出端就都为“1”,这样与我们认为的两个输出端的值互为反变量的原则就相违背了,但是在画时序图的时候,可以将两个输出端同画为高电平。重点是,当两个输入端都为低电平的时候,再把它们扳回高电平,这时候输出端就会有两种结果,而具体是哪种结果,这要取决于两个门电路的运转速度问题了,图2为时序图。

图2

图3基本RS触发器的真值表

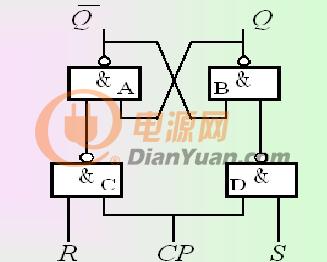

图4同步RS触发器

同步RS触发器是在基本RS触发器的基础上加了两个与非门,CP是时钟。当CP为“0”时,下面两个门电路相当于被封死,这时第一级门电路的输出端就都为“1”,即保持状态。当CP为“1”时,门电路被打开,第一级门电路的输出端分别为Rd非和Sd非,与刚才的基本RS触发器相同。

本文针对新手,重点介绍FPGA学习过程中遇到的RS触发器相关基础难点问题,并通过经验总结,对这些容易引起新手疑问的问题进行了解答。对于新手来说,可以算的上是一篇较为实用的参考文章,希望大家在阅读过本文之后能够有所收获。

声明:本内容为作者独立观点,不代表电源网。本网站原创内容,如需转载,请注明出处;本网站转载的内容(文章、图片、视频)等资料版权归原作者所有。如我们采用了您不宜公开的文章或图片,未能及时和您确认,避免给双方造成不必要的经济损失,请电邮联系我们,以便迅速采取适当处理措施;欢迎投稿,邮箱∶editor@netbroad.com。