| |||||||

1、引言

在工业加热中,感应加热方式越来越受到人们的重视,其特点是以电为能源,通过电磁感应的原理对金属工件进行熔化、透热、表面淬火加热,感应加热环保、节能、自动化程度高。工业感应加热装置主要由变频电源和感应炉组成。变频电源的作用是依靠电力电子功率器件,对50Hz的电网工频电源进行整流、滤波、然后再逆变为需要的频率。变频电源也叫感应加热电源,输出端负载接并联、串联、或串并联谐振电路。逆变输出频率工作在槽路谐振电路的固有频率f0 附近,是负载电路有一个高的效率和较好的功率因数。但是,金属在加热过程中,由冷态到热态电阻是变化的,磁性金属材料过了居里点后,失去磁性,谐振等效参数变化较大,为了能使逆变输出保持和槽路的谐振频率变化一致,必须在感应加热变频电源的逆变控制电路设计有频率跟踪电路,由于各种跟踪方法的不同,形成了逆变跟踪控制技术。

2、模拟锁相环技术

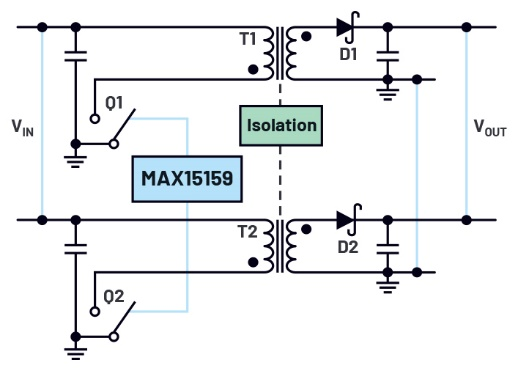

锁相环技术最早应用于广播和通讯方面的电路,现在在感应加热电源上应用比较普遍。锁相环简称PLL。其主要有三个基本单元构成,即鉴相器PD、压控震荡器VCO和低通滤波器LPF。PLL的基本结构见图1所示。

图1 压控振荡器结构框图示意

PLL的工作原理:输入电压ui与输出电压uo通过鉴相器对两个相位进行比较。形成相位误差电压uo',这个误差电压再经过低通滤波后得到控制电压Ud,控制电压的大小决定了压振振荡器产生的频率高低的偏移大小,这个新的频率偏移信号再次和输入信号ui进入鉴相器比较,形成新的误差电压uo'及滤波后Ud控制电压,直到进入鉴相器的两个信号相同,输出误差电压uo=0,控制电压Ud=0,从而实现了输入信号频率和输出信号频率相同,锁相环实现了锁定,这实质就是频率跟踪过程。

能够实现锁相环功能的集成电路很多,下面仅以国内常用的集成锁相环芯片CD4046为例分析频率跟踪电路技术。4046芯片内集成有2个鉴相器,即PD1和PD2,压控振荡器,外接低通滤波器。按一定的电路接法能组成一个锁相环电路,对负载电流进行频率跟踪。见图2所示。

图2 CD4046组成的锁相环频率跟踪电路

感应加热电源输出到负载电流的为io,经过LEM传感器采样后,送入到过零比较器LM339,变成方波信号,送入到CD4046的14脚,内部接PD2的输入端,PD2的输出端13脚外接R3、R4、C2构成低通滤波器,滤波后的信号输入到9脚,9脚内部接的是压控振荡器的输入端,压控振荡器的输出端为3脚,由3脚输出的信号分为两路,一路接3脚,3脚内是PD2鉴相器输入,另一路去驱动逆变器的功率开关器件,这路是负载电压信号。当负载电流与负载电压信号相位差为零时,锁相环进入锁定状态,频率跟踪实现。PD2由逻辑门控制的四个边沿触发器和三态输出电路组成,为0o相移,并与脉冲的占空比无关,常选用鉴相器PD2来实现无相差的频率跟踪。

电源工作中,负载的等效参数发生变化而引起固有频率f0变化时,由于锁相环有一定范围频率的锁相宽度,这个宽度覆盖了f0的变化范围,锁相环一般不会失锁,所以频率始终是能够跟踪的。

无论负载是串联谐振还是并联谐振电路,开始工作时,槽路都有一个起动过程。串联谐振感应加热电源一般设有它激到自激的起动的电路。图2中起动过程是这样的,电路开始起动的瞬间,Cs可视为短路,端9脚加电源电压,压控震荡器VCO输出最高频率;伴随着Cs的逐步充电,9脚的电压逐步降低,VCO的输出频率也由最高向最低频率变化,若槽路的固有谐振频率f0 在最高和最低频率间,则会激发负载频率振荡,而这个振荡的频率一但被传感器采样后,进入鉴相器被俘获,负载的频率会被锁相环跟踪,这时槽路谐振起动完成。VD1是把起动电路和滤波电路隔离。

并联谐振电路起动难于串联谐振起动。目前流行着一种扫频起动方式,这种方式是在4046的9脚前加上一个电压由高到低的变化,当到达地电位时,再一次由高到低电压变化,加到9脚上,接4046内部的VC0,从而使输出端频率由高到低一遍一遍扫描,直到并联负载电路起动才停止。见图3所示电路。

图3 并联谐振扫频起动和锁相环电路

工作原理:IC19C和外围元件组成了积分电路,当电源接通时,W6的活动端会有一个分压,相当于在积分电路的输入端加入了一个电压阶跃信号,使IC19C的输出电压按照积分规律变化。这个信号通过VD68正极大于负极电压时输出一个脉冲,宽度由积分时间常数决定。扫描电路由IC19B和其外围元件组成,这个扫描发生器工作过程具有PI(比例积分)的输出特性,电路在得到VD68的正脉冲信号后,IC19B输出端会产生一个先高后低按积分规律变化的电压,加到CD4046的9脚,C53是充电电容,电压充电后下降速度比较缓慢且线性度较好,下降电压持续时间到输入高电平脉冲下跳沿结束。同时,由于输入信号反极性变化,IC19B的输出端电压极性也会出现反转升高,导致运放IC19C同相输入端电位上升,结束一次扫描。由于加到CD4046的9脚电压是由高到低线性变化的,所以CD4046的4脚将会输出一个由高到低变化的频率信号。

CD4046和外围电路组成了锁相环电路,模拟开关IC21A、IC21B、IC21D、可以切换元件和电位。中频变压器T7及相关元件组成了谐振槽路信号的反馈通道,由14脚进入CD4046内部,当扫描电路产生的由高到低的线性变化电压由CD4046的9脚输入后,其4脚输出一个由高到低的频率变化脉冲信号,经逆变驱动电路加到逆变晶闸管上使逆变桥上的晶闸管有序开通关断,并输出到谐振槽路,使谐振槽路上LC逐步的由静止状态谐振起来,再将这个信号通过中频电压互感器取样,通过T6隔离,变压器之后的交流信号通道加到CD4046的14脚,锁相环把扫描信号和反馈回的中频电压信号进行比较,进行锁定。一但锁相,自动起动检测电路会让扫描电路停止继续扫描,中频电压信号会进入自动跟踪的正常工作过程。

起动检测部分包括起动成功检测电路和起动失败检测电路。起动成功检测电路有IC19A、R121、R117、R116及起动指示Dpp等元件组成。当频率锁定成功后,模拟开关IC21A、IC21B导通和IC21D截止。IC19A反相输入端电位降低,输出电位升高,二级管Dpp(起动成功的指示)由发光到停止发光,并从R117、R116的分压点输出约为2/3Vcc的高电平,该高电位作为允许给定功率调节的控制信号。起动失败检测电路由IC19D、R124、R115及电源指示发光二极管Dpw等元件组成。IC19D的同相输入端约有1.5V左右的参考电位。当扫描锁相失败(扫描频率发生后,无法从主回路得到反馈回来的中频信号,或这个信号不被扫描信号所覆盖)时,IC19D的反相输入端的电位将会降止低于同相输入端的电位,此时IC19D输出变高,得出起动失败信号,该信号通过IC9A的控制来禁止给定功率调节的控制信号输入。在扫描电路的控制下,若一次起动不成功,则锁相环的扫描电路会进行自动重复起动,由高向低不断进行,重复周期大约为0.5秒左右,直到起动成功或人工干遇停止。自动重复起动电路这里未画出。

CD4046芯片实现锁相环技术虽然较早,但缺点是:存在跟踪范围窄,频段不同,要求滤波网络参数不同,在串联的线路中实现死区时间还要另加辅助电路,该锁相环涉及元件多,线路复杂参数易零漂,故障率相对多,正逐步被数字锁相环技术所取代。

3、数字锁相环技术

可以用单片机、微处理器(DSP)、FPGA或CPLD可编程芯片来实现中频电源的数字锁相环频率跟踪的目的。这里分别简要进行论述。

图4 8051单片机组成的锁相环电路

图4是用通用单片机8051实现锁相环频率跟踪的硬件电路图。用电流传感器采样到负载电流后,用比较器将正弦波变换成方波信号,加到单片机的外中断口INT0,单片机得知中断信号到来后,起动计数器T0开始计数,之后不断循环检测外中断口,直到中断信号消失,计数器T0停止计数。具体为,负载电流正半周向负载半周过零信号到达时,中断信号消失,T0停止计数。这个计数值乘以2得到负载的谐振周期。以谐振周期为定时器1的时间常数,发出第一路(OUT1)驱动脉冲,延时经过设定的死区时间后发生第二路(OUT2)驱动脉冲。忽略信号延迟时间,可以得到两路同频的驱动脉冲及同步的中断信号。即负载电压信号和负载电流信号同频,从而实现了感应加热电源工作在谐振的f0或f0附近。

通用单片机能实现频率带较大范围的跟踪,且运行稳定、可靠,但控制精度和速度略差,不尽人意。

DSP可以克服8051单片机的缺点,主频快,运算速度高,计算能力强。图5是用DSP实现的数字频率跟踪锁相环电路图。DSP选用TI生产TMS320F240芯片。

图5 DSP组成的锁相环频率跟踪电路

图中的工作原理:i为串联谐振加热电源负载上的电流取样信号,经过信号整理转换为方波后输入到TMS320F240的CAP3(高速捕获单元),获得输入脉冲的时间,得到脉冲周期,CAP3产生中断。DSP程序进行数字锁相环的运算,以过零点为参照,分别输出两路驱动脉冲,实现频率跟踪。TMS320F240可以提供PWM输出波形,也可以直接产生两路脉冲波形,死区时间可调,经隔离、驱动电路去驱动逆变桥的功率开关器件。DSP实现的锁相环频率跟踪电路元件少,抗干扰能力强。

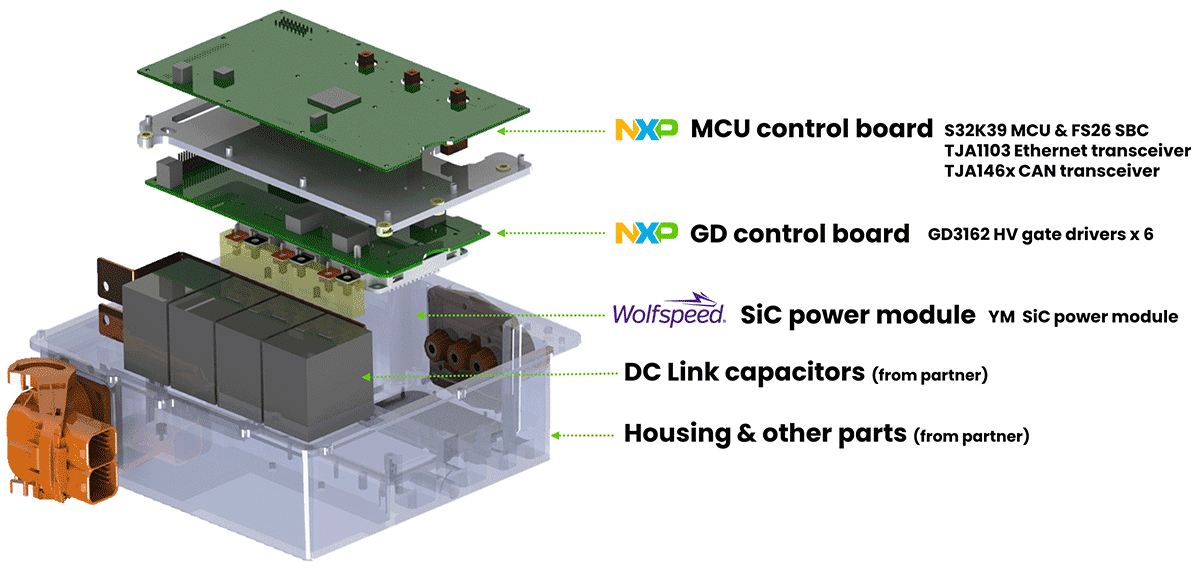

现代EAD技术中,现场可编程门陈列(FPGA)与复杂的可编程逻辑器件(CPLD)是一种可重构器件,选定芯片后,可以根据电路功能的需要,用VHDL等硬件设计语言编程得到逻辑功能关系,下载传输到芯片中,实现专用电路功能。如果软件设计有缺陷或要进行升级,不动硬件,直接再次下载新的程序到芯片中,就完成了升级更新。这些芯片典型的有Altera公司、Xilinx公司生产,分多个类型系列。感应加热电源中可用FPGA或CPLD芯片实现全数字锁相环(DPLL),即采用数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO),结构示意图见图6。

图6 FPGA/CPLD组成的频率跟踪电路示意图

工作原理:由电流传感器采得电源负载的电流信号Fi,作为反馈的频率跟踪输入信号,通过鉴相器输到K计数器,同时还有N分频器的输出驱动脉冲信号一方面去输出驱动信号Four,另一路进入鉴相器和Fi 信号进行比较,若Fi信号超前Four信号,K计数器输出脉冲至I/D线路的增量输入,I/D线路输出增加一定插入脉冲,经N次分频后,是Four脉冲信号频率上升相位差不断变缩小,直至差值为零,即进入数字锁相状态。若输入的信号Fi滞后反馈信号Four,K计数器输出借位脉冲至I/D线路的减号输入,I/D线路输出减少一定的脉冲,经N次分频后,使反馈信号频率下降,相位差不断减少直到差为零。在这样的不断调节下,最后会达到感应加热电源的输出电流信号和电压信号达到一致,实现槽路谐振频率的自动跟踪。

用FPGA/CPLD来设计数字化的锁相环,灵活方便,精度高,修改易,是今后的一个重要发展方向,只是芯片目前的成本比较高,对开发人员的素质要求高一些,但可以预期,随着电子设计的进步,EDA的发展,最终将会有大量的FPGA/CPLD芯片进入数字话的感应加热电源电路中。

4、结论

现代感应加热变频电源离不开锁相环技术,特别是数字锁相环技术,它能达到逆变频率的自动跟踪。而锁相环技术的实现方法有多种,各有其特点。纵观这项技术的发展,DSP和FPGA/CPLD这两种物理芯片实现频率的自动跟踪将有更广阔的发展前景。

声明:本内容为作者独立观点,不代表电源网。本网站原创内容,如需转载,请注明出处;本网站转载的内容(文章、图片、视频)等资料版权归原作者所有。如我们采用了您不宜公开的文章或图片,未能及时和您确认,避免给双方造成不必要的经济损失,请电邮联系我们,以便迅速采取适当处理措施;欢迎投稿,邮箱∶editor@netbroad.com。