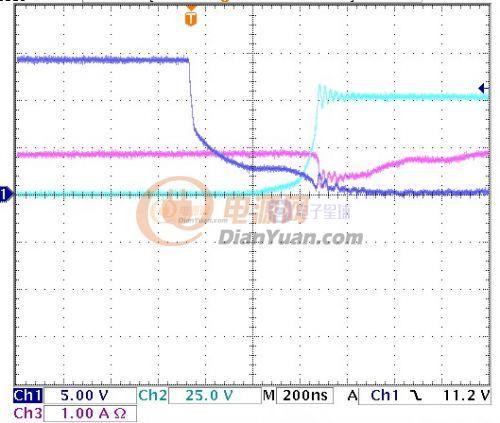

BUCK电路,目前还是初步调试阶段,MOSFET关断时的Vgs,Vds,Id分别如下图中的CH1,CH2,CH3所示。从波形上看,似乎是MOSFET在应该关断的时候误导通了,所以电流又从0开始上升,后面部分Vds有一个电压跌落,Id看上去就是正弦振荡。。。图没有截好,这一部分看不到。之后,Vds和Vgs又恢复正常。求教一下各位大侠,这会是什么原因造成的呢?谢谢!

【图】请高手帮忙看一下这个BUCK关断时的波形

全部回复(7)

正序查看

倒序查看

现在还没有回复呢,说说你的想法