《CMOS技术中的闩锁效应——问题及其解决方法》

目录

1.引言

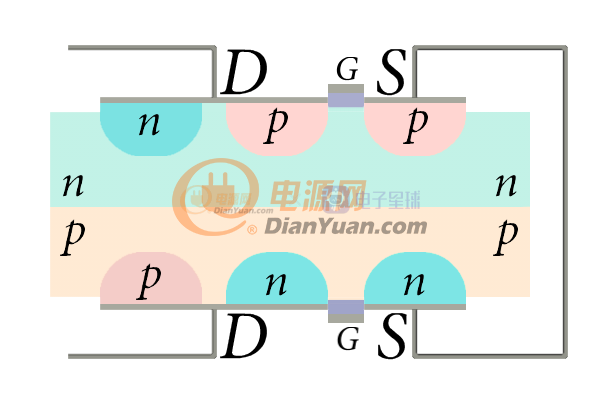

2.闩锁的概述

2.1 结构上的起因和集总元件模型

2.2 举例。悬空N阱结构中的闩锁问题

3.闩锁问题的描述

3.1 阻塞态和闩锁态

3.2 闩锁产生的必要条件

3.3 触发方式

3.4 触发方式分类

4.闩锁模型及分析

4.1 早期的闩锁模型

4.2 PNPN集总元件模型的发展

4.3 闩锁的物理分析

4.4 安全区-阻塞态的严格定义

4.5 饱和区模型

4.6 闩锁的图解说明

4.7 集总元件模型的修正

4.8 动态闩锁效应

5.闩锁特性的测量

5.1 测量仪器

5.2 两端特性的测量

5.3 三端和四端特性的测量

5.4 开关转换点特性的测量

5.5 保持点特性的测量

5.6 动态触发

5.7 温度关系

5.8 非电探针测量

5.9 闩锁特性测量总结

6.闩锁的防止

6.1 版图设计布局规则

6.2 破坏双极特性的工艺技术

6.3 双极去耦工艺技术

6.4 CMOS的设计考虑

6.5 无闩锁的设计

7.总结

- 回复

- 收藏

- 点赞

- 分享

- 发新帖

- 论坛首页

- LED照明 中国好方案

- 《CMOS技术中的闩锁效应——问题及其解决方法》

立

即

发

帖