四个MOS管的DS极需要外接二极管吗?我查看一些芯片规格书,有的接,有的不接,有些疑惑

四个MOS管的DS极需要外接二极管吗?我查看一些芯片规格书,有的接,有的不接,有些疑惑

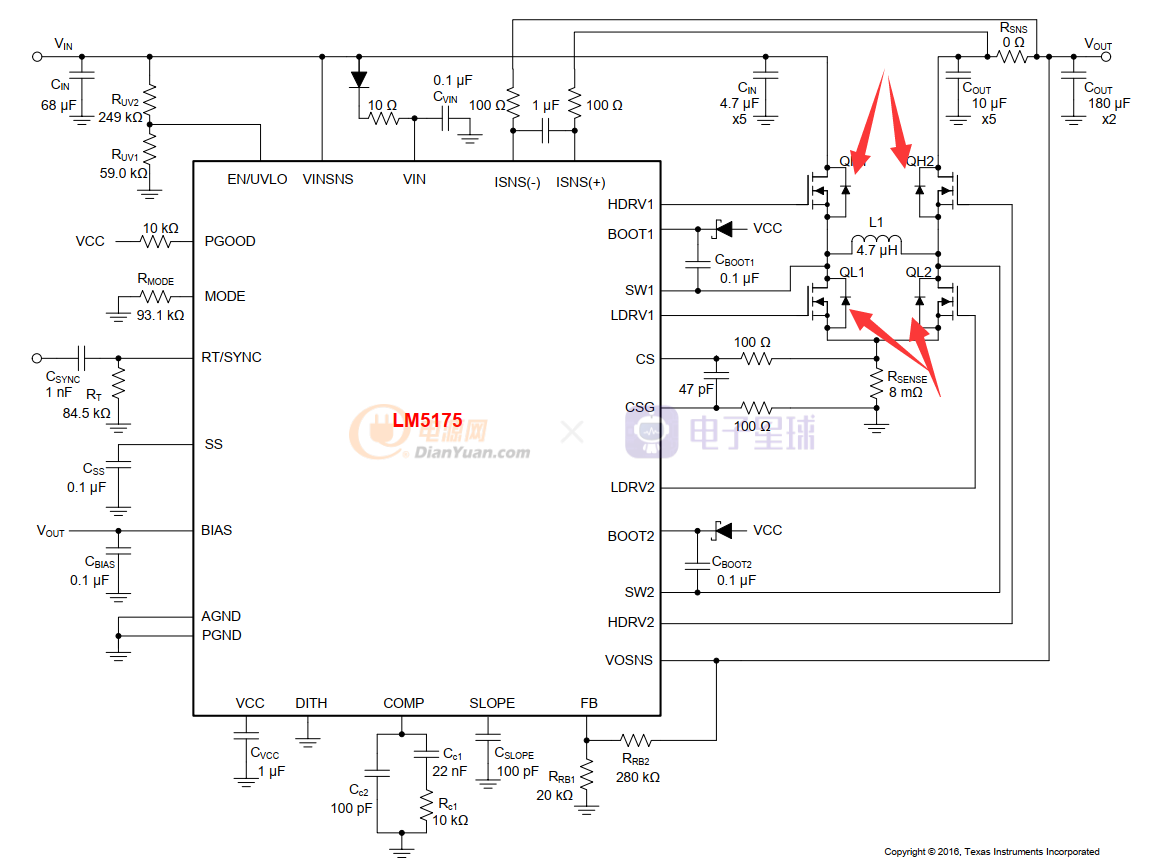

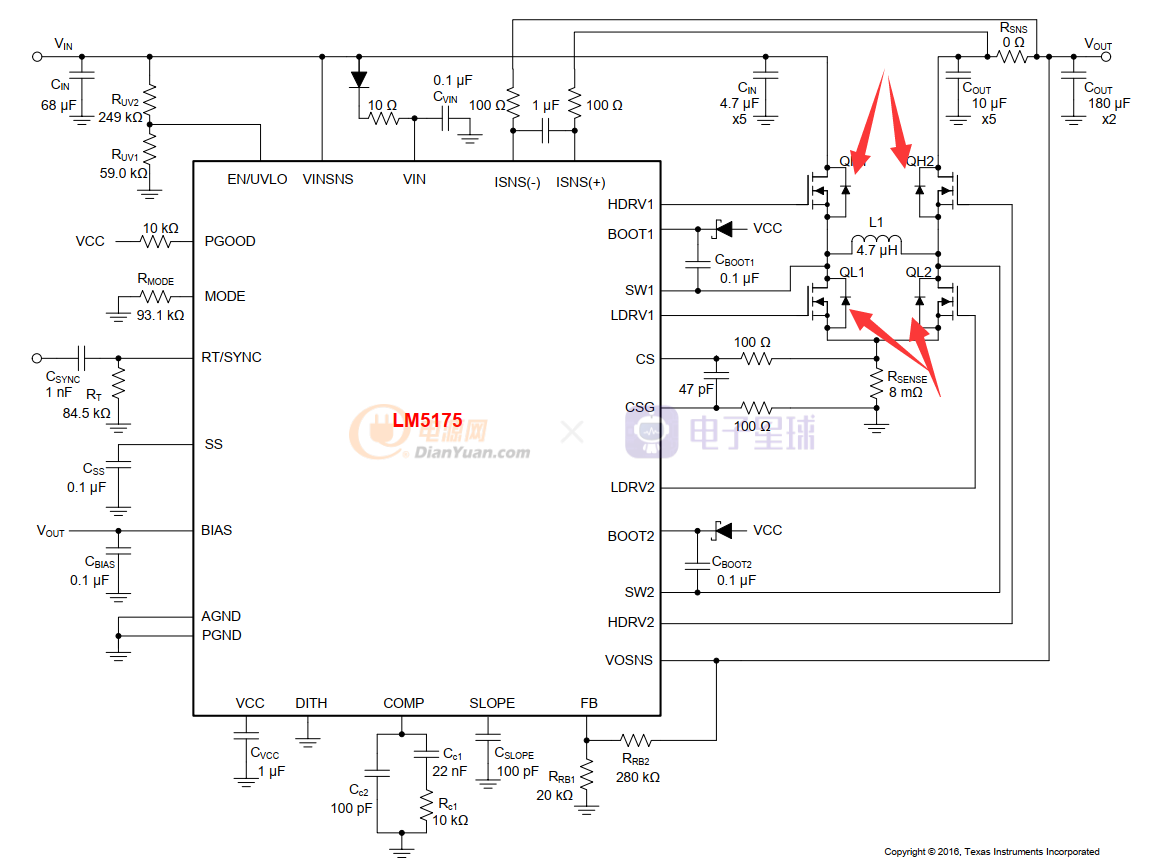

第一张图:是MOS寄生的二极管,具体是肖特基还是快恢复,要看芯片的制程,按照是否设计了barrier和金属制程产生硅化两种方法,有肖特基和快恢复两种管子,但是现在一般芯片制造主要使用Ti金属,(现在一般的MOS生产过程中都是使用钛Ti),那么这个管子就是钛制程的肖特基二极管,但是这个二极管是寄生的所以没有Barrier,高温情况下耐压VB会下降,这也是Ti制程的缺点,所以钛制程的肖特基,SBD,MOS都有同一个缺点,就是Vbarrier(肖特基参数名称VR/MOS参数名称VDS)的耐压能力会下降;

第二张图:是MOS旁边并联的肖特基,大家在看国外品牌半导体的规格书时,MOS一般都会外接一个二极管,一般都是用肖特基二极管并联,并联的原因是保护作用,这也是肖特基最大的市场,国内一般都省去了,因为主要起保护作用,所以省去出问题的概率可能只有万分之几,另一个作用是外接肖特基与MOS内部的二极管并联,还起到分流和分散散热的作用 ;利用肖特基并联MOS因为MOS的生产制程主要是外延片而没有做barrier,所以MOS的VDS耐压高温情况下会降低,但是肖特基一般是做了barrier这样高温下耐压更稳定可靠,所以肖特基并联就是为了保护MOS的耐压下降得太多而损坏,当然现在肖特基也有不少不再使用Barrier制程,所以加了也起不到保护作用了,只有高Barrier铂金制程的,而且要特定做高Barrier,这个肖特基的特征就是IR反向漏电比较低,特别是高温下的漏电比较低,一般60V的肖特基反向漏电在125℃下漏电<3mA,这个制造是很难的,需要高Barrier和生产上花费双倍的生产时间,才能达到在高温是也能保持VB不降低

所以为了稳定可靠,就在MOS旁并联肖特基,选择肖特基要关注

1.肖特基的制程(高Barrier还是低Barrier,实际使用下的温度,是否有风冷散热);

2.应用电流下VF和IR,具体电流下的VF

如果你实在在乎成本,那5A以内MOS基本可以不用并联肖特基,5A以上看情况,不过国内设计东西大部分不知道具体原因,有些 设计看着感觉没用,就省去了,我看到华为在设计的时候都是有预留,但是生产时很多都省去了

MOTIVE 墨濎半导体,专业TMBS制造商 提供超大电流的肖特基二极管

TOLL封装,TO-247封装的超大电流肖特基

学习了,谢谢