引言

对于MOSFET,米勒效应(Miller Effect)指其输入输出之间的分布电容(栅漏电容)在反相放大作用下,使得等效输入电容值放大的效应。由于米勒效应,MOSFET栅极驱动过程中,会形成平台电压,引起开关时间变长,开关损耗增加,给MOS管的正常工作带来非常不利的影响。

本文详细分析了MOS管开通关断过程,以及米勒平台的形成。然后结合实际应用电路中说明了MOSFET开关中电压尖峰的形成原因和可能带来的后果,并给出了相应的解决方案。

MOSFET结构及寄生电容的分布

MOSFET结构

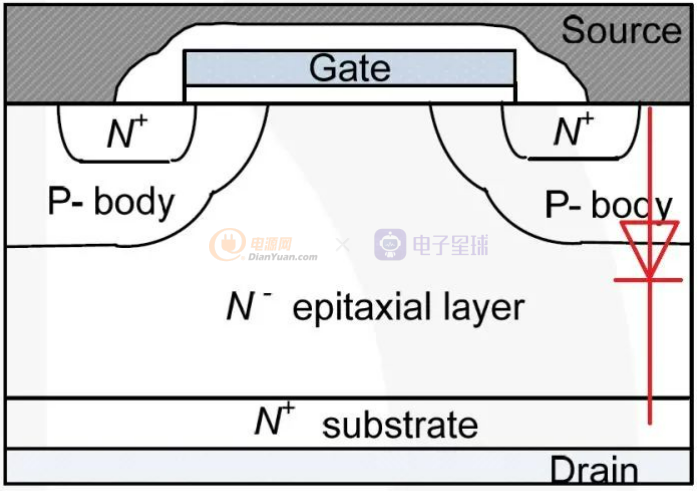

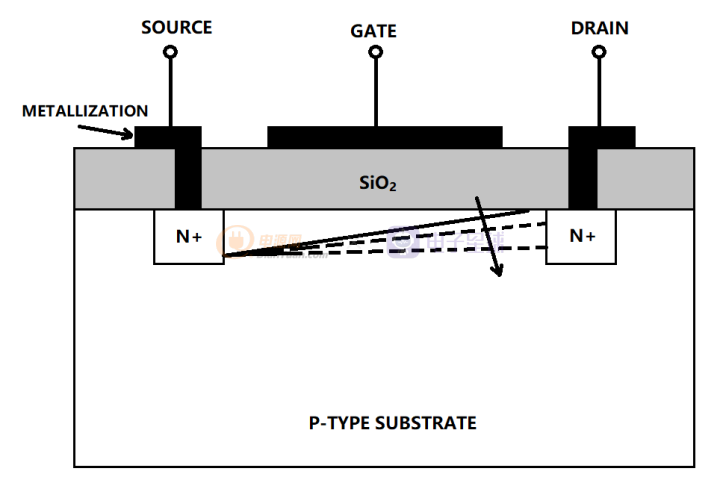

图1. 垂直型MOSFET结构

图1是垂直型MOSFET的结构,它是一个由P区域和 N+ 的源区组成的双扩散结构。漏极(drain)和源极(source)分别放在晶圆的两面,这样的结构适合制造大功率器件。因为可以通过增加外延层(epitaxial layer)的长度,来增加漏源极之间的电流等级,提高器件的击穿电压能力。另外从图中,还可以清晰看出MOSFET的寄生体二极管。

寄生电容

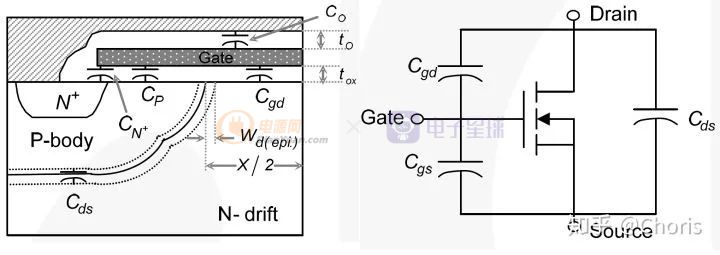

图2. MOSFET的寄生电容及等效电路

MOSFET的寄生电容主要包括栅源电容(Cgs)、栅漏电容(Cgd)以及漏源电容(Cds)。从图2中左图看到,Cds是由漏极和源极之间的结电容形成,Cgd栅极和漏极间的耦合电容。Cgs则较为复杂,由栅极和源极金属电极之间的电容Co、栅极和 N+ 源极扩散区的电容 CN+ ,以及栅极和扩散区P区的电容Cp组成。

一般器件的手册中,都会以下列形式给出MOSFET的寄生电容,

输入电容:

输出电容:

反向传输电容:

米勒平台的形成

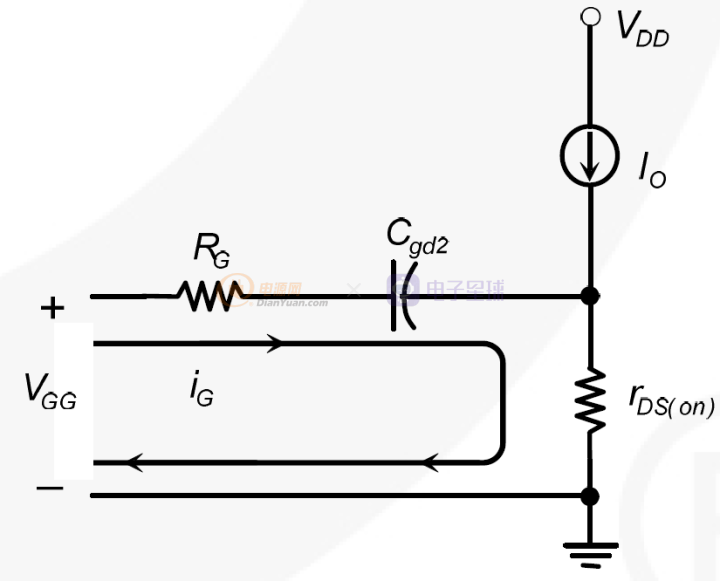

考虑到电感负载的广泛应用,本文以电感负载来分析米勒平台的形成。由于MOS管开关的时间极短,电感电流可以认为不变,当作恒流源来处理。图3是栅极驱动电路以及开通时MOS管的电流电压波形。

图3. 栅极驱动电路及其波形

MOS管的开通过程可以分为三个阶段。

t0-t1 阶段

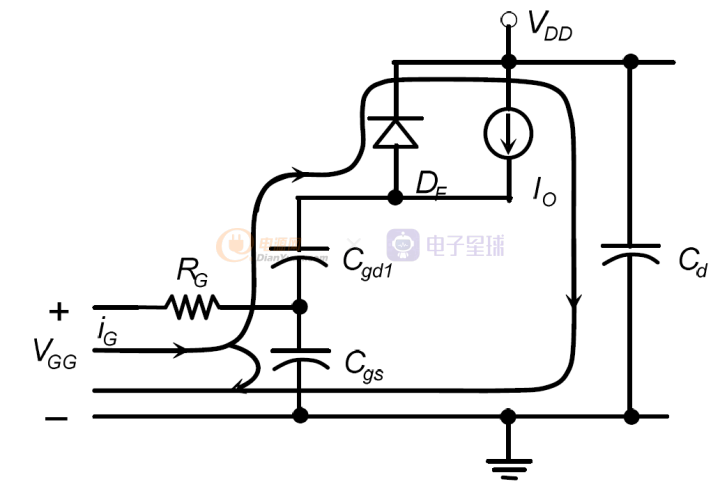

图4. t0-t1时的等效电路

从 t0 时刻开始,栅极驱动电流给栅源电容Cgs充电。Vgs从0V上升到Vgs(th)时,MOS管处于截止状态,Vds保持不变,Id为零。

t1-t2 阶段

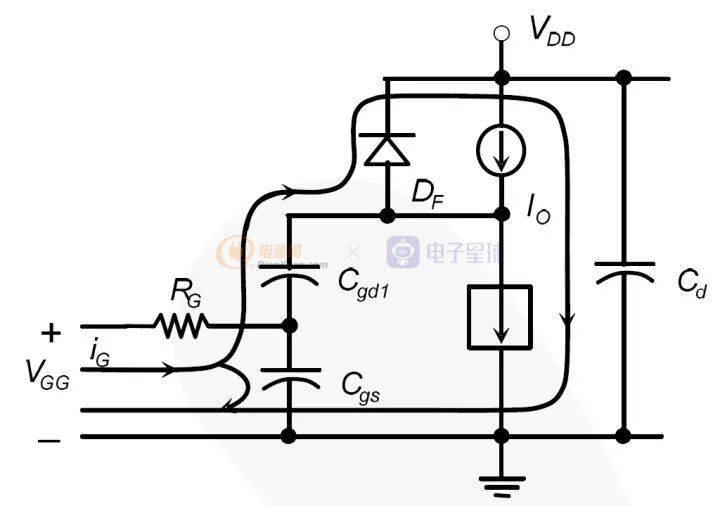

图5. t1-t2时的等效电路

从t1时刻开始,MOS管因为Vgs超过其阈值电压而开始导通。Id开始上升,电感电流流经续流二极管DF的电流一部分换向流入MOS管。但是此时二极管仍然导通,MOS两端的电压仍然被二极管钳位保持不变。驱动电流只给栅源电容Cgs充电。到t2时刻,Id上升到和电感电流一样,换流结束。

在t1-t2这段时间内,电感电流上升过程中Vds会稍微下降。这是因为Id上升的di/dt会在引线电感等杂散电感上形成压降,所以MOS管两端的电压会稍稍下降。

这段时间内,MOS管处于饱和区。

t2-t3 阶段

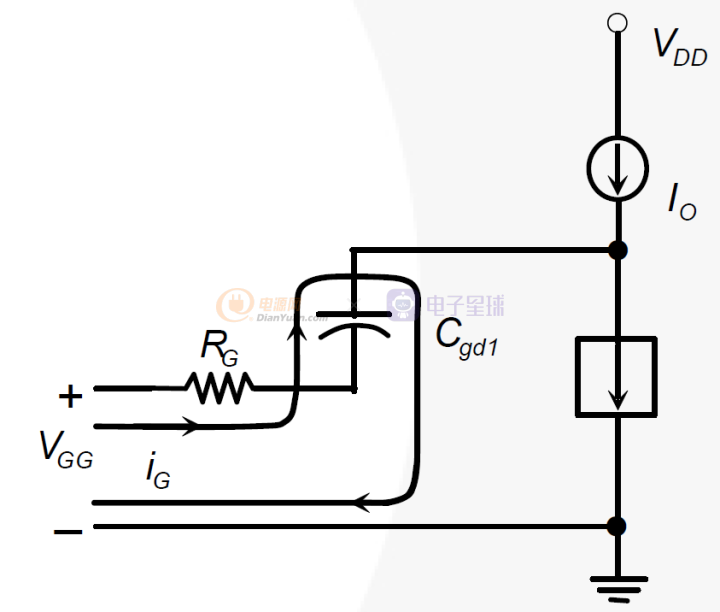

图6. t2-t3时的等效电路

从t2时刻开始,由于MOSFET中的电流已经上升达到电感负载中的电流,MOS管两端的电压不再被VDD钳位。因此,漏源之间的反型层沟道也不再被VDD束缚而呈楔形分布,Vds开始降低 ,栅极驱动电流开始给Cgd充电。驱动电流全部用来给Cgd充电,栅极电压Vgs保持不变呈现出一段平台期,这个平台称为米勒平台。

米勒平台一直维持到Vds电压降低到MOS管进入线性区。可以注意到,在米勒平台期,Vds电压下降的斜率分为两段,这与MOSFET的结构有关。在导通的不同阶段Cgd电容发生变化的缘故。

在这个阶段,MOS管仍然处于饱和区。

这里顺便说一下,为什么漏源电压在MOSFET进入米勒平台后开始下降。

在进入米勒平台前,漏源电压由于被二极管钳位保持VDD不变,MOS管的导电沟道处于夹断状态。当MOSFET的电流和电感电流相同时,MOSFET的漏极不再被钳位。这也就意味着,导电沟道由于被VDD钳位而导致的夹断状态被解除,导电沟道靠近漏极侧的沟道渐渐变宽,从而使沟道的导通电阻降低。在漏极电流Id不变的情况下,漏源电压Vds就开始下降。

当漏源电压Vds下降后,栅极驱动电流就开始给米勒电容Cgd充电。几乎所有的驱动电流都用来给Cgd充电,所以栅极电压保持不变。这个状态一直维持到,沟道刚好处于预夹断状态,MOS管进入线性电阻区。

图7. MOSFET在不同漏极电压时,导电沟道的变化情况

t3-t4 阶段

图8. t3-t4时的等效电路

从t3时刻开始,MOSFET工作在线性电阻区。栅极驱动电流同时给Cgs和Cgd充电,栅极电压又开始继续上升。由于栅极电压增加,MOSFET的导电沟道也开始变宽,导通压降会进一步降低。当Vgs增加到一定电压时,MOS管进入完全导通状态。

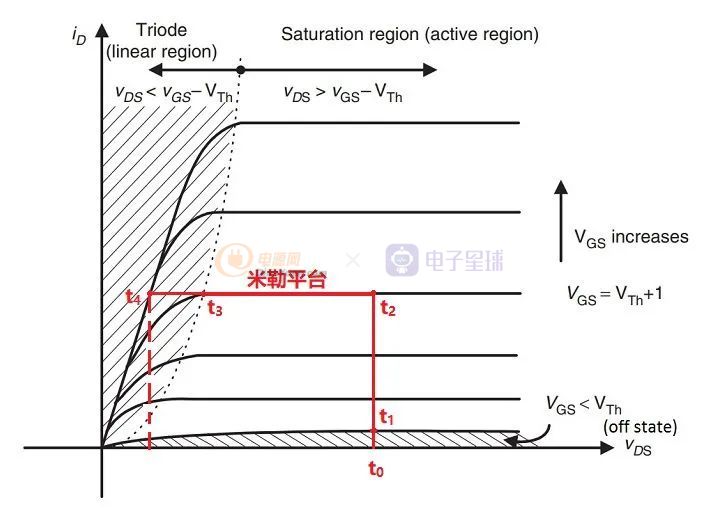

现在总结一下,在MOSFET驱动过程中,它是怎么打开的。图9标示了在开通时不同阶段对应在MOSFET输出曲线的位置。当Vgs超过其阈值电压(t1)后,Id电流随着Vgs的增加而上升。当Id上升到和电感电流值时,进入米勒平台期(t2-t3)。这个时候Vds不再被VDD钳位,MOSFET夹断区变小,直到MOSFET进入线性电阻区。进入线性电阻区(t3)后,Vgs继续上升,导电沟道也随之变宽,MOSFET导通压降进一步降低。MOSFET完全导通(t4)。

图9. MOSFET输出曲线

米勒效应对MOSFET开关过程的影响

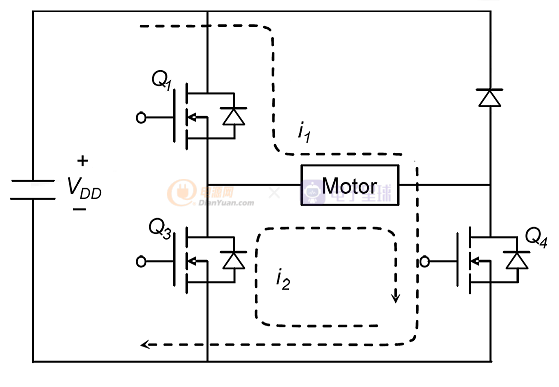

下面以图10中电机控制电路来说明米勒效应对MOSFET开通关断过程的影响。在图10控制电路中,上管导通时,VDD通过Q1、Q4对电机进行励磁;上管关断时,电机通过Q4、Q3进行去磁。在整个工作过程中,Q4一直保持开通,Q1, Q2交替开通来对电机转子进行励磁和去磁。

图10. 电机控制电路

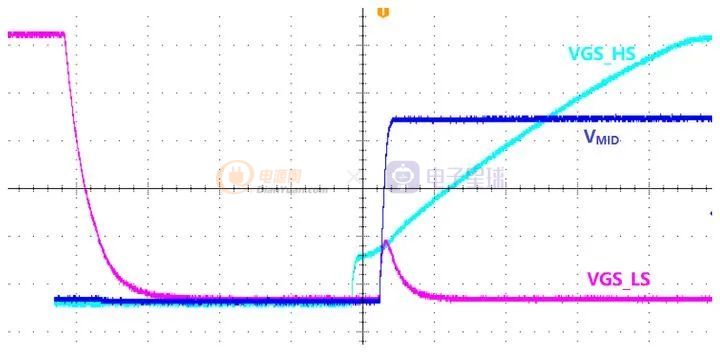

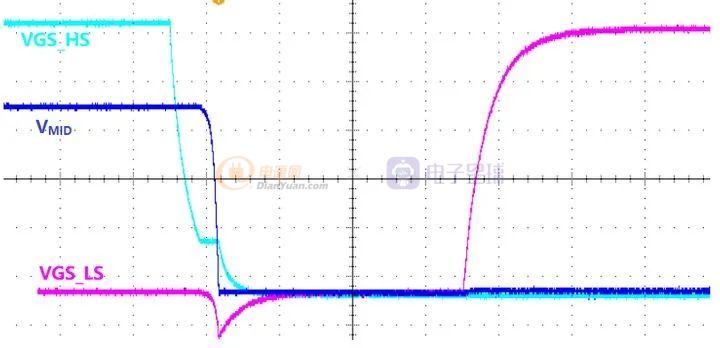

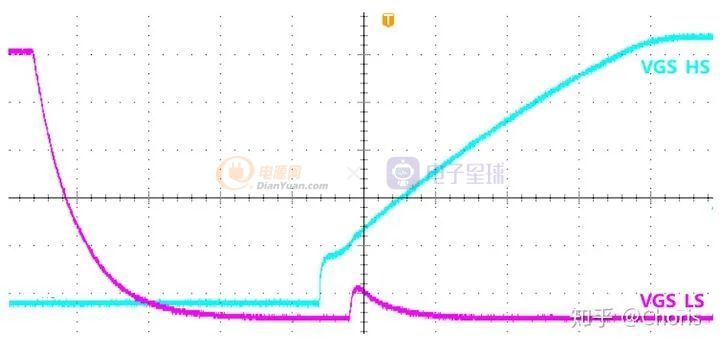

图11,图12是上下管开通关断时驱动电压测试波形。可以清楚的看到,在上管开通和关断时,下管栅极上会产生一个尖峰,尖峰的电压增加了上下管同时导通的风险,严重时会造成非常大的电流同时流过上下管,损坏器件。

图11. 上管开通下管关断时的测试波形

图12. 上管关断上管开通时的测试波形

下管开通关断出现的这种波形是由漏栅电容导致的寄生开通现象(如图13所示)。在下管关断后,上管米勒平台结束时,桥臂中点电压由0升到VDD,MOSFET的源极和漏极之间产生陡峭的的dV/dt。由此在漏栅电容产生的电流会流到栅极,经栅极电阻到地,这样就会在栅极电阻上产生的电压降。这种情况,就会可能发生上下管同时导通,损坏器件。

图13. MOSFET寄生开通机制

下管的这个Vgs尖峰电压(也有公司称之为Vgs bouncing)可以表达为:

Rgoff驱动关断电阻,Rg,ls(int)为MOSFET栅极固有电阻,Rdrv为驱动IC的电阻。从公式(1)可以看到,该电压与Rgtot和Cgd呈正向相关。

所以解决这个问题有两类方法:

1. 减小Rgtot。由公式(2)知道,Rg,ls(int)由器件本身决定,Rdrv由驱动IC决定,所以一般是选择合适的Rg来平衡该Vgs bouncing电压。

2. 选择Crss/Ciss(即Cgd/Cgs)低的MOSFET有助于降低Vgs尖峰电压值。或者在MOSFET栅源之间并上一个电容,也会吸收dV/dt产生的漏删电流。图15是在下管的GS两端并联5.5nF电容后的开关波形,可以看到电压明显降低,由图11中的3.1V降低到1.7V,大大降低了上下管贯通的风险。

图15. 下管GS并上5.5nF电容的波形

同理,上管关断至米勒平台结束时,下管开通前,桥臂中点电压由VDD降为0,MOSFET的源极和漏极之间产生陡峭的的dV/dt。由此就会在栅极上面产生一个负压。

同时,由图11,图12,可以观察到,下管开通关断过程中,都没有出现米勒平台现象。这是因为在其开通关断时,由于Motor中的电流经过下管的体二极管续流,DS两端电压很小,所以米勒平台也就形成不了了。