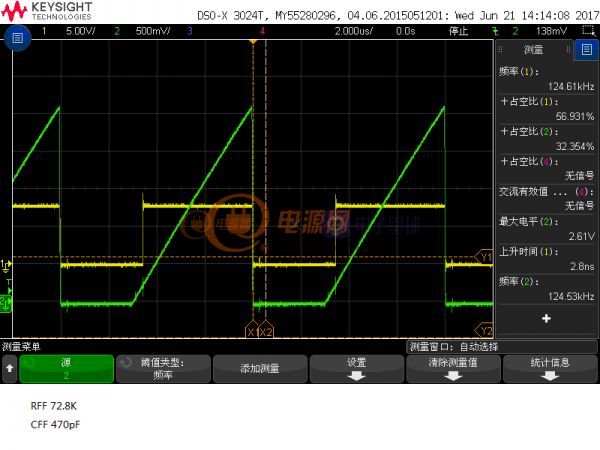

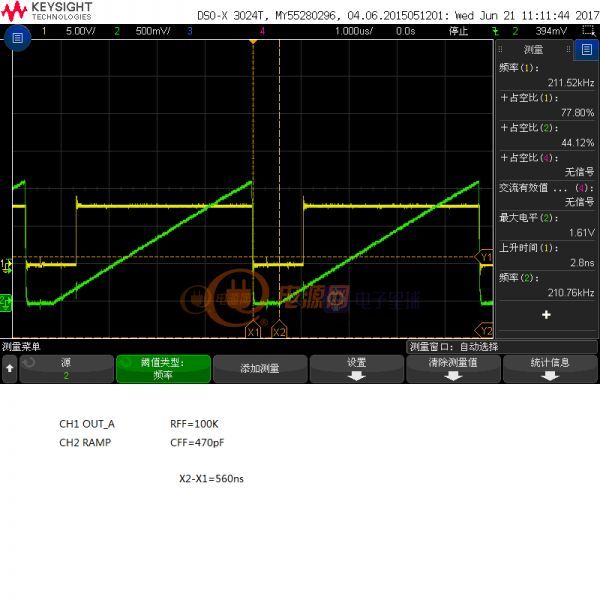

解释:RFF选得太小,Vramp上升到2.5V,RAMP脚复位,占空比上不去,只有42.594%

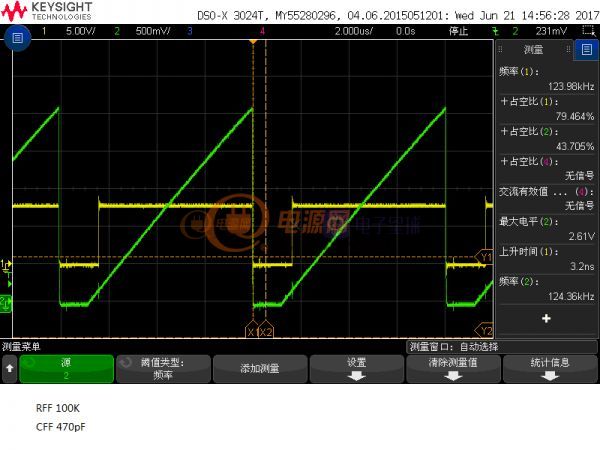

解释:如果把RFF减小到100K至120K某个值,使Vramp可以上升到2.5V临界态,但是估计离91%还是差不少

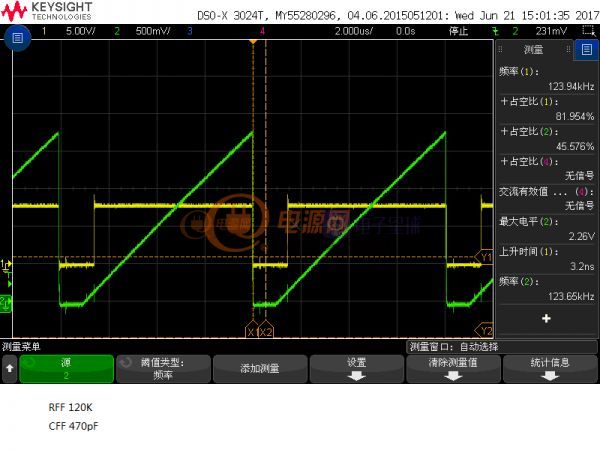

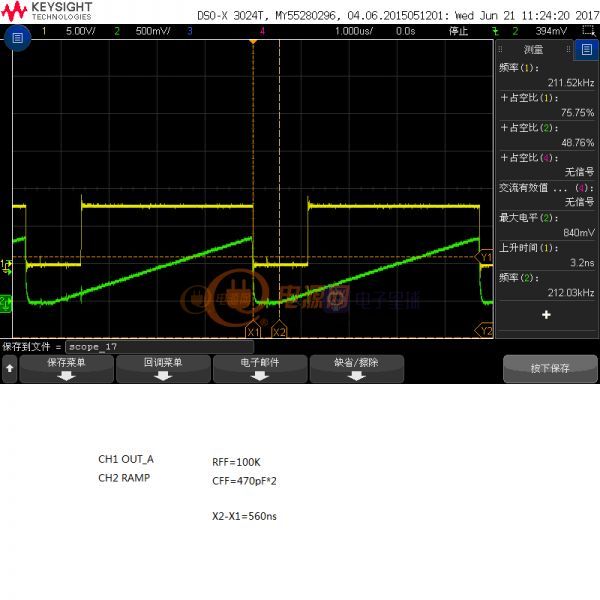

解释:RFF进一步增大,占空比反而减小,初步估计可能是斜坡电压必须高于某个阈值M(0.2V左右),OUTA才能输出高电平。但是

随着RFF增大,斜坡上升速度变慢,导致斜坡电压从0上升到阈值M的时间增加,导致关断时间增加,从而引起占空比下降。

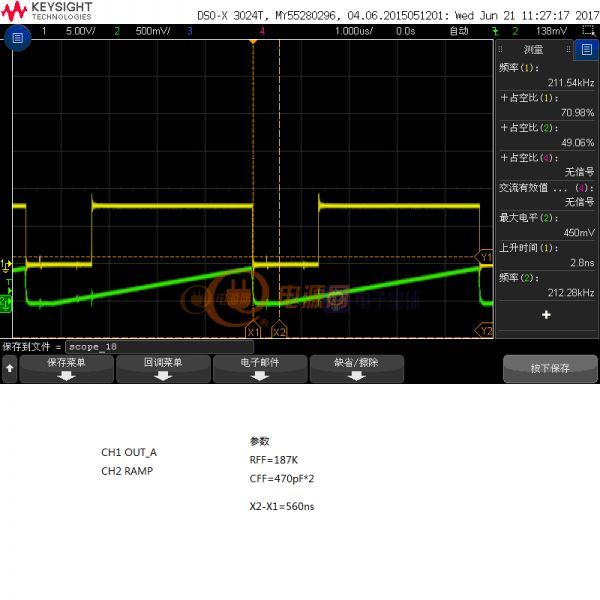

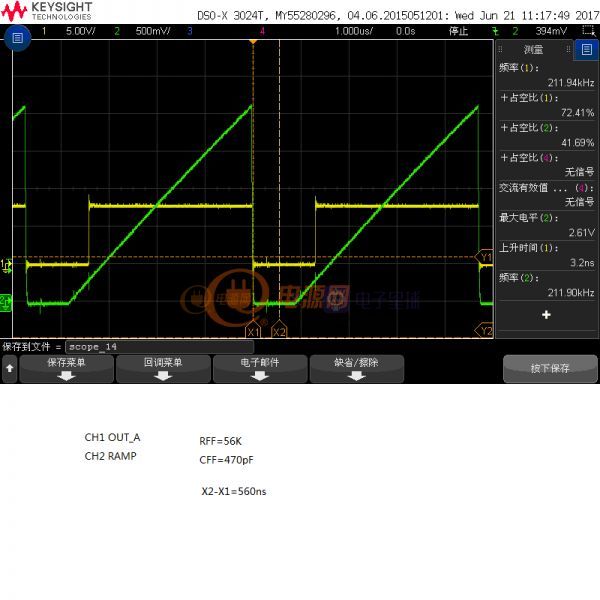

解释:先测试的是200KHz的频率,发现占空比上不去后,仔细观察RAMP和OUT_A的波形后,认为可能有个固定的死区,如果把频率降下去点,也许占空比就上去了。但是测试发现,频率下降,死区时间也变长...