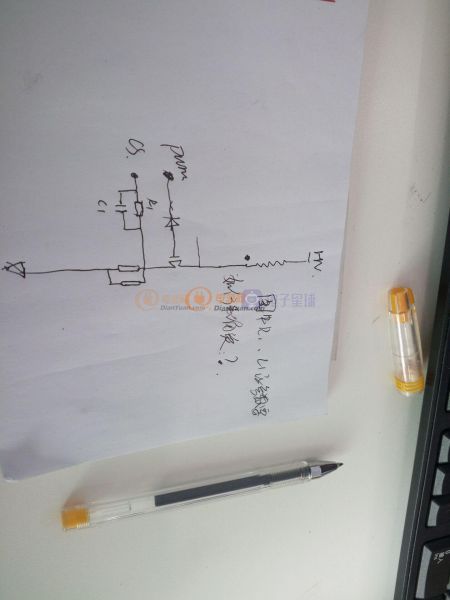

例图是一个普通的PSR控制端口的RCS脚和IC的CS脚之间的抗雷击电路!非常的简单;只是一个RC并联分流电路!在这次的聊天中:希望能有更多的大神过来讲解这两个参数值的定义和取值该当如何依据?推导过程又是如何!如果取值不当又会引起什么样子的后果!也同时希望各为路友进来顶起!![]() 未完待续!

未完待续!

PSR原边CS抗雷击(浪涌)电路分析

全部回复(6)

正序查看

倒序查看

现在还没有回复呢,说说你的想法

@越凌科技

大神们 高手们请进啊!顶起来呀!一二一呀···

假设:芯片的CS的阀值为:0.9V ;IPK=1A ; 则对应电源板的RCS是多少? SO,RCS=0.9Ω(介于功率的损耗,随需要三个电阻并联分流例如:3R6Ω/3R6Ω/1R8Ω/ 阻值是不变的! 就上诉条件分析:当芯片的VCC建立后VOUT开始上升,那么IPK也上升并且达到0.9V的阀值后关断(对应实现横流功能CC)那么类似于OB2532A或者SF6771D等等外挂MOS的PSR方案为何会在RCS的信号源和芯片的CS脚之间串并联RC网络呢? 行内人都知道RCS的搭档是RC网络旁路掉杂波的,(在当下的PSR方案中很少见了,基本都做了内封或者工艺优化了这一弊端)而此时的这个介于RCS和CS之间的CS又是何解? 人呢? 人呢:? 高手们能否帮我纠正一下错误!来个高手讲讲课行不行 啊? 那么多的坛主呢????

0

回复

提示

@越凌科技

假设:芯片的CS的阀值为:0.9V;IPK=1A ; 则对应电源板的RCS是多少?SO,RCS=0.9Ω(介于功率的损耗,随需要三个电阻并联分流例如:3R6Ω/3R6Ω/1R8Ω/阻值是不变的! 就上诉条件分析:当芯片的VCC建立后VOUT开始上升,那么IPK也上升并且达到0.9V的阀值后关断(对应实现横流功能CC)那么类似于OB2532A或者SF6771D等等外挂MOS的PSR方案为何会在RCS的信号源和芯片的CS脚之间串并联RC网络呢?行内人都知道RCS的搭档是RC网络旁路掉杂波的,(在当下的PSR方案中很少见了,基本都做了内封或者工艺优化了这一弊端)而此时的这个介于RCS和CS之间的CS又是何解? 人呢?人呢:? 高手们能否帮我纠正一下错误!来个高手讲讲课行不行啊?那么多的坛主呢????[图片]

阀值0.9V,IPK应该是OCP前的IPK,而不是额定载时的,按你的计算是0.9欧

0

回复

提示