在上一个贴子《MOS的选择》中说到:

“回看近年,随着中国制造业的跨越长进,模式也在慢慢推进,从“模块代工”过度到“整机生产”,从“按图样生产”过度到“国产化设计”,从“周边元件国产化”过度到“核心器件国产化”。这也是进步的规律。

作为MOS的设计生产商,一方面欣喜地看到在一些如LED、适配器、电动车等等应用领域,国产器件慢慢受到认可;另一方面也看到在很多的应用场合国产 MOS倍受冷遇。希望可以通过应用推广和使用讲解,尽可能地让工程师们认识到国产MOS器件已经迎头赶上,可堪使用了。”

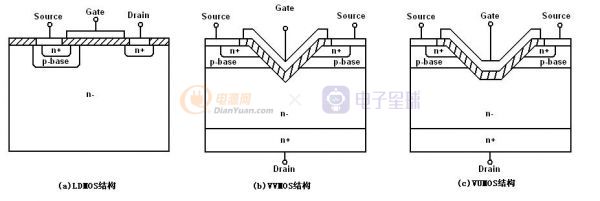

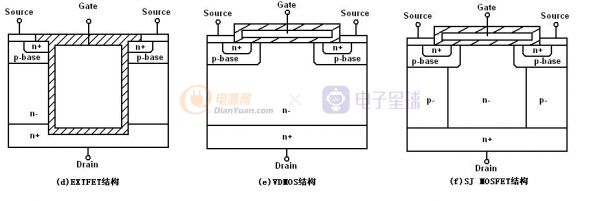

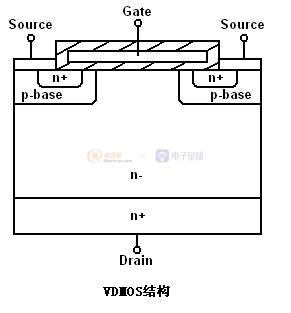

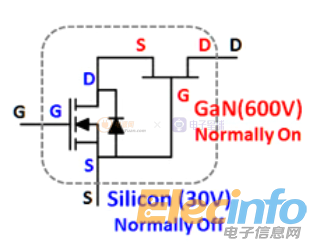

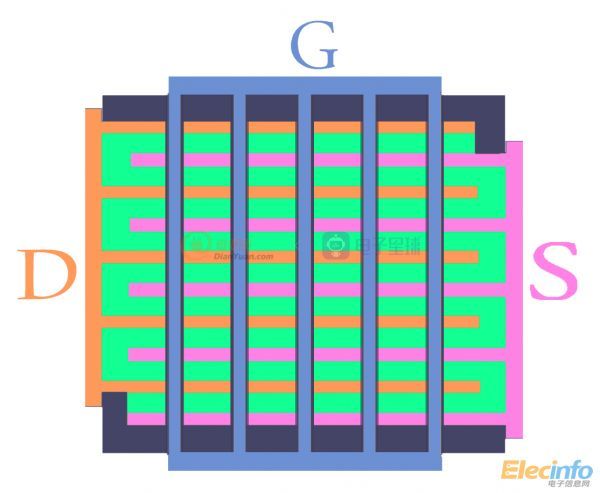

这个贴子准备讲解一下VDMOS的前世今生,VDMOS现在使用得较多较为广泛。希望大家通过更深入的了解,清楚国内与国外的技术差距,明白国内器件所处的水平,更有利推动国产MOS器件的推广使用。

先起个头,慢慢加。

如对芯片尺寸、选择BV、Rds、Qg等参数平衡点、封装的考虑方向等问题感兴趣,请积极发表见解,