各位大师

下午好

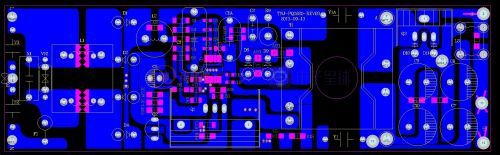

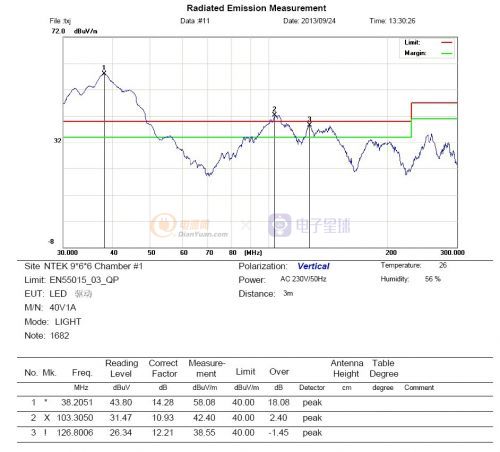

本人用原边PSR方案设计了一款输出40V1A的LED外置电源,测试EMI传导已经过呢,辐射差的要命,驱动电阻现在是100R,DS加了电容100PF,输出加了共模600UH,无改善,下面请看图.PCB

首先非常感谢11贴的细心回复:

第一点大功率回路太大,这点后续可以稍微改善一些,但是大家都知道,小不到哪里去了,

第二点:R13,R14是调节输出电流的,这个面积大,应该是好一些的.

第三点:不该画大的地方,您如果是指地线的话,地线应该是面积越大越好的.

第四点:Y电容不要服铜,这个问题,我在改板的时候有试过,效果没有显著的区别存在.

第五点:输出共模的线走到其他地方去了,这点,我很认可,后续画板一定注意,

第六点:MOS的DS端并接电容,MOS的温升自然会高,但是实际这个电源考箱50度的环温,变压器没有超过90度(电容用的不大,100PF)符合UL标准,楼主说加RC,把热量分到电组,这点我还没有见过这样的搞法,这样的话,电阻取多大,?

我会吸取楼主的建议,套磁株.换慢管,改板等实在过不去, 才能改.谢谢

是整灯测试还是单独测试的驱动,注意整灯测试的时候灯具一定要接地!

PCB画得太差了,输出没经过电容直接就出去了,四个电解没起到什么作用,输入环路面积太大,你看你的初级控制电路,整个就被大电流环路包围,干扰不大才怪。重新布局吧。

请教下大功率回路面积大,我看了下,VCC好像只可以这样了吧,还请指教该如何布线