小弟今年大二结束,之前一直在学习单片机与FPGA,暑假无聊刚接触逆变,有愚拙之处敬请指出。(之所以用FPGA而不用专业的SPWM驱动芯片是因为最终的项目要实现0.1°移相、0.01HZ调频功能及其他扩展功能。(比如可能要用FPGA做光伏并网的相位、频率跟踪)这些是其它芯片所做不到的。)

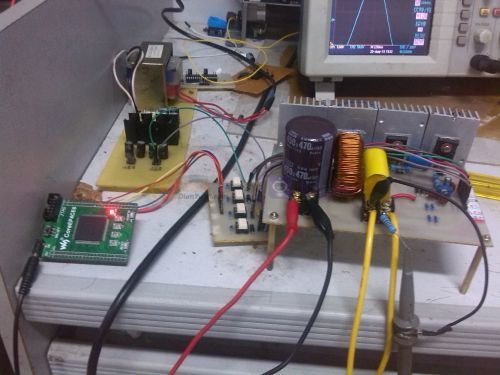

这个基于FPGA的逆变器最终是要做成三相、六路的"三相工频测试源",三路恒流、三路恒压,(直接市电整流滤波供电)。且电压、电流幅值、相位、频率均可调。 目前先把单相的给大家展示一下、原理都一样。(三相的也还没完成呢,主要是H桥的驱动还是有点问题,想请大家帮下下忙,问题解决完毕后我将像老寿一样公布 所有技术资料)

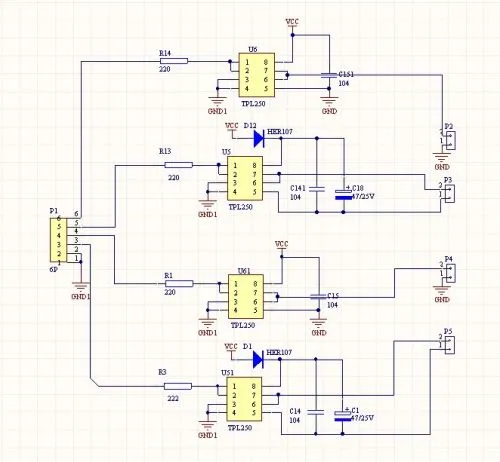

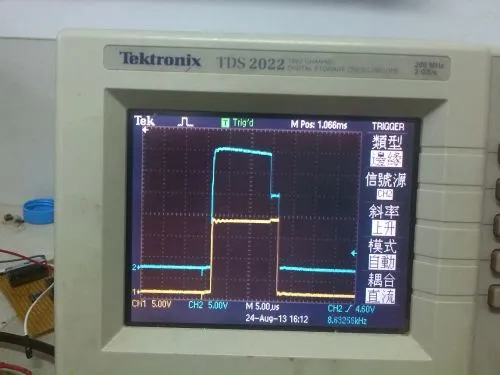

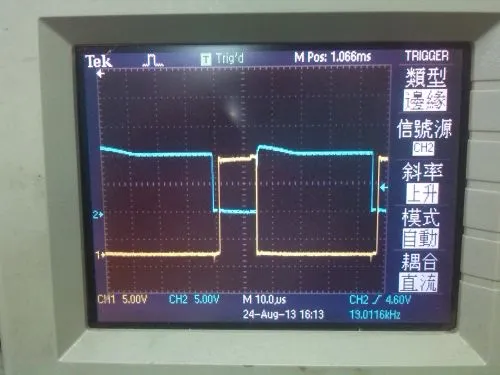

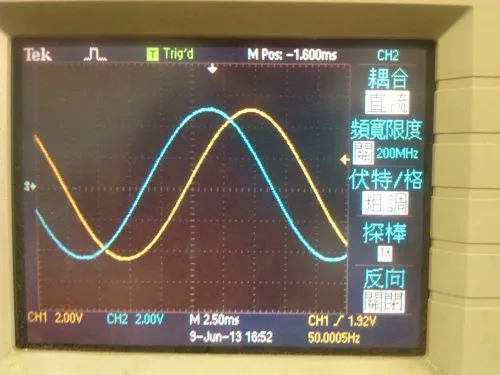

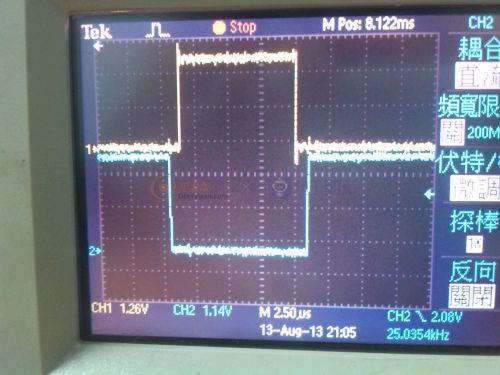

上图为FPGA输出SPWM波形图,为单极性调制。逻辑控制与延时是在FPGA内部做的。输出四路SPWM直接接上IR2110或TLP250,即可驱动后级H桥。

上图为FPGA输出SPWM波形图,为单极性调制。逻辑控制与延时是在FPGA内部做的。输出四路SPWM直接接上IR2110或TLP250,即可驱动后级H桥。

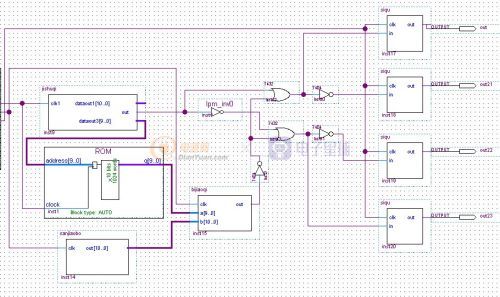

下图为FPGA生成SPWM的结构图(单相的,是用那种四个管子都一半高频、一半低频的方式调制)。

原理跟纯硬件的差不多,就是将正弦波、三角波的数据先生成好放到ROM中,用两路驱动信号分别驱动两个模块,再把输出数据进行比较就生成的SPWM了。三角波和正弦波的频率、幅值都可以很好的控制。

上图只是说明一下FPGA产生SPWM的原理,调频模块直接用锁相环替代。逻辑控制调用非门与或门,死区用程序写的,想要多少设置多少。

上图只是说明一下FPGA产生SPWM的原理,调频模块直接用锁相环替代。逻辑控制调用非门与或门,死区用程序写的,想要多少设置多少。

空载波形:

带载300W波形:(波形还不错,就是散热片有点小,发热有点大,不敢再加了,且发热不均。左上管发热最严重,80度左右,右下管几乎温的。目前此问题还没有解决。)输出250V,由于示波器探头只有10倍衰减档位所以只能看一半了。