【10周年】用simplis验证环路理论(四)

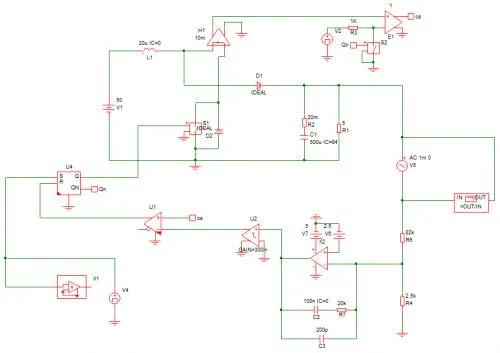

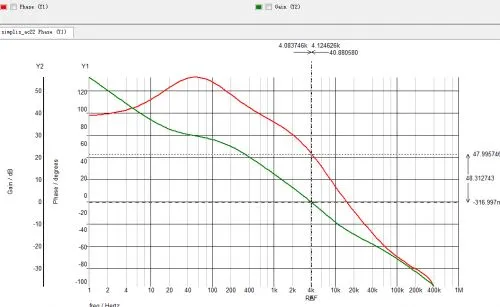

在这个帖子里,我们来看真正的闭环仿真,以及如何借助仿真工具来设计环路补偿。

全部回复(44)

正序查看

倒序查看

现在还没有回复呢,说说你的想法

@sometimes

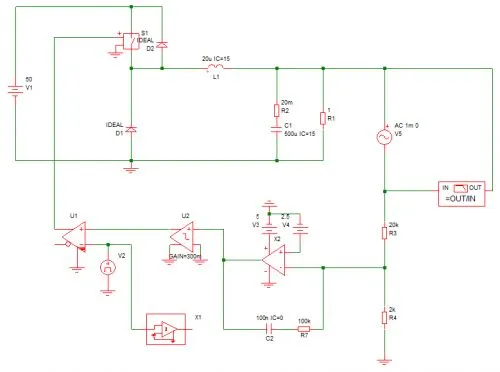

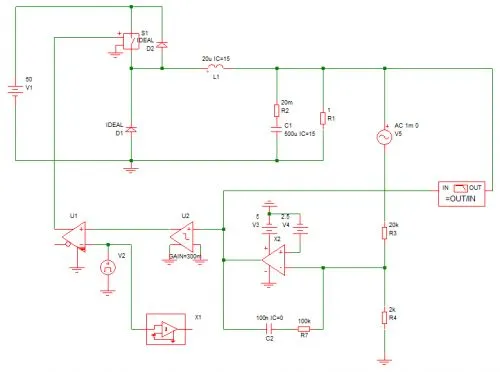

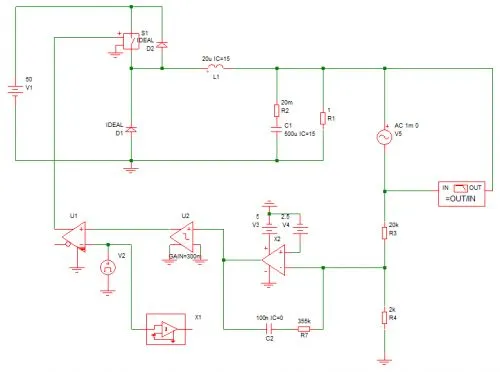

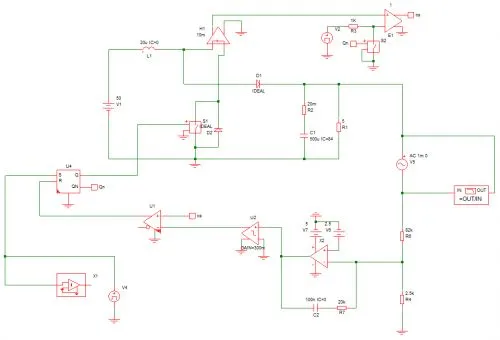

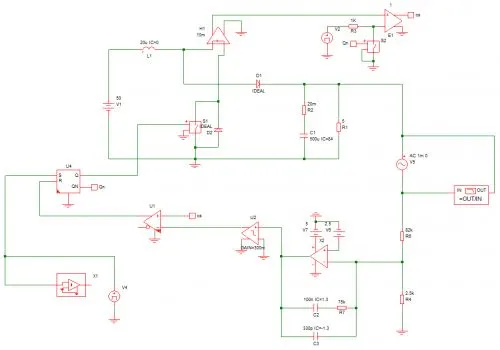

得知这些信息之后,我们就要开始设计反馈参数了。首先:我们要确定采样电阻的大小(R3,R4)第一步,确定R3,R4的比例,这个容易,根据基准电压和输出电压,很容易就能得到。第二步,确定R3,R4确切的值,那么先要知道这个运放的输入偏置电流Ibias。知道Ibias之后,你就要保证采样电阻上的电流是Ibias的一千倍以上。这样才能保证Ibias不影响你输出电压的精度。假如这个运放的Ibias最大是1uA,那么采样电阻上的电流应该大于1mA.

那么下一步,就要确定,你期望中的环路波特图。

首先我们需要明确几点:

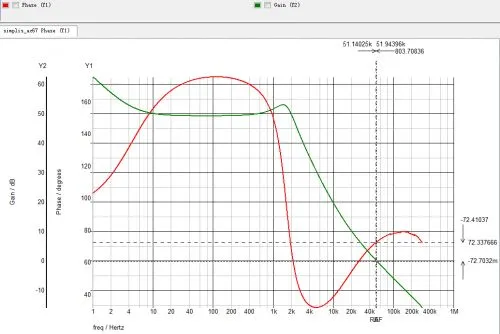

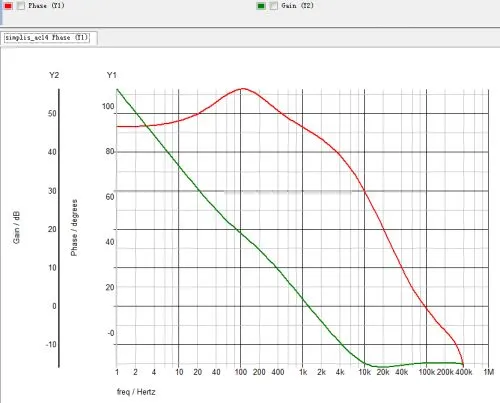

1.开关电源环路的带宽应该选多大?从理论上来说,开关电源的最大带宽可以做到开关频率的1/6-1/3.但是实际上,通常控制在开关频率的1/10之内。在这个例子里,开关频率是500Khz,那么我们把带宽控制在50KHz之内。

2.环路的主要稳定判据?环路的稳定判据为,在增益0db处,相位余量要超过45度。如果简单的从增益曲线来判断,就是要求增益曲线穿越0db线的时候,以单极点特性(20db/10倍频)曲线穿过。而且如果接下去高频处还有极点的话,这个极点应该高于带宽频率10倍以上。

0

回复

提示

@sometimes

那么下一步,就要确定,你期望中的环路波特图。首先我们需要明确几点:1.开关电源环路的带宽应该选多大?从理论上来说,开关电源的最大带宽可以做到开关频率的1/6-1/3.但是实际上,通常控制在开关频率的1/10之内。在这个例子里,开关频率是500Khz,那么我们把带宽控制在50KHz之内。2.环路的主要稳定判据?环路的稳定判据为,在增益0db处,相位余量要超过45度。如果简单的从增益曲线来判断,就是要求增益曲线穿越0db线的时候,以单极点特性(20db/10倍频)曲线穿过。而且如果接下去高频处还有极点的话,这个极点应该高于带宽频率10倍以上。

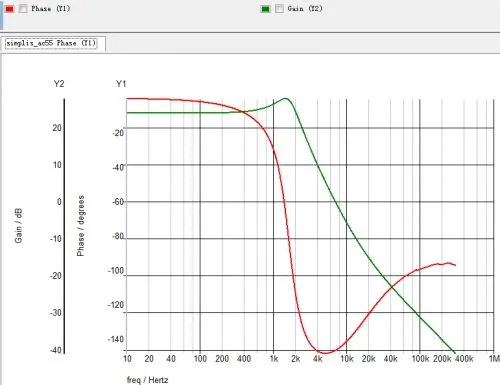

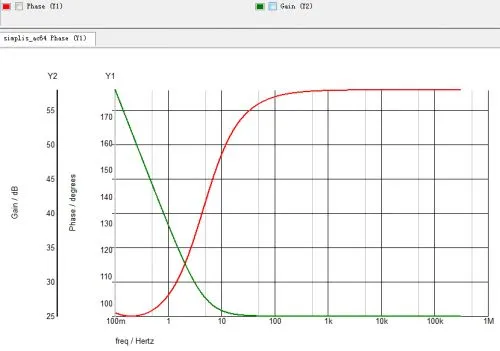

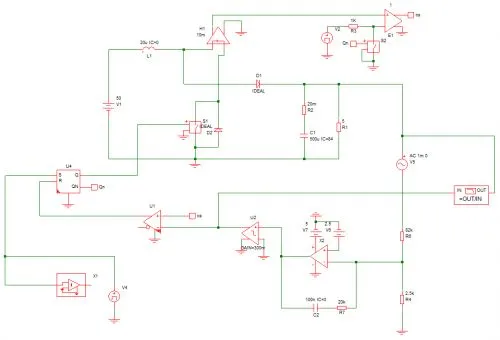

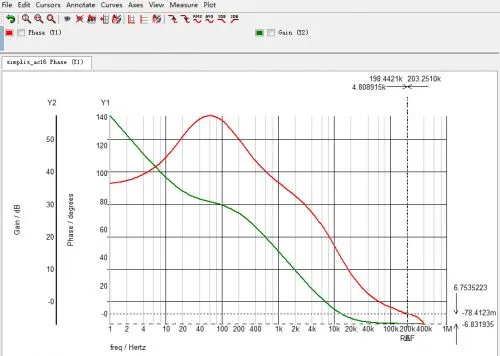

我们看上面的bode图,可以发现,从16Khz之后,该bode图增益曲线就是单极点特性了。

而且可以看到,在50Khz处,该增益大概为-25db。

那么如果,我们把这个增益曲线整体上抬25db,理论上来说,穿越频率就会在50Khz,而且是以单极点特性穿越的。

0

回复

提示

@sometimes

我们看上面的bode图,可以发现,从16Khz之后,该bode图增益曲线就是单极点特性了。而且可以看到,在50Khz处,该增益大概为-25db。那么如果,我们把这个增益曲线整体上抬25db,理论上来说,穿越频率就会在50Khz,而且是以单极点特性穿越的。

接下去,我们就要来设计环路补偿来符合上面的思路。

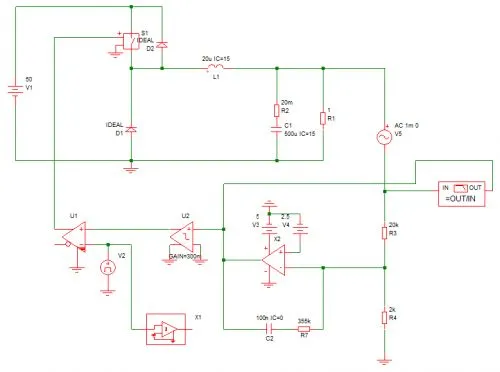

按照上面的原理图,我们采用一个简单的RC补偿,也即是有一个零极点,一个零点。

假如我们选这个零点处于低频处,来抵消这个零极点。

这里先选C2=100nF

接下去确定补偿带来的增益平台,也就是R7/R3,上面我们说到,这个增益平台需要25db,也就是17.88.那么如果R3是20K,R7就要选356K。

那么可以的根据C2,R7得到那个零点为4.5Hz

0

回复

提示